# Operation, Control and Stability Analysis of Multi-Terminal VSC-HVDC Systems

A thesis submitted to The University of Manchester for the degree of

Doctor of Philosophy

in the Faculty of Engineering and Physical Sciences

2015

Wenyuan Wang

School of Electrical and Electronic Engineering

## **Table of Contents**

| Table of Co   | ntents                                         | 2  |

|---------------|------------------------------------------------|----|

| List of Figur | res                                            | 6  |

| List of Table | es                                             | 13 |

| Nomenclatu    | re                                             | 15 |

| Abstract      |                                                | 23 |

| Declaration   |                                                | 24 |

| Copyright S   | tatement                                       | 25 |

| Acknowledg    | gements                                        | 26 |

| Chapter 1     | Introduction                                   | 27 |

| 1.1 Ba        | ckground                                       | 27 |

| 1.2 Up        | -to-date VSC-HVDC Technology                   | 28 |

| 1.3 Mu        | Ilti-Terminal VSC-HVDC                         | 29 |

| 1.4 Pro       | pject Objectives                               | 32 |

| 1.5 Ma        | in Contributions of the Thesis                 | 32 |

| 1.6 Ou        | tline of the Thesis                            | 34 |

| 1.7 Lis       | t of Publications                              | 36 |

| Chapter 2     | Modelling and Control of MTDC                  | 37 |

| 2.1 Mo        | delling and Control of Grid Side VSC-HVDC      | 37 |

| 2.1.1         | Overview of GSC Control                        |    |

| 2.1.2         | Average-Value Model (AVM)                      |    |

| 2.1.3         | Vector Current Control                         | 43 |

| 2.1.4         | Phase-Locked Loop                              | 49 |

| 2.1.5         | Active and Reactive Power Control              | 51 |

| 2.1.6         | Current Limit                                  | 54 |

| 2.1.7         | AC Voltage Control                             | 55 |

| 2.1.8         | Frequency Control and Damping Support          | 57 |

| 2.2 Mo        | odelling of Wind Farm and Offshore VSC Control | 58 |

| 2.2.1         | Modelling of WFC Control                       | 58 |

| 2.2.2         | Modelling of Simplified Wind Farm (SWF)        | 59 |

| 2.2.3         | Fault Ride-Through Control                     | 59 |

| 2.2.4         | Modelling of DC Cable                          | 62 |

| 2.3 DC        | C Voltage Control of MTDC                      |    |

| 2.3.1         | DC Slack Bus Control                           | 64 |

| 2.3.2         | Voltage Margin Control                         | 70 |

| 2.3.3         | DC Voltage Droop Control                       | 73 |

| 2.3     | 3.4 | Voltage Droop Control with Deadband                 | 75  |

|---------|-----|-----------------------------------------------------|-----|

| 2.3     | 3.5 | Control Comparison                                  | 76  |

| 2.4     | Ch  | apter Summary                                       | 82  |

| Chapter | : 3 | Steady-State Analysis of MTDC                       |     |

| 3.1     | Pov | wer Flow Algorithms for MTDC                        | 83  |

| 3.1     | l.1 | Integration of AC/DC Power Flow                     | 84  |

| 3.1     | 1.2 | Power Flow of MTDC with a Slack Bus                 | 86  |

| 3.1     | 1.3 | Power Flow of MTDC with Droop Control               |     |

| 3.1     | 1.4 | Power Flow with Generalised V-P/V-I Characteristics | 91  |

| 3.1     | 1.5 | Case Studies and Simulations                        | 94  |

| 3.2     | VS  | C Transmission Limit                                | 101 |

| 3.3     | Lin | ear Analysis and Equivalent Circuit                 | 105 |

| 3.3     | 3.1 | Voltage-Current Droop                               | 105 |

| 3.3     | 3.2 | Voltage-Power Droop                                 | 106 |

| 3.3     | 3.3 | Steady-state Equivalent Circuit for Droop Control   | 109 |

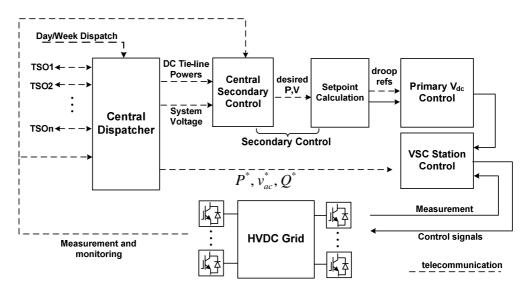

| 3.4     | Sec | condary Control and DC Dispatch                     | 112 |

| 3.4     | 4.1 | Control Structure Description                       | 112 |

| 3.4     | 4.2 | Setpoint Calculation                                | 114 |

| 3.5     | Ch  | apter Summary                                       | 117 |

| Chapter | r 4 | Analysis of Active Power Control of VSC-HVDC        | 118 |

| 4.1     | Tw  | o Types of Controllers                              | 119 |

| 4.1     | l.1 | More Detailed Current Loop                          | 119 |

| 4.1     | 1.2 | Models for Feedforward and Feedback Power Control   | 121 |

| 4.1     | 1.3 | Stability Criterions of the Active Power Control    |     |

| 4.1     | l.4 | Impact on the Voltage Droop Control                 | 125 |

| 4.2     | Fre | equency-Response Analysis and Simulations           | 127 |

| 4.2     | 2.1 | Impact of Controller Bandwidth                      | 127 |

| 4.2     | 2.2 | Sensitivity Analysis                                | 129 |

| 4.2     | 2.3 | Simulations of SISO Droop Control                   |     |

| 4.3     | Sin | nulations Studies Using a Four-Terminal Model       | 134 |

| 4.4     | Ch  | apter Summary                                       | 136 |

| Chapter | : 5 | Small-Signal Modelling of VSC-MTDC                  | 137 |

| 5.1     | Mo  | odelling of Grid Side Converter (GSC)               | 138 |

| 5.1     | l.1 | Modelling of AC Side Dynamics and PLL               | 138 |

| 5.1     | 1.2 | Modelling of the DC Side Dynamics                   | 140 |

| 5.1     | 1.3 | Modelling of Current Control                        | 140 |

| 5.1     | 1.4 | Modelling of Outer Control Loops                    | 141 |

| 5.1     | 1.5 | Integration of Sub-Systems for GSC                  | 142 |

|         |     |                                                     | 3   |

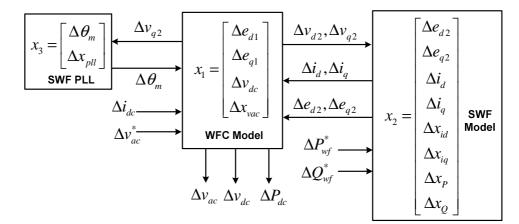

| 5.2     | Mo  | odelling of Wind Farm Side Converter Terminal                  | 143   |

|---------|-----|----------------------------------------------------------------|-------|

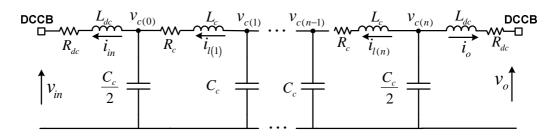

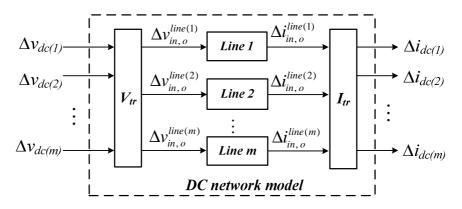

| 5.3     | DC  | C Network Modelling                                            | 146   |

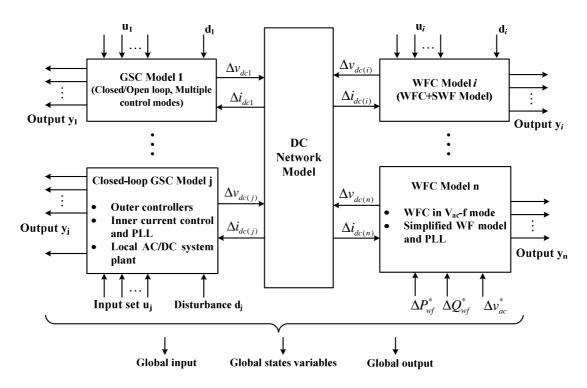

| 5.4     | Mo  | odel Interconnection for MTDC Systems                          | 148   |

| 5.5     | Mo  | odal Analysis                                                  | 150   |

| 5.6     | Ch  | apter Summary                                                  | 157   |

| Chapter | 6   | Stability Analysis of DC Voltage Control of VSC-HVDC           | 158   |

| 6.1     | Ke  | y Dynamic Limitations for DC Voltage Control                   | 159   |

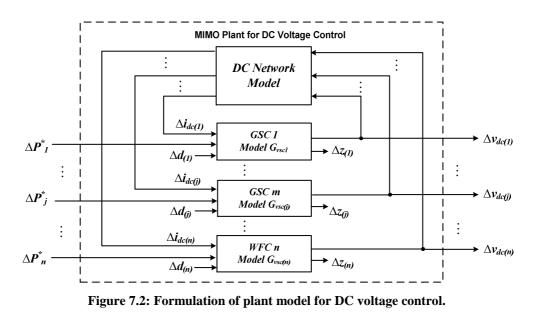

| 6.1     | .1  | Formulation of the Plant Model                                 | 159   |

| 6.1     | .2  | Constraints Imposed by Weak AC System                          | 160   |

| 6.1     | .3  | Constraints Imposed by Power Operating Point (OP)              | 162   |

| 6.1     | .4  | Constraints Imposed by Other Control Loops                     | 165   |

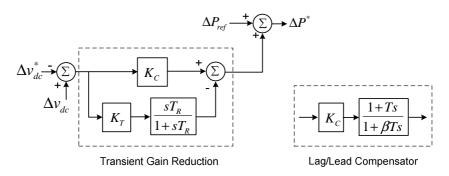

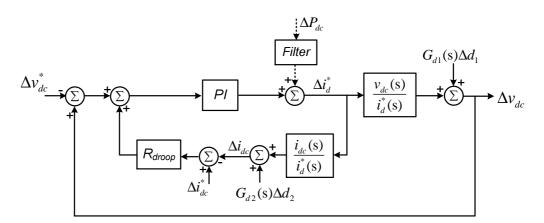

| 6.2     | Dre | oop Control with Transient Compensation                        | 168   |

| 6.2     | 2.1 | Transient Gain Reduction                                       | 168   |

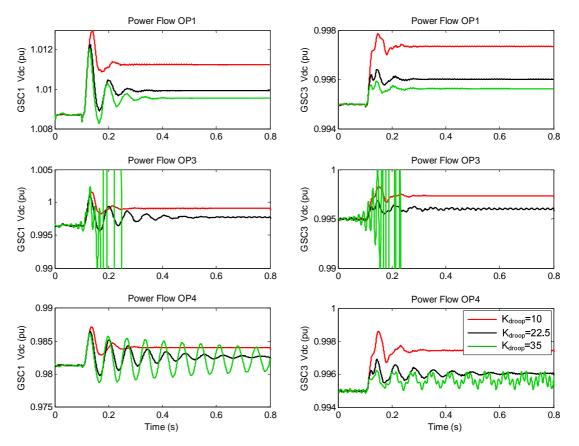

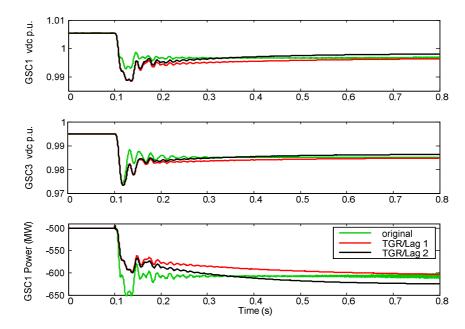

| 6.2     | 2.2 | Time-Domain Simulations                                        | 169   |

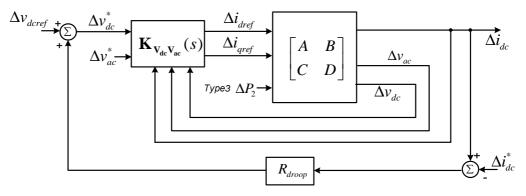

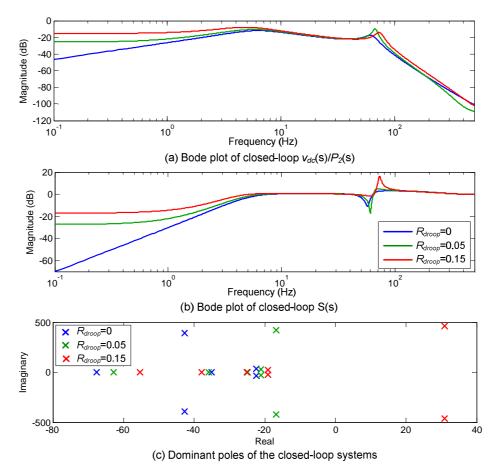

| 6.3     | Sta | bility Analysis of V-I Droop Control                           | 171   |

| 6.4     | Im  | pact of the Feedforward DC Current                             | 176   |

| 6.5     | Ch  | apter Summary                                                  | 180   |

| Chapter | 7   | Impact of DC Reactor on MTDC Stability and Damping Enhancement | nt181 |

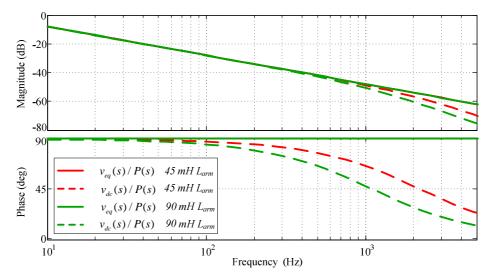

| 7.1     | Sta | bility Issues Caused by DC Reactor                             | 182   |

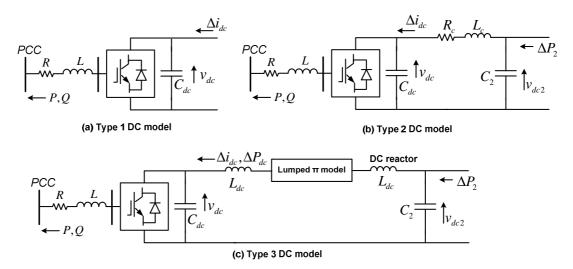

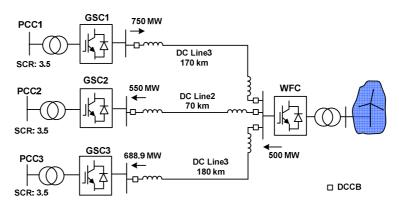

| 7.1     | .1  | Description of Analytical Models                               | 182   |

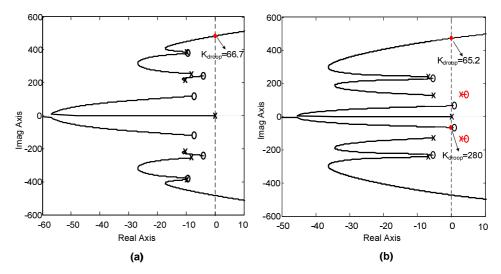

| 7.1     | .2  | Stability and Controllability Issues                           | 184   |

| 7.1     | .3  | Dynamic Performance Issues                                     | 187   |

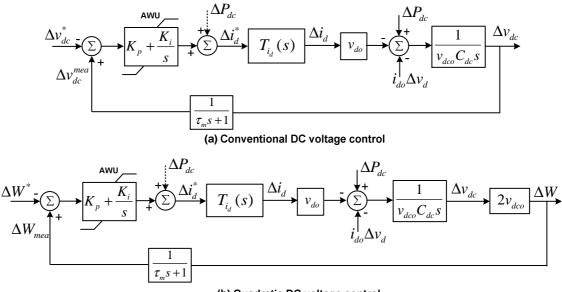

| 7.2     | DC  | C Voltage Damping Controller (DCPSS)                           | 191   |

| 7.2     | 2.1 | Location Selection and Control Design                          | 191   |

| 7.2     | 2.2 | Test of Damping Controllers                                    | 194   |

| 7.3     | Ac  | tive Stabilising Control                                       | 198   |

| 7.3     | 3.1 | Two Stabilising Controllers                                    | 198   |

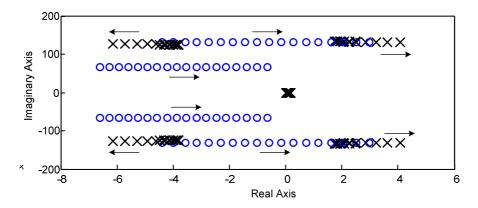

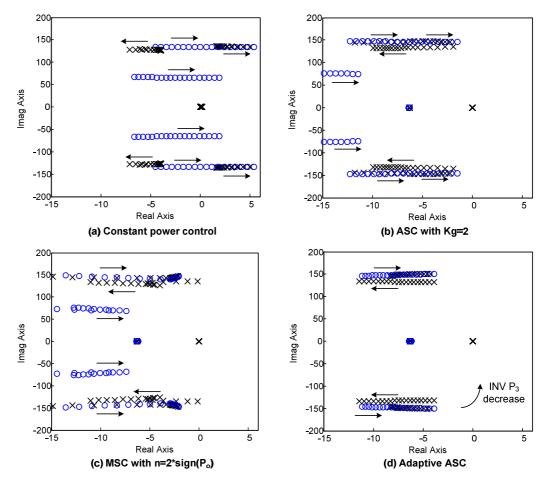

| 7.3     | 3.2 | Analytical Results                                             | 200   |

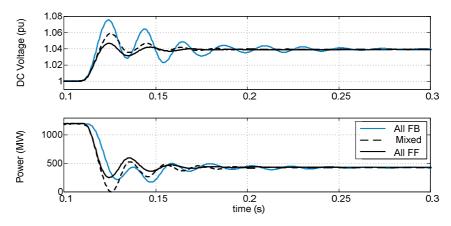

| 7.3     | 3.3 | Simulation Results                                             | 204   |

| 7.4     | Ch  | apter Summary                                                  | 208   |

| Chapter | 8   | Conclusion and Future Work                                     | 209   |

| 8.1     | Co  | nclusion                                                       | 209   |

| 8.1     | .1  | Modelling and Control of MTDC                                  | 209   |

| 8.1     | .2  | Steady-State Analysis of MTDC                                  | 209   |

| 8.1     | .3  | Stability Studies of Active Power and DC Voltage Control       | 210   |

| 8.1     | .4  | MTDC Stability Analysis and Auxiliary Controllers              | 211   |

| 8.2     | Fut | ture Work                                                      | 212   |

| 8.2     | 2.1 | More Realistic MTDC Models                                     | 212   |

| 8.2.2      | Coordinated MTDC Control                                    | 213 |

|------------|-------------------------------------------------------------|-----|

| 8.2.3      | Assessment of Droop Control Implementations                 |     |

| References |                                                             |     |

| Appendix A | Modelling of MTDC Systems                                   | 225 |

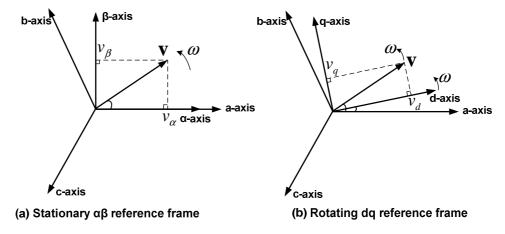

| A.1 Clarl  | and Park Transformations                                    | 225 |

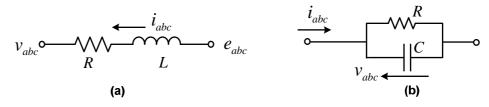

| A.2 Diffe  | rential Equations in DQ Domain                              |     |

| A.3 Justi  | fication of the Use of AVM                                  | 228 |

| A.4 Base   | Values for AC and DC System Parameters                      |     |

| A.5 VSC    | -HVDC System Parameters                                     | 232 |

| Appendix E | Power Flow Calculation                                      | 236 |

| B.1 Loss   | Calculation Parameters                                      | 236 |

| B.2 Inter  | or Point Method for Optimisation                            | 238 |

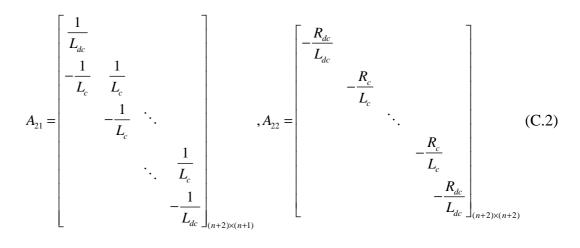

| Appendix C | State-Space Modelling of MTDC                               | 239 |

| C.1 State  | -Space Modelling of DC Lines                                |     |

| C.2 State  | -Space Representation of GSC Terminal                       | 240 |

| C.3 Conr   | ections of the Models of VSC, PLL and Lumped AC System      | 244 |

| C.4 State  | -Space Modelling of WFC Terminal                            | 246 |

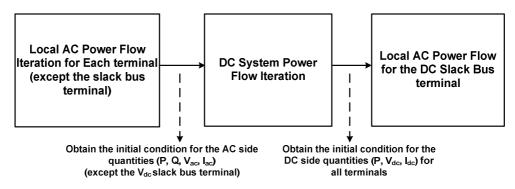

| C.5 Initia | l Condition Calculation                                     |     |

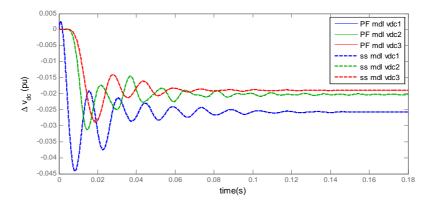

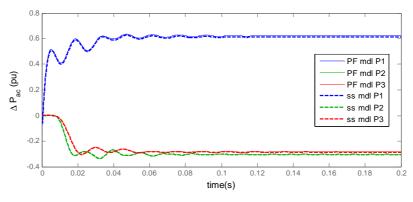

| C.6 Verif  | ication of the Analytical Model of the Four-terminal System | 251 |

| C.7 Selec  | ted Participation Factors                                   | 254 |

| C.8 State  | -Space Type1 GSC Model Used in Chapter 6                    | 256 |

| C.9 Oper   | -Loop State-Space GSC Model Used in Chapter 7               | 257 |

| Appendix I | OAC Fault Studies of MTDC                                   | 258 |

| D.1 Impa   | ct of Inverter Operation                                    | 258 |

| D.2 Impa   | ct of PLL and Reactive Power Control                        |     |

| D.3 Perfe  | ormance of the Adaptive Current Limit                       |     |

|            |                                                             |     |

Word count: 64,642

## **List of Figures**

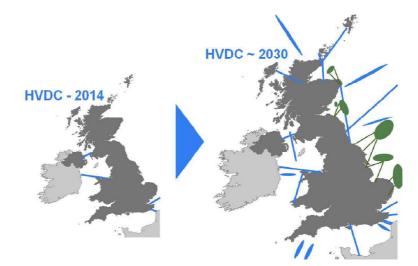

| Figure 1.1: HVDC plans from 2014 until 2030 [6] (based on Electricity Ten Year                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Statement 2013 [7])                                                                                                                                                                                                                                    |

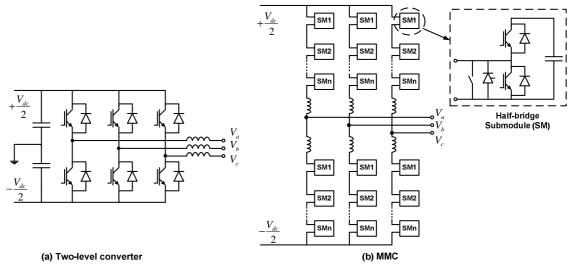

| Figure 1.2: Two-Level and MMC converter topologies                                                                                                                                                                                                     |

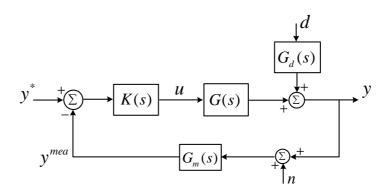

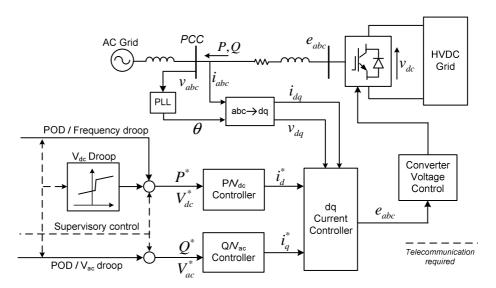

| Figure 2.1: Cascaded control structure for VSC-HVDC                                                                                                                                                                                                    |

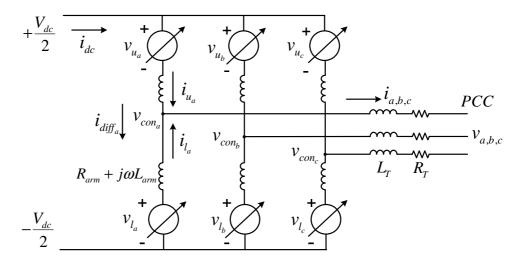

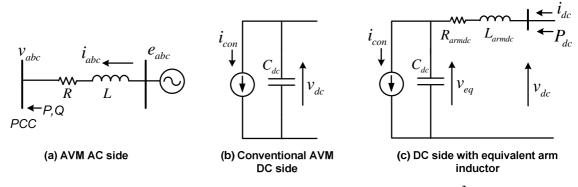

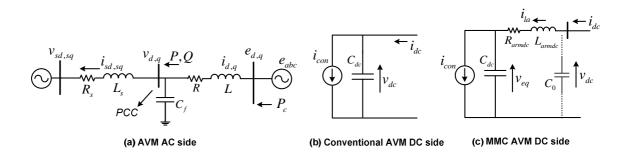

| Figure 2.2: AVM representation of MMC AC side40                                                                                                                                                                                                        |

| Figure 2.3: Single-Line diagram of the AVM model for MMC41                                                                                                                                                                                             |

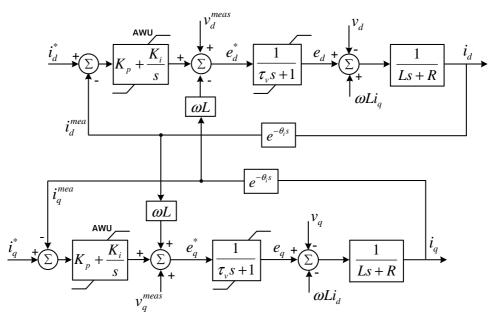

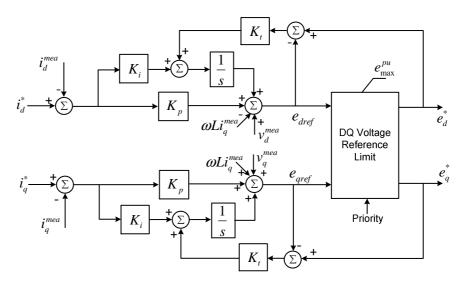

| Figure 2.4: Closed-Loop feedback diagram for dq current control                                                                                                                                                                                        |

| Figure 2.5: Anti-Windup design for the vector current controller45                                                                                                                                                                                     |

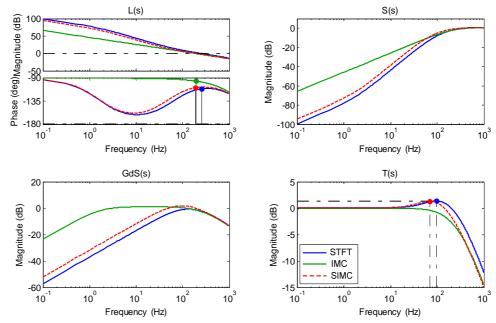

| Figure 2.6: Frequency responses of L(s), S(s), G <sub>d</sub> S(s) and T(s) for the three tuning methods                                                                                                                                               |

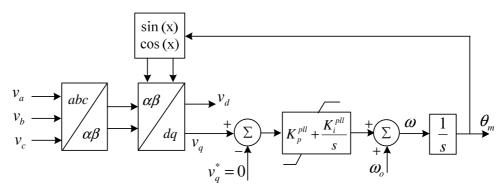

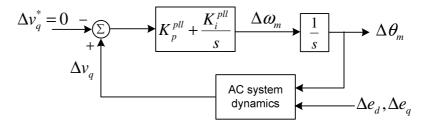

| Figure 2.7: Control diagram for the synchronous reference frame (SRF) PLL50                                                                                                                                                                            |

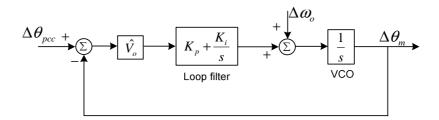

| Figure 2.8: Linearised model for SRF PLL                                                                                                                                                                                                               |

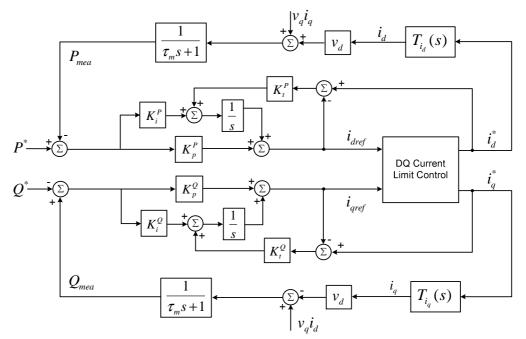

| Figure 2.9: Active and reactive power control system with dynamic anti-wind design52                                                                                                                                                                   |

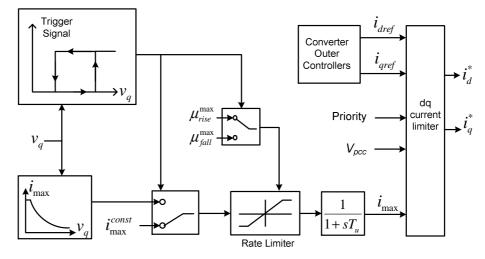

| Figure 2.10: Adaptive current limit control                                                                                                                                                                                                            |

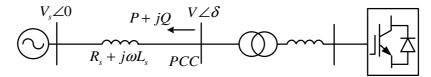

| Figure 2.11: RMS model of a VSC connected to a simplified AC system                                                                                                                                                                                    |

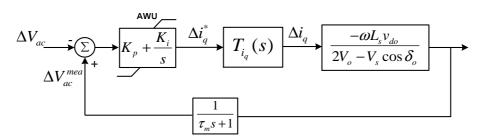

| Figure 2.12: Approximated feedback loop for AC voltage control                                                                                                                                                                                         |

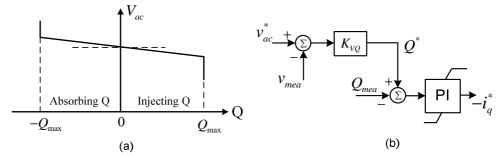

| Figure 2.13: (a) $V_{ac}$ - $Q$ droop characteristics; (b) $V_{ac}$ - $Q$ droop controller                                                                                                                                                             |

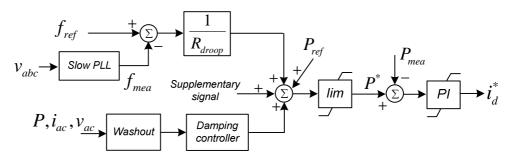

| Figure 2.14: Basic structure of frequency droop control and POD control for VSC-<br>HVDC                                                                                                                                                               |

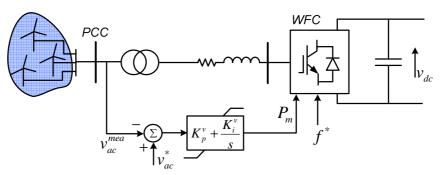

| Figure 2.15: Feedback AC voltage and direct frequency control of WFC                                                                                                                                                                                   |

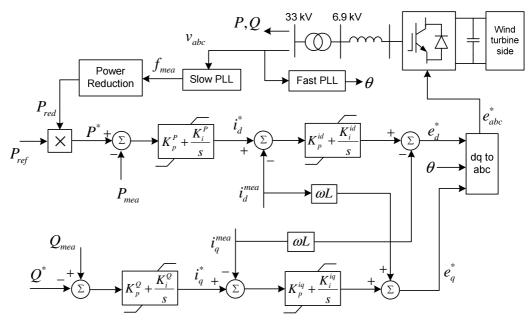

| Figure 2.16: Active and reactive power control of the SWF model                                                                                                                                                                                        |

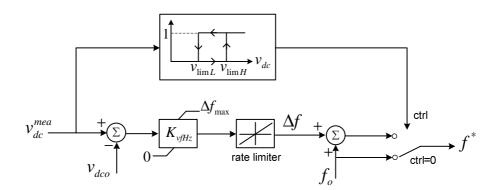

| Figure 2.17: DC overvoltage control of WFC by altering wind farm frequency60                                                                                                                                                                           |

| Figure 2.18: Active power reduction characteristic for the SWF model                                                                                                                                                                                   |

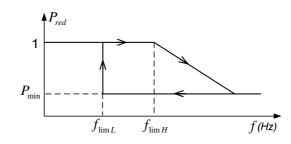

| Figure 2.19: (a) Braking resistor representations of DC chopper; (c) Hysteresis-Based switching control of the braking resistor; (b) Current source representation of DC chopper; (d) Voltage-Current characteristic of the current-source-based model |

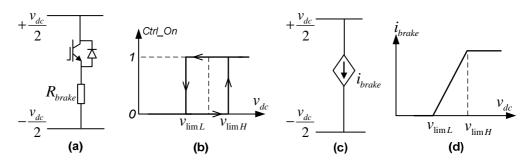

| Figure 2.20: Simulations of FRT control based on DC braking resistor, current-source-<br>based DC chopper and wind power reduction in a point-to-point system                                                                                          |

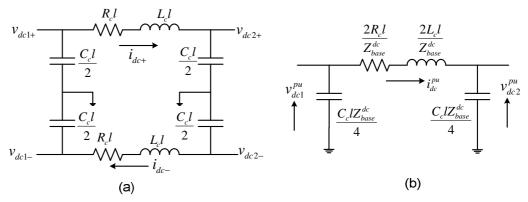

| Figure 2.21: (a) Nominal $\pi$ model of DC cable; (b) per unit representation of the $\pi$ model.                                                                                                                                                      |

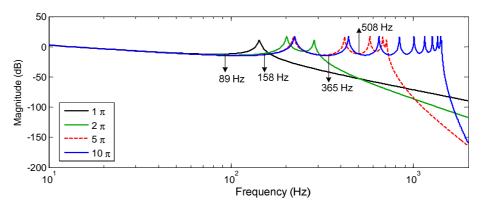

| Figure 2.22: Frequency responses for cable models of different numbers of $\pi$ sections (180 km)                                                                                                                                                      |

| Figure 2.23: Frequency responses of between the converter power and DC voltages measured at two buses                                                                                                                                                  |

| Figure 2.24: Feedback control diagrams for DC voltage control                                                                                                                                                                                          |

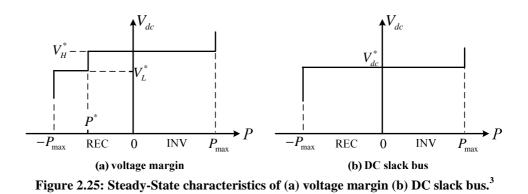

| Figure 2.25: Steady-State characteristics of (a) voltage margin (b) DC slack bus70                                                                                                                                                                     |

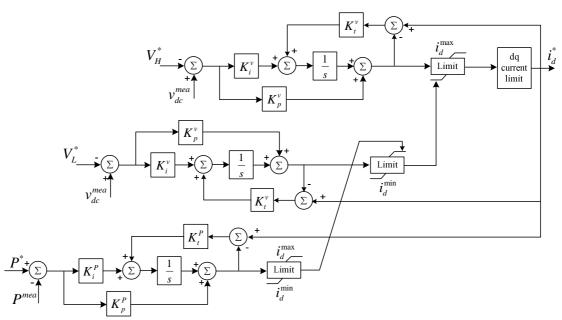

| Figure 2.26: Adaptive-Limit-Based implementation of the voltage margin controller71                                |

|--------------------------------------------------------------------------------------------------------------------|

| Figure 2.27: Hysteresis-Based implementation of the voltage margin controller72                                    |

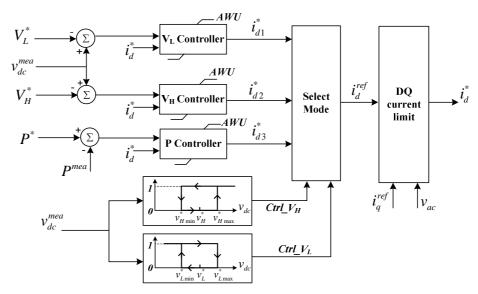

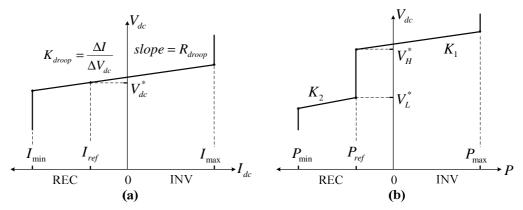

| Figure 2.28: (a) Steady-State voltage-power droop characteristic; (b) Voltage-Power droop controller               |

| Figure 2.29: Steady-State characteristics of (a) voltage-current droop and (b) voltage-power droop with deadband74 |

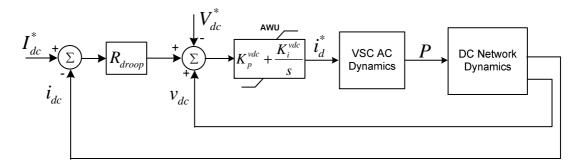

| Figure 2.30: Controller implementation of the voltage-current droop characteristic74                               |

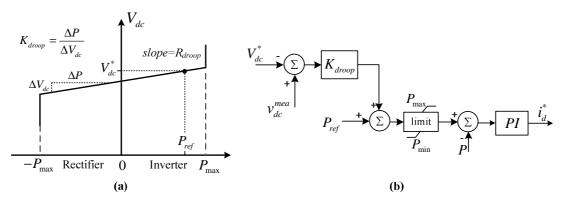

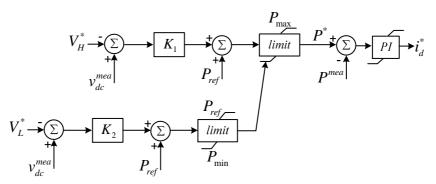

| Figure 2.31: A basic control implementation of V-P droop with deadband75                                           |

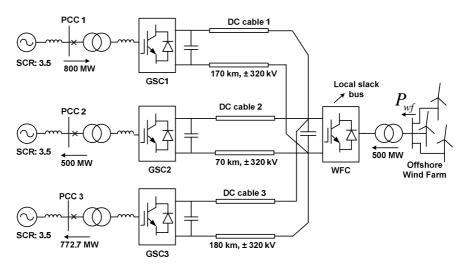

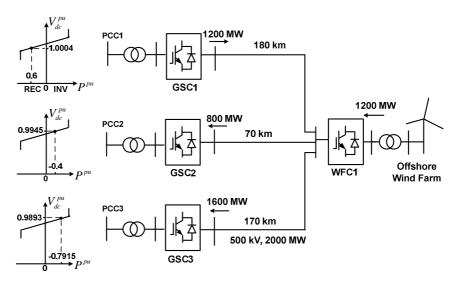

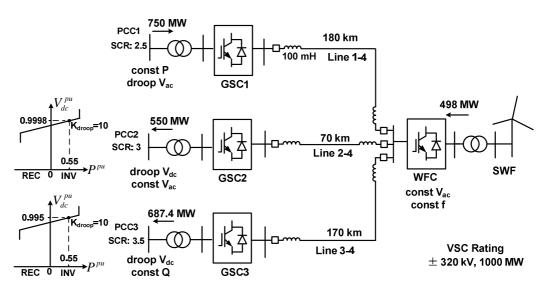

| Figure 2.32: Four-Terminal VSC-HVDC test system                                                                    |

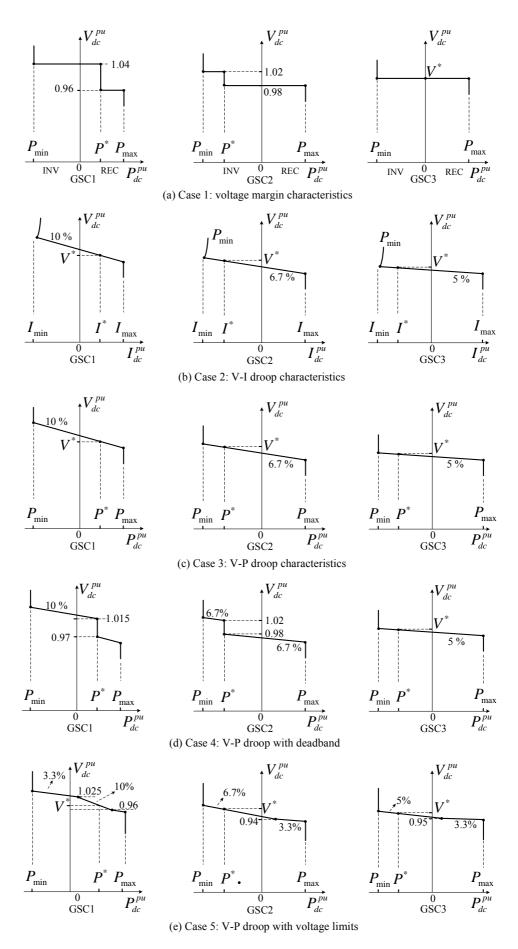

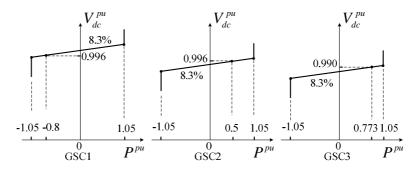

| Figure 2.33: DC voltage characteristics for the three GSCs77                                                       |

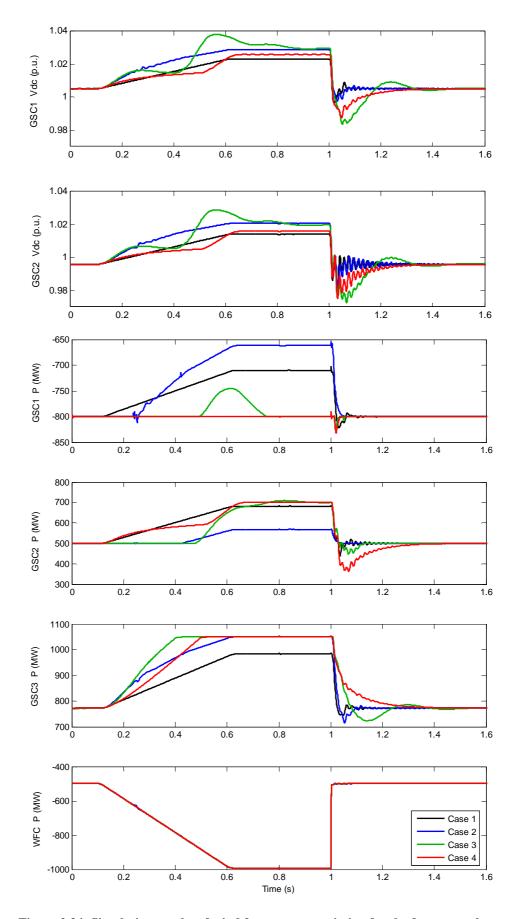

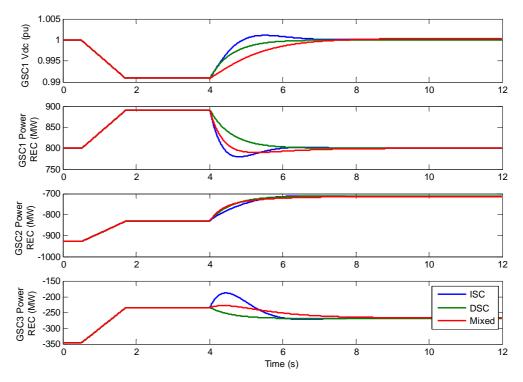

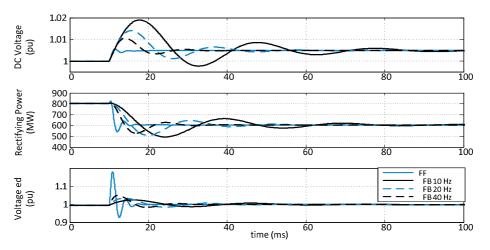

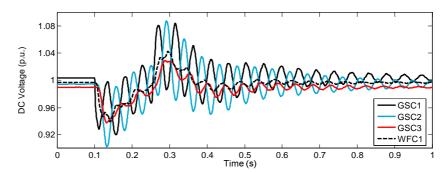

| Figure 2.34: Simulation results of wind farm power variation for the four control cases.                           |

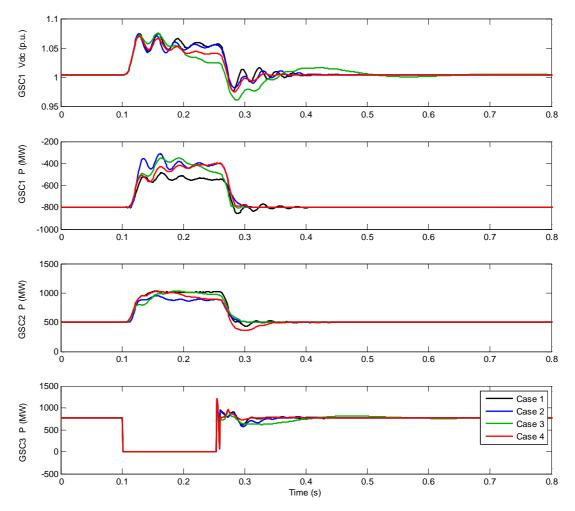

| Figure 2.35: Simulation results of a three-phase fault at PCC3 for the four control cases.                         |

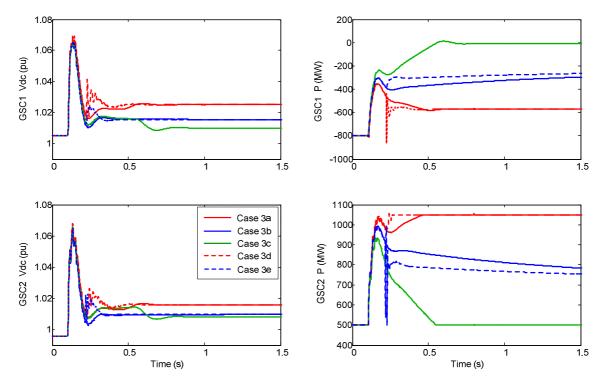

| Figure 2.36: Dynamic responses of GSC1 and GSC2 to the loss of GSC3 for the five voltage margin cases              |

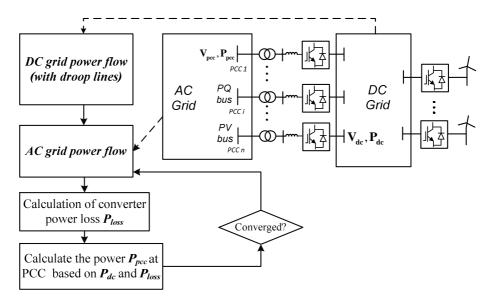

| Figure 3.1: Integration of MTDC power flow with AC power flow                                                      |

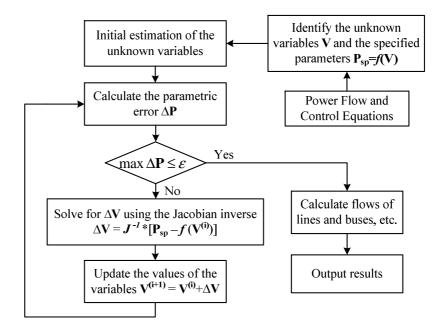

| Figure 3.2: Flow chart of the NR method for MTDC power flow                                                        |

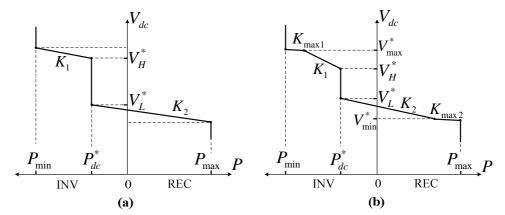

| Figure 3.3: (a) V-P droop with deadband; (b) V-P droop with deadband and voltage limits                            |

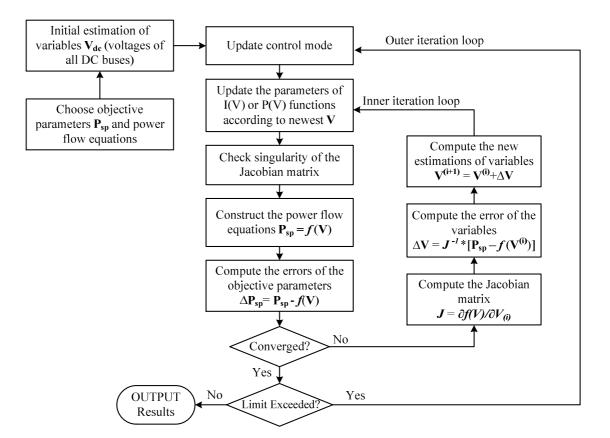

| Figure 3.4: Flow chart of the DC power flow with generic droop lines                                               |

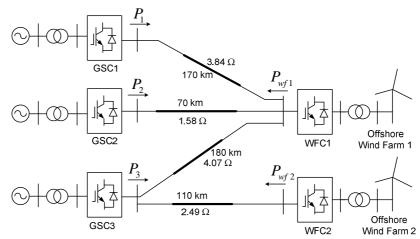

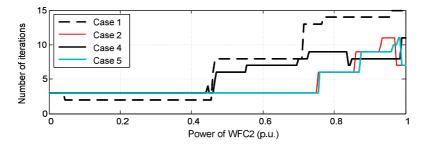

| Figure 3.5: Five-Terminal test network for power flow studies                                                      |

| Figure 3.6: DC voltage characteristics of the three GSCs                                                           |

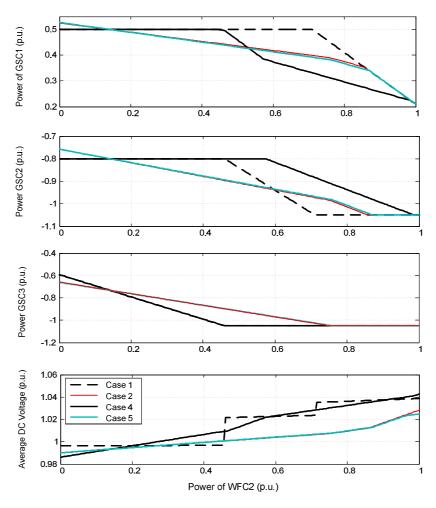

| Figure 3.7: Steady-State variations of the power generations of the GSCs and the average DC voltage                |

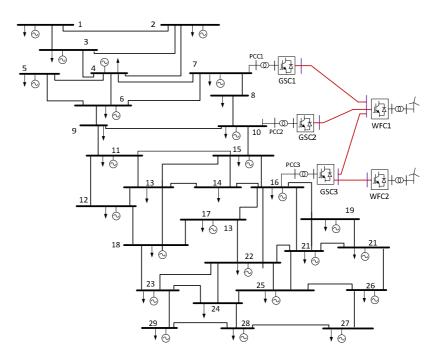

| Figure 3.8: Number of iterations for the five control cases for a series of wind farm generations                  |

| Figure 3.9: Test system for integrated AC/DC power flow100                                                         |

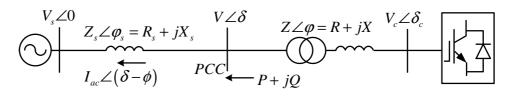

| Figure 3.10: Power transfer between a VSC and a simplified AC system101                                            |

| Figure 3.11: (a) Simplified lagging power factor diagram; (b) Scaled lagging power factor diagram. 102             |

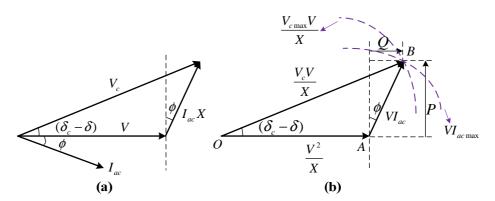

| Figure 3.12: Impact of the key factors on the VSC PQ capability curve103                                           |

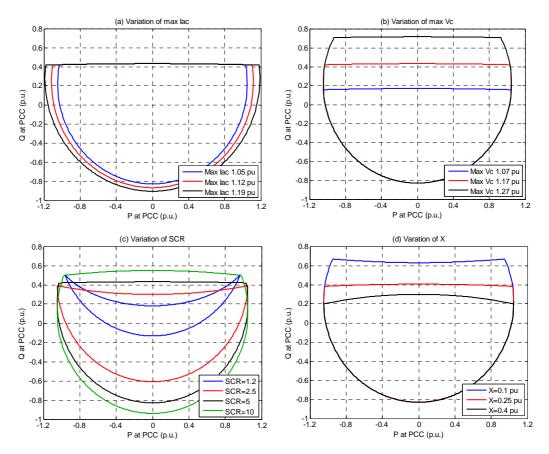

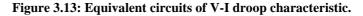

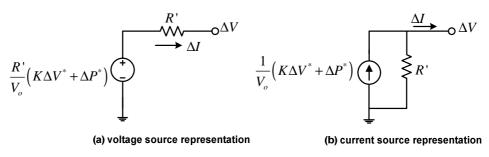

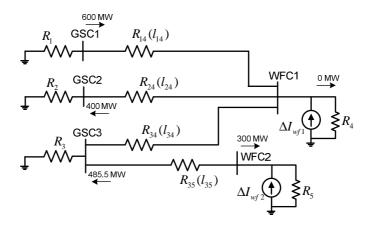

| Figure 3.13: Equivalent circuits of V-I droop characteristic                                                       |

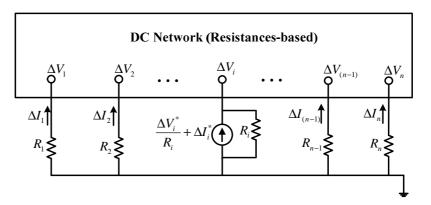

| Figure 3.14: Linearised equivalent circuit for a generalised DC network with V-I droop control                     |

| Figure 3.15: Equivalent circuit of V-P droop control                                                               |

| Figure 3.16: Equivalent circuit of the droop controlled five-terminal test system111                               |

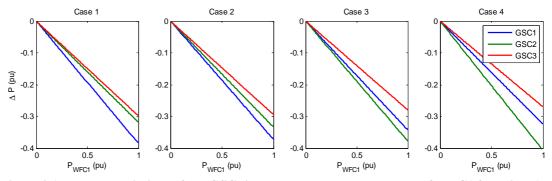

| Figure 3.17: Power deviations of the GSCs in response to the power ramp of WFC1 from 0 to 1 pu                     |

| Figure 3.18: Power and voltage deviations of the GSCs in response to 0.7 pu power increase of WFC2, with identical droop gain applied to the GSCs                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

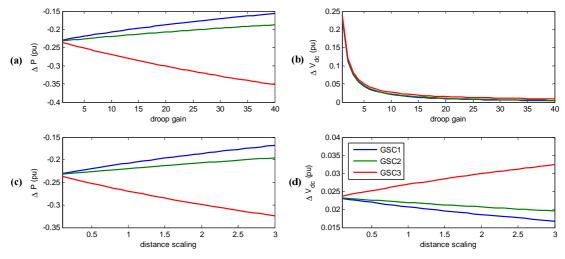

| Figure 3.19: Hierarchical MTDC control structure                                                                                                                                                           |

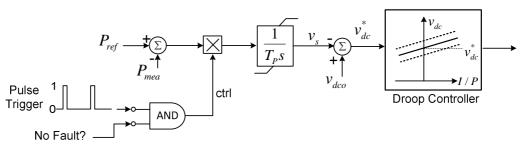

| Figure 3.20: Integrator-Based setpoint control (ISC) structure                                                                                                                                             |

| Figure 3.21: Dynamic performance of the ISC and DSC schemes in response to the power change of WFC                                                                                                         |

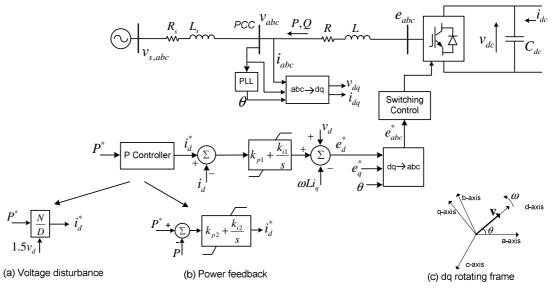

| Figure 4.1: Active power controllers employing vector current control: (a) voltage disturbance/feedforward; (b) power feedback                                                                             |

| Figure 4.2: Model of the d-axis current loop                                                                                                                                                               |

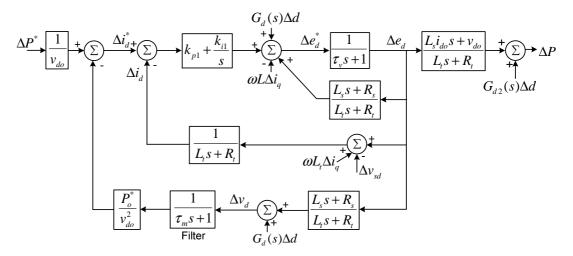

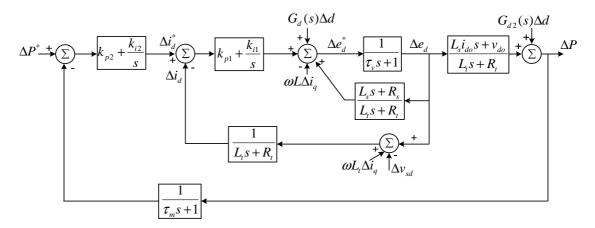

| Figure 4.3: Linearised model of the feedforward active power control122                                                                                                                                    |

| Figure 4.4: Linearised model of the feedback active power control122                                                                                                                                       |

| Figure 4.5: Frequency response comparisons for (a) the transfer function $P(s)/i_d^*(s)$ and (b) the FF tracking transfer function $P(s)/P^*(s)$ , ( $P_o=-0.6$ pu rectifier, $i_d$ loop bandwidth=200 Hz) |

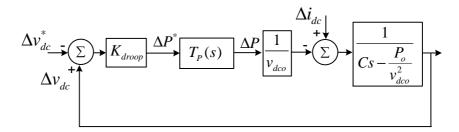

| Figure 4.6: Linearised V-P droop control employing the power loop126                                                                                                                                       |

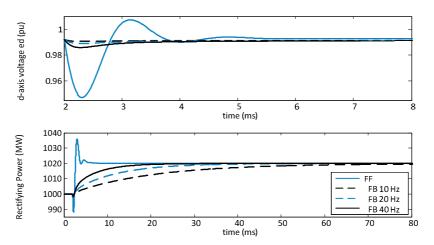

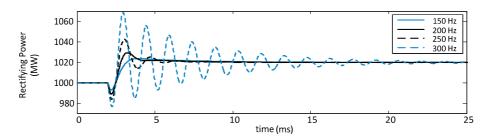

| Figure 4.7: Step responses of the power loops of different bandwidths ( $i_d$ loop bandwidth=250 Hz, SCR=5)                                                                                                |

| Figure 4.8: Step responses of FF control systems with various current loop bandwidths (SCR=4)                                                                                                              |

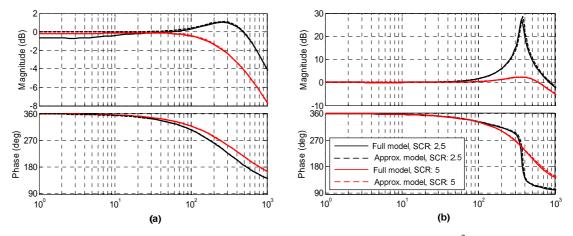

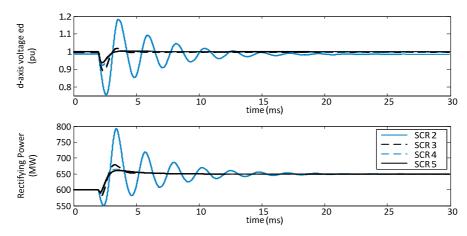

| Figure 4.9: Impact of SCR on the performance of FF control ( $i_d$ loop bandwidth=200 Hz).<br>                                                                                                             |

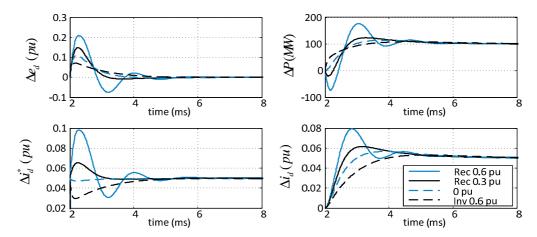

| Figure 4.10: Step responses of the FF power control under a series of power operating points (SCR=5, $i_d$ loop bandwidth=250 Hz)131                                                                       |

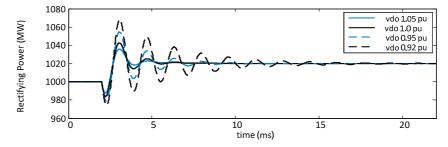

| Figure 4.11: Impact of the PCC voltage on the step response of the FF power control (SCR=4, $i_d$ loop bandwidth=250 Hz)131                                                                                |

| Figure 4.12: Simulations of a 0.1pu step of DC current disturbance for droop control based on different power control modes                                                                                |

| Figure 4.13: Four-Terminal test network and droop characteristics                                                                                                                                          |

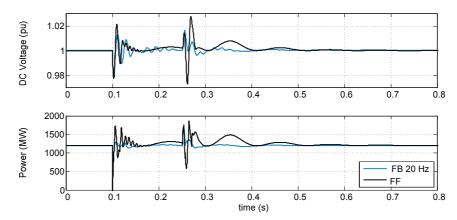

| Figure 4.14: Responses of the DC voltage and power of GSC1 to 30% voltage sag at PCC1 ( $i_d$ loop bandwidth=200 Hz; SCR=4)                                                                                |

| Figure 4.15: Responses of the DC voltage and power of GSC1 to the outage of GSC3.                                                                                                                          |

| Figure 5.1: VSC-HVDC system for analytical modelling                                                                                                                                                       |

| Figure 5.2: Closed-Loop SRF PLL                                                                                                                                                                            |

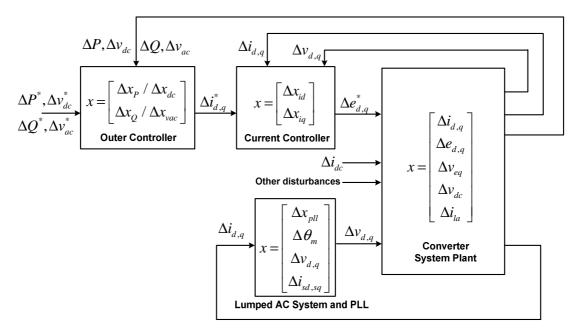

| Figure 5.3: Generalised state-space model for grid side VSC-HVDC143                                                                                                                                        |

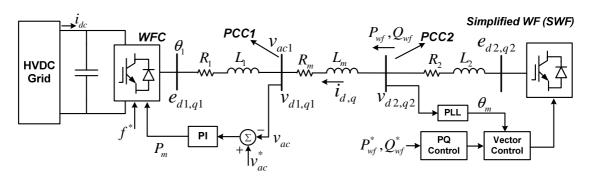

| Figure 5.4: Control block diagram of the WFC and the simplified wind farm (SWF) model                                                                                                                      |

| Figure 5.5: State-Space formulation of the wind farm side terminal144                                                                                                                                      |

| Figure 5.6: Circuit of a multi- $\pi$ cable model with DC inductors at two ends146                                                                                                                         |

| Figure 5.7: DC network model integrating multiple DC line models                                                                                                                                           |

| Figure 5.8: Formulation of the state-space model for MTDC systems148                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.9: The nominal power flow and control modes of the four-terminal test system.                                                                                                                    |

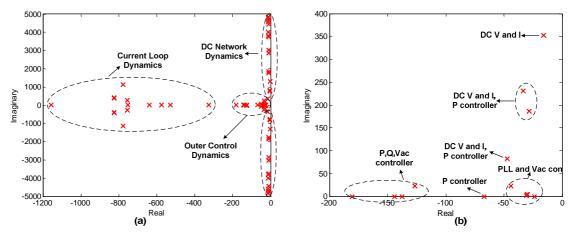

| Figure 5.10: Eigenvalues and their dominant state variables                                                                                                                                               |

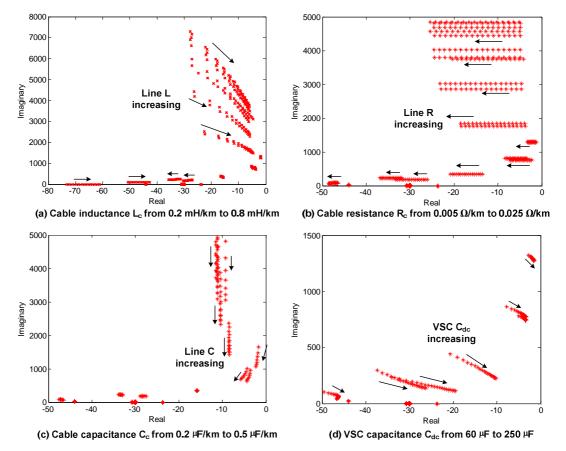

| Figure 5.11: Trajectories of eigenvalues as a function of different DC system parameters (nominal parameters: $L_c=0.466$ mH/km, $R_c=0.0113 \Omega/km$ , $C_c=0.28 \mu$ F/km, $C_{dc}=98 \mu$ F).<br>153 |

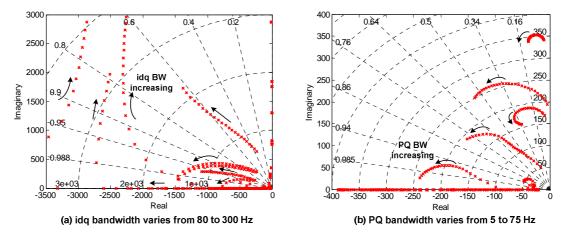

| Figure 5.12: Trajectories of eigenvalues corresponding to the variations of controller settings                                                                                                           |

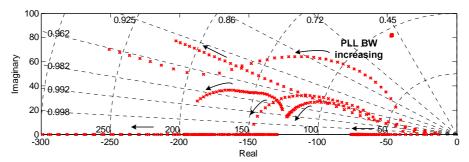

| Figure 5.13: Trajectories of eigenvalues as the PLL bandwidth varies from 5 to 100 Hz.                                                                                                                    |

| Figure 5.14: Trajectories of the dominant modes as the droop gain of GSC2 and GSC3 varies from 5 to 36 (GSC1: constant power control, GSC2 and GSC3: V-P droop control).                                  |

| Figure 5.15: DC voltage responses to 100 MW change of wind farm power under three OP scenarios                                                                                                            |

| Figure 6.1: The three types models for DC side                                                                                                                                                            |

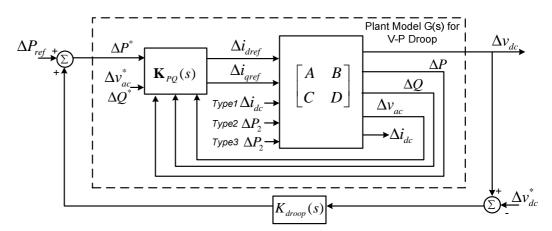

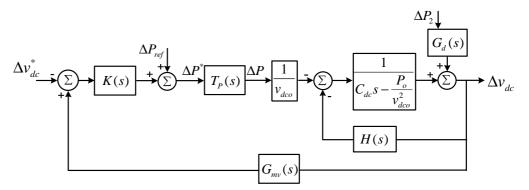

| Figure 6.2: Formulation of the plant model for V-P droop control                                                                                                                                          |

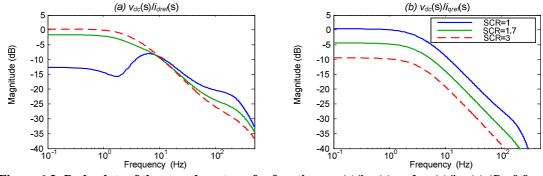

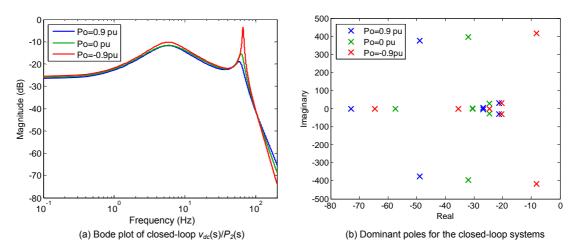

| Figure 6.3: Bode plots of the open-loop transfer functions $v_{dc}(s)/i_{dref}(s)$ and $v_{dc}(s)/i_{qref}(s)$ ( $P_o=0.9$ pu INV, type 1 model)                                                          |

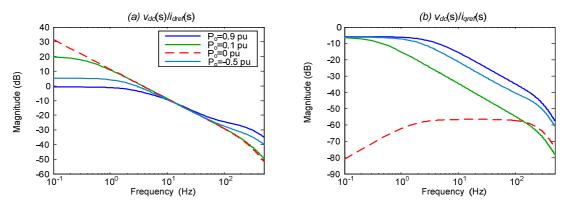

| Figure 6.4: Frequency responses of the open-loop transfer functions $v_{dc}(s)/i_{dref}(s)$ and $v_{dc}(s)/i_{qref}(s)$ (SCR=2, type 1 model)                                                             |

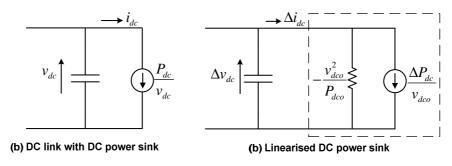

| Figure 6.5: Simplified DC link model with DC power sink                                                                                                                                                   |

| Figure 6.6: Linearised DC voltage control loop (type 2 model)163                                                                                                                                          |

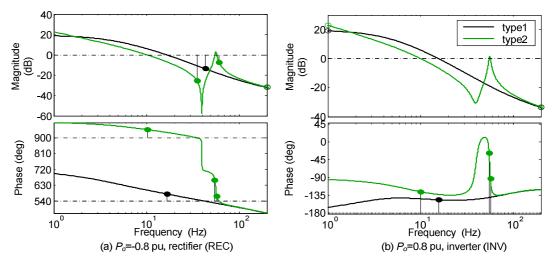

| Figure 6.7: Frequency responses of the loop transfer functions L(s) regarding V-P droop control, with $P_o$ =-0.8 pu REC in (a) and $P_o$ =0.8 pu INV in (b) ( $K_{droop}$ =7.5, SCR=2.5).164             |

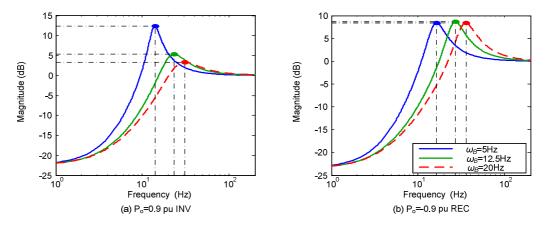

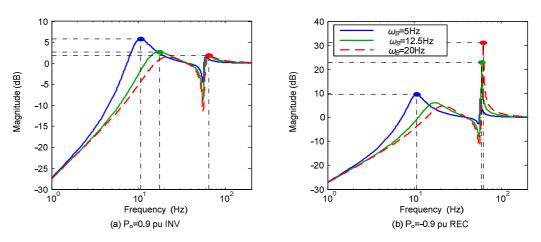

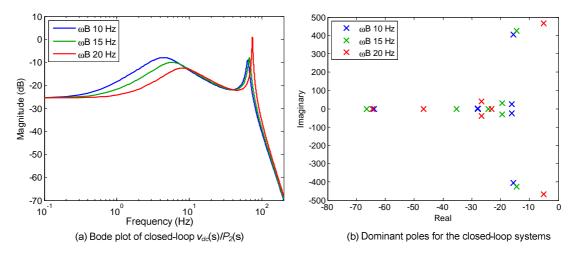

| Figure 6.8: Frequency response of the sensitivity transfer function $ S(j\omega) $ (type 1 model, SCR=2.5, $K_{droop}$ =12.5)                                                                             |

| Figure 6.9: Frequency response of the sensitivity transfer function $ S(j\omega) $ (type 2 model, SCR=2.5, $K_{droop}$ =12.5)                                                                             |

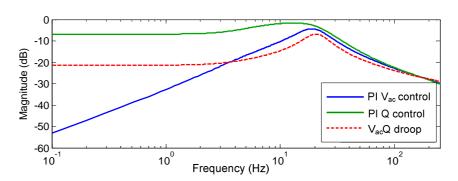

| Figure 6.10: Frequency response of the closed-loop transfer function $v_{ac}(s)/i_{dc}(s)$ for three AC voltage/reactive power control designs ( $K_{droop}$ =12.5, SCR=1.65, $P_o$ =0.9 pu INV). 166     |

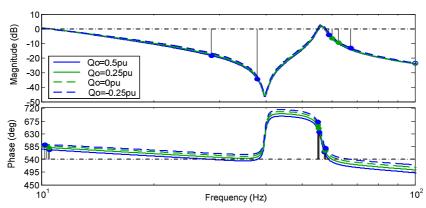

| Figure 6.11: Frequency response of the loop transfer function $L(s)$ for four reactive power operating point (SCR=1.8, $P_o$ =-0.5 pu REC, $K_{droop}$ =7.5, type 2 model)167                             |

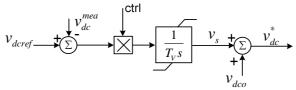

| Figure 6.12: Droop controllers modified with transient compensation                                                                                                                                       |

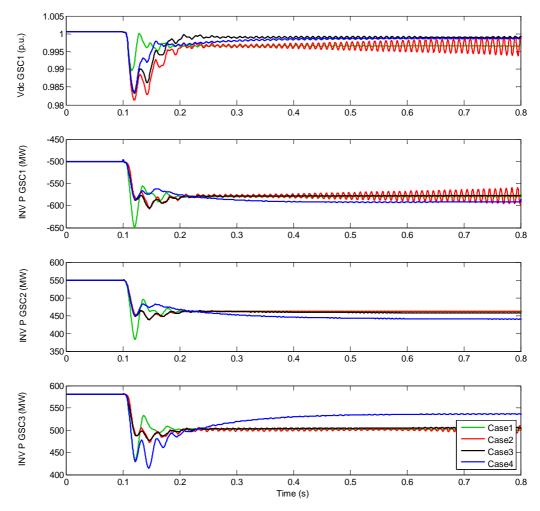

| Figure 6.13: Four-Terminal test network and droop lines for GSCs                                                                                                                                          |

| Figure 6.14: Simulation of loss of 250 MW wind power and comparison of performance of the three types of droop design for GSC1                                                                            |

| Figure 6.15: A generalised closed-loop diagram for V-I droop control171                                                                                                                                   |

| Figure 6.16: Formulation of the open-loop/closed-loop model for V-I droop control (type 3 model)                                                                                                          |

| Figure 6.17: Analytical results of the type 3 model with respect to three V-I droop settings (cable length=150 km, $P_o$ =-0.8 pu REC, type 3 model)172                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.18: Analytical results of the type 3 model with respect to three power operating points (cable length=150 km, $R_{droop}$ =0.05, type 3 model)                                                    |

| Figure 6.19: Analytical results of the type 3 model with respect to three PI v <sub>dc</sub> controllers (cable length=150 km, $R_{droop}$ =0.05, $P_o$ =-1.0 pu REC, type 3 model)                        |

| Figure 6.20: Dynamic responses of the four-terminal test system to sudden loss of 250 MW wind farm power, under four control scenarios                                                                     |

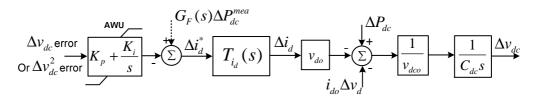

| Figure 6.21: DC voltage control with feedforward DC power                                                                                                                                                  |

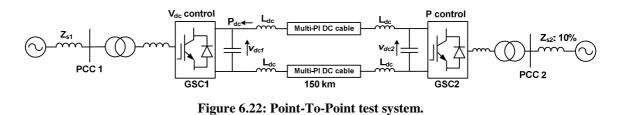

| Figure 6.22: Point-To-Point test system                                                                                                                                                                    |

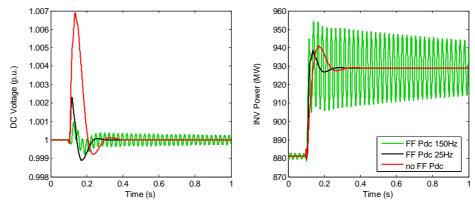

| Figure 6.23: Responses of GSC1 to a 50-MW power reference change of GSC2 for three types of DC voltage controller at GSC1 ( $L_{dc}$ =0 mH, $Z_{sI}$ =0.4 pu)177                                           |

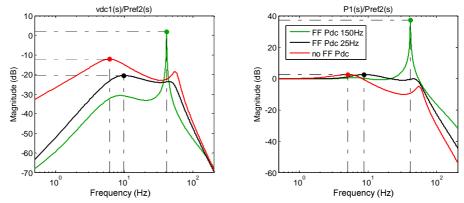

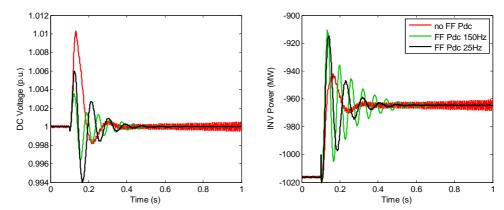

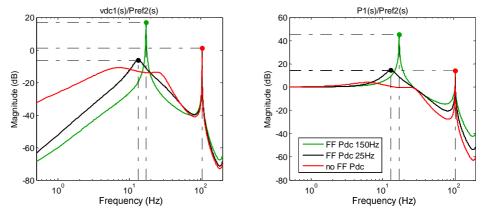

| Figure 6.24: Frequency responses of the closed-loop transfer function $v_{dc1}(s)/P_{ref2}(s)$ and $P_1(s)/P_{ref2}(s)$ ( $P_o=0.93$ pu INV, $L_{dc}=0$ mH, $Z_{s1}=0.4$ pu, type 3 model)177              |

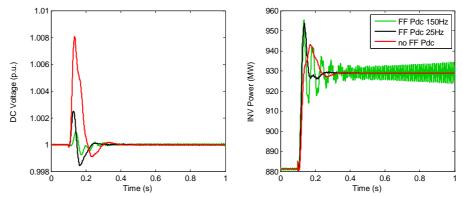

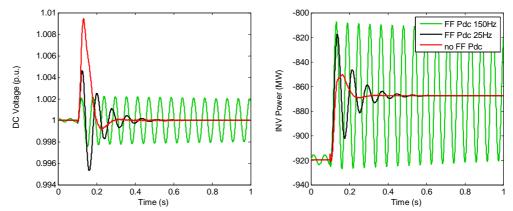

| Figure 6.25: Responses of GSC1 to the 50 MW power reference change of GSC2 for three types of DC voltage controller at GSC1 (Inverter, $L_{dc}$ =125 mH, $Z_{sI}$ =0.4 pu)178                              |

| Figure 6.26: Responses of GSC1 to a 50-MW power reference change of GSC2 for three types of DC voltage controller at GSC1 (Rectifier, $L_{dc}$ =125 mH, $Z_{sI}$ =0.4 pu)178                               |

| Figure 6.27: Responses of GSC1 to a 50-MW power reference change of GSC2 for three types of DC voltage controller at GSC1 ( $P_o$ =-0.87 pu REC, $L_{dc}$ =125 mH, SCR1=10)179                             |

| Figure 6.28: Frequency responses of the closed-loop transfer function $v_{dc1}(s)/P_{ref2}(s)$ and $P_I(s)/P_{ref2}(s)$ ( $P_o$ =-0.87 pu REC, $L_{dc}$ =125 mH, SCR1=10, type 3 model)179                 |

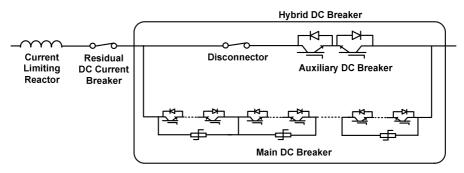

| Figure 7.1: ABB proactive HVDC circuit breaker [23]181                                                                                                                                                     |

| Figure 7.2: Formulation of plant model for DC voltage control                                                                                                                                              |

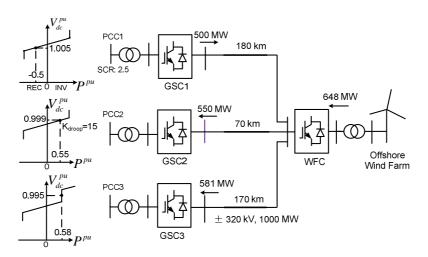

| Figure 7.3: Four-terminal VSC-HVDC test model184                                                                                                                                                           |

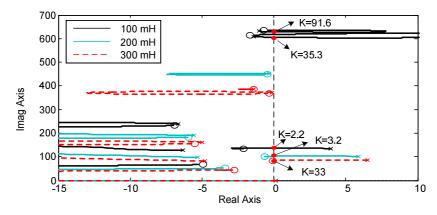

| Figure 7.4: Root loci of the open-loop transfer function of $v_{dcl}(s)/P_1^*(s)$ for the four-<br>terminal model in low-frequencies: (a) without DC reactor; (b) with DC reactor of 100 mH                |

| Figure 7.5: Trajectories of the dominant poles and zeros of the open-loop transfer function $v_{dc3}(s)/P_3^*(s)$ as GSC3's inverting power varies from 0.85 pu (INV) to -0.45 pu (REC)                    |

| Figure 7.6: Root loci of the open-loop transfer function $v_{dc3}(s)/P_3^*(s)$ of the four-terminal model for three DC inductor sizes                                                                      |

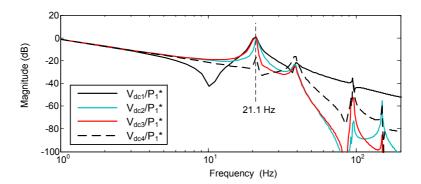

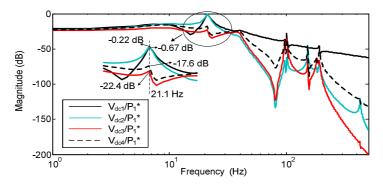

| Figure 7.7: Frequency responses of the open-loop transfer functions between the DC voltages of the four terminals and the power reference of GSC1 $P_1^*(s)$ , the four-terminal model                     |

| Figure 7.8: Frequency responses of the closed-loop transfer functions between the DC voltages of the four terminals and $P_I^*(s)$ , with droop controller at GSC3 ( $K_{droop}$ =15), four-terminal model |

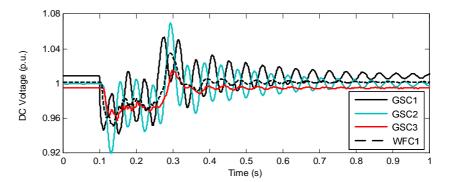

| Figure 7.9: Responses of the DC voltages to a 50% AC voltage sag caused by a fault at PCC1 (V-P droop control at GSC3 with $K_{droop}$ =15, four-terminal model)189                                        |

| Figure 7.10: Responses of the DC voltages to a 50% AC voltage sag caused by a fault at PCC1 (V-I droop control at GSC3 with $R_{droop}$ =0.05, four-terminal model)                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

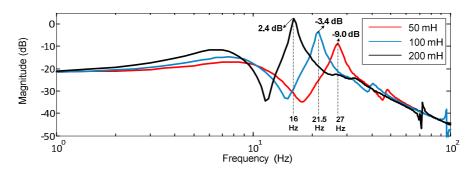

| Figure 7.11: Frequency response of the closed-loop transfer function $v_{dcl}(s)/P_l(s)$ for three sizes of DC reactors, with droop controller at GSC3 ( $K_{droop}$ =15)190                                                                                                                       |

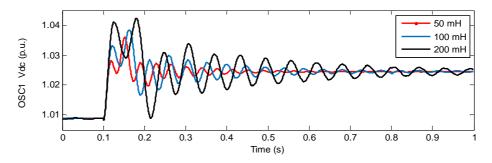

| Figure 7.12: Response of the DC voltage of GSC1 to a 0.2 pu step change of the power reference $P_1^*$ , with droop controller at GSC3 ( $K_{droop}$ =15)                                                                                                                                          |

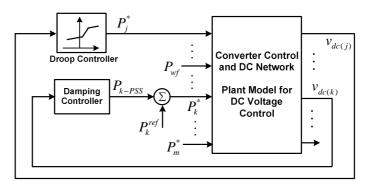

| Figure 7.13: Generalised closed-loop model for DC voltage control in MTDC systems with damping controllers                                                                                                                                                                                         |

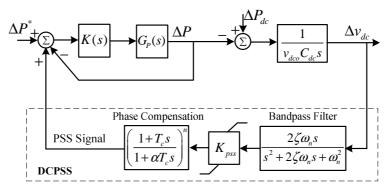

| Figure 7.14: DC voltage damping controller (DCPSS) structure                                                                                                                                                                                                                                       |

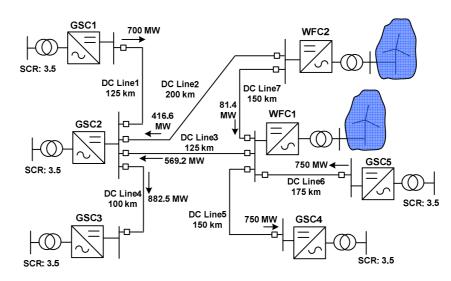

| Figure 7.15: Network diagram of the seven-terminal HVDC test model                                                                                                                                                                                                                                 |

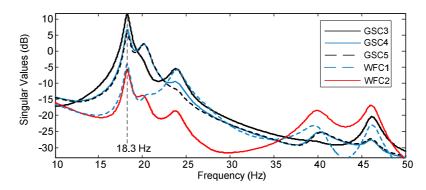

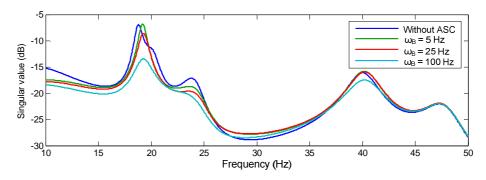

| Figure 7.16: Singular value plots of the closed-loop models with all the DC terminal voltages as output and the power of selected terminal as input (GSC1: $K_{droop}=7$ ; GSC2: $K_{droop}=15$ )                                                                                                  |

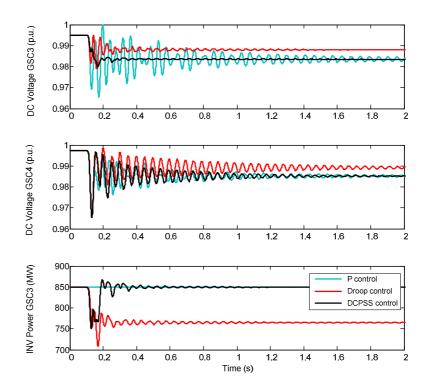

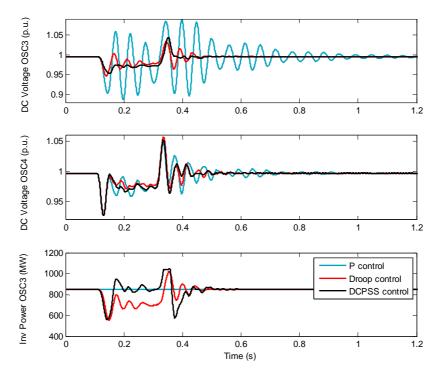

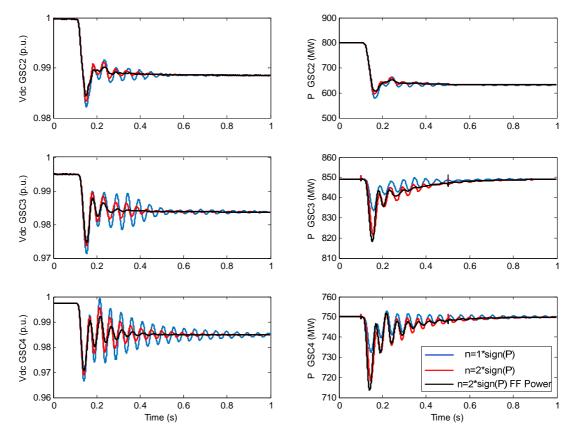

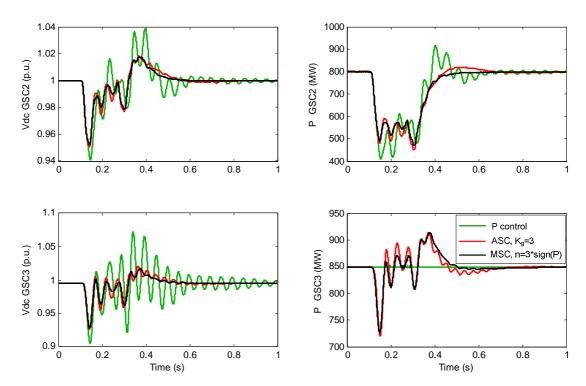

| Figure 7.17: Responses of the DC voltage and power of GSC3 and GSC4 to a loss of 250 MW generation in wind farm 2, with three types of control applied to GSC3 (Case 1: GSC1 and GSC2 in droop mode)                                                                                               |

| Figure 7.18: Responses of the DC voltage and power of GSC3 and GSC4 to a fault occurring at PCC5, with three types of control applied to GSC3 (Case 2: GSC1, GSC2 and GSC4 in droop control)                                                                                                       |

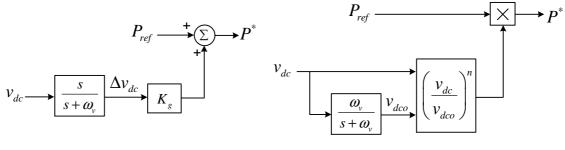

| Figure 7.19: Two active DC link stabilising control structures                                                                                                                                                                                                                                     |

| Figure 7.20: Trajectories of the dominant poles and zeros of the open-loop transfer function $v_{dc3}(s)/P_3^*(s)$ as GSC3's inverting power varies from 0.85 pu (INV) to -0.45 pu (REC), seven-terminal model (for the MSC case, sign( $P_o$ )=1 if $P_o$ >0, while sign( $P_o$ )=-1 if $P_o$ <0) |

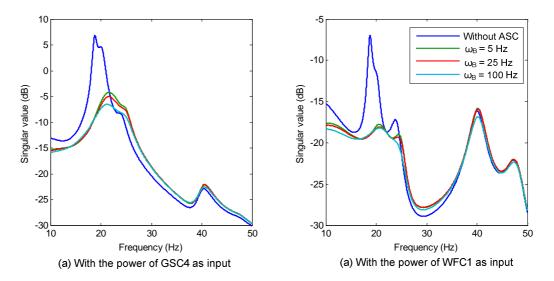

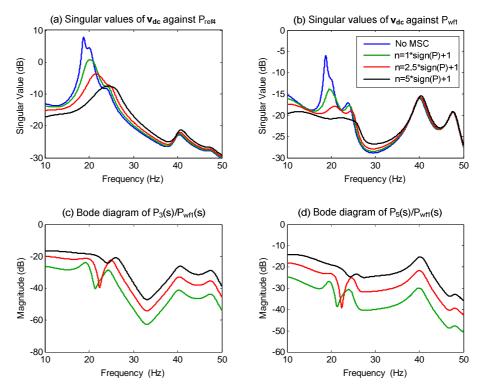

| Figure 7.21: Singular value plots of the closed-loop models with all the DC terminal voltages as output and the power of selected terminal as input (seven-terminal model, ASC with $K_g=2$ for GSC3 and GSC5, GSC1 $K_{droop}=7$ , GSC2 $K_{droop}=15$ , GSC4 in constant power control)          |

| Figure 7.22: Singular value plots of the closed-loop models with all the DC terminal voltages as output and the power of WFC1 as input (seven-terminal model, ASC with $K_g=2$ for GSC4 and GSC5, GSC1 $K_{droop}=7$ , GSC2 $K_{droop}=15$ , GSC4 in constant power control)                       |

| Figure 7.23: Closed-loop frequency responses for different settings of MSC gains (seven-terminal model, GSC1: $K_{droop}$ =7, GSC2: $K_{droop}$ =15; MSC with identical gains applied to GSC3, GSC4 and GSC5)203                                                                                   |

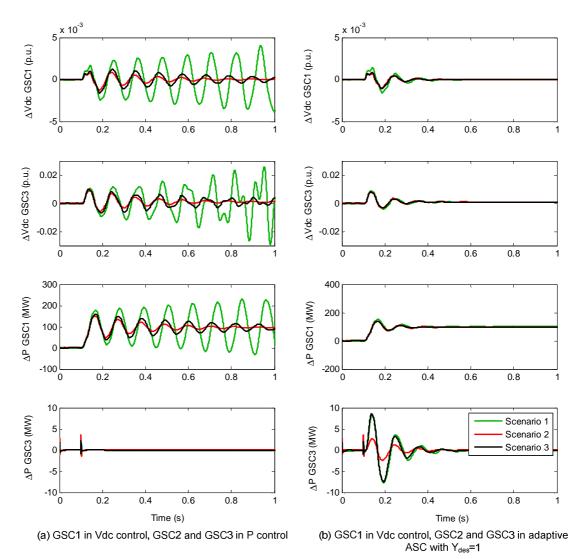

| Figure 7.24: Transient responses of GSC1 and GSC3 to the sudden increase of 100 MW wind farm power for each scenario (four-terminal model)                                                                                                                                                         |

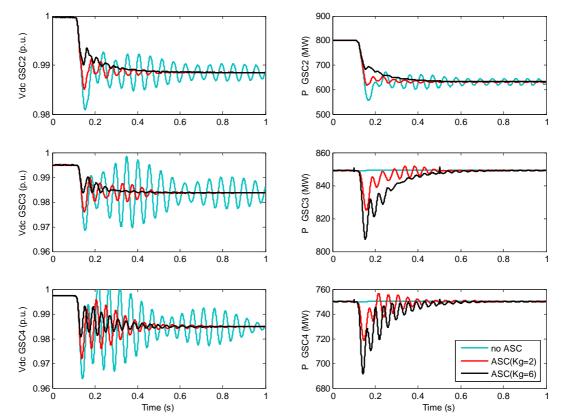

| Figure 7.25: Transient responses of GSC2, GSC3 and GSC4 to a loss of 250 MW generation in wind farm 2, with three types of control applied to GSC3, GSC4 and GSC5 (GSC1 $K_{droop}$ =7, GSC2 $K_{droop}$ =15)                                                                                      |

| Figure 7.26: Transient responses of GSC2, GSC3 and GSC4 to a loss of 250 MW generation in wind farm 2, with three types of MSC control applied to GSC3, GSC4 and GSC5 (GSC1 $K_{droop}$ =7, GSC2 $K_{droop}$ =15)                                                                                  |

| Figure 7.27: Transient responses to the AC fault causing 50% voltage sag at the PCC5, with three control settings applied to GSC3, GSC4 and GSC5, and V-I droop used for GSC1 ( $R_{droop}$ =4%) and GSC2 ( $R_{droop}$ =2.5%) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure A.1: Stationary and rotating reference frames                                                                                                                                                                           |

| Figure A.2: Basic dynamic inductor and capacitor circuits                                                                                                                                                                      |

| Figure C.1: Power flow calculation procedure for the initial condition computation250                                                                                                                                          |

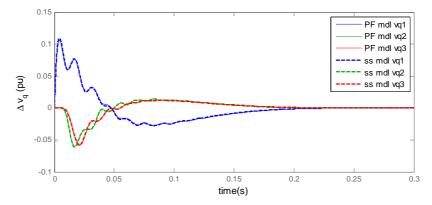

| Figure C.2: $\Delta v_{dc}$ responses to the step of $\Delta P_{refl}$ (all GSCs in droop $V_{dc}$ - $P$ and constant $Q$ control)                                                                                             |

| Figure C.3: $\Delta P_{ac}$ responses to the step of $\Delta P_{refl}$ (all GSCs in $V_{dc}$ - $P$ droop and constant $Q$ control)                                                                                             |

| Figure C.4: $\Delta v_q$ responses to the step of $\Delta P_{refl}$ (all GSCs in $V_{dc}$ - $P$ droop and constant $Q$ control)                                                                                                |

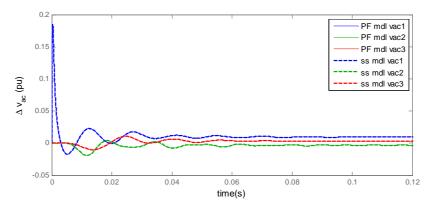

| Figure C.5: $\Delta v_{ac}$ responses to the step of $\Delta P_{refl}$ (all GSCs in $V_{dc}$ - $P$ droop and $V_{ac}$ - $Q$ droop control).                                                                                    |

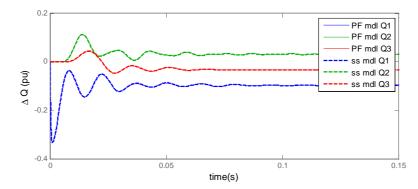

| Figure C.6: $\Delta Q$ responses to the step of $\Delta P_{ref1}$ (all GSCs in $V_{dc}$ - $P$ droop and $V_{ac}$ - $Q$ droop control)                                                                                          |

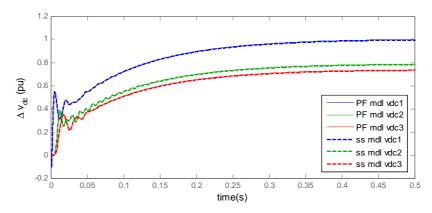

| Figure C.7: $\Delta v_{dc}$ responses to the step of $\Delta v_{dcref1}$ (GSC1: constant $V_{dc}$ control, $V_{ac}$ - $Q$ droop control; GSC2 and GSC3: $V_{dc}$ - $P$ droop control, $V_{ac}$ - $Q$ droop control)253         |

| Figure D.1: Droop characteristics for the three GSCs of the test system                                                                                                                                                        |

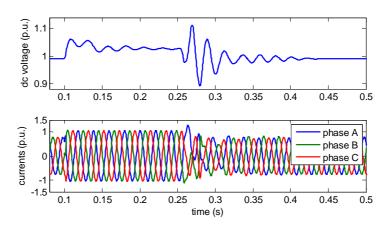

| Figure D.2: Responses of DC voltage and phase currents of GSC3 to a fault at PCC3 (fault impedance: $4 \Omega$ )                                                                                                               |

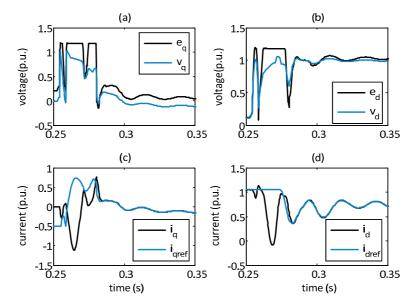

| Figure D.3: Responses of the d-axis and q-axis voltages and currents of GSC3 to the clearance of the fault at PCC3 (fault impedance: $4 \Omega$ )                                                                              |

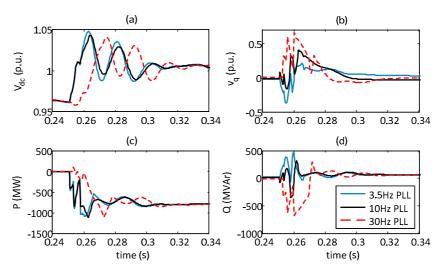

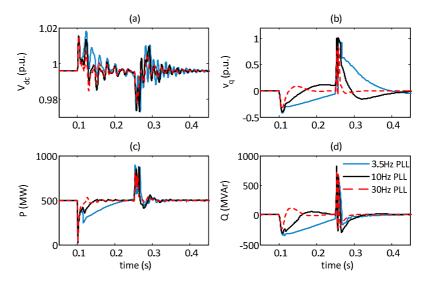

| Figure D.4: Impact of the PLL bandwidth on the responses to the fault clearance (fault location: PCC1, fault impedance: 1 $\Omega$ )                                                                                           |

| Figure D.5: Impact of the PLL bandwidth on the responses to the fault clearance (fault location: PCC2, fault impedance: $20 \Omega$ )                                                                                          |

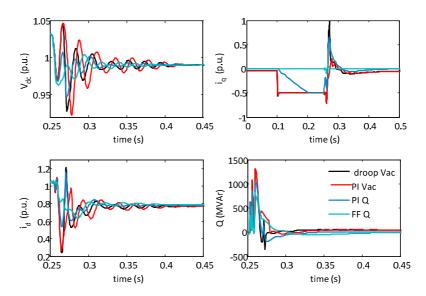

| Figure D.6: Impact of reactive power controllers on the AC grid fault responses of GSC3 (fault location: PCC3, fault impedance: $2 \Omega$ )                                                                                   |

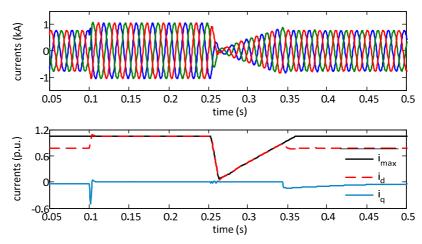

| Figure D.7: Response of the GSC3 currents to the fault at the bus PCC3, with the adaptive current limit applied (fault impedance: $4 \Omega$ )                                                                                 |

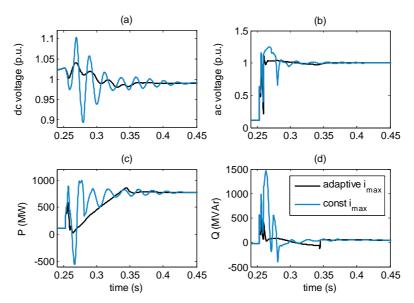

| Figure D.8: Response of voltages and powers of GSC3 with the adaptive current limit applied (fault location: PCC3, fault impedance: 4 $\Omega$ )                                                                               |

## **List of Tables**

| Table 2.1: Comparison of the frequency-response measures for multiple current controller designs.                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2: Comparison of the frequency-response measures for multiple DC voltage controller designs.                                            |

| Table 2.3: Controller types and upper voltage references for five cases of voltage margin control.       81                                     |

| Table 3.1: Power flow results of the nominal operating point                                                                                    |

| Table 3.2: Power flow results of the outage of GSC2 (in pu)                                                                                     |

| Table 3.3: Power flow results of the outage of WFC1 (in pu)                                                                                     |

| Table 3.4: Power flow results for GSCs                                                                                                          |

| Table 3.5: Comparison of the actual and estimated power flow results.    107                                                                    |

| Table 3.6: Four test cases for power sharing demonstration                                                                                      |

| Table 3.7: Optimised operating points for the WFC power of 0.5 pu and 0.2 pu ( $P_{GSC1}$ fixed at 0.8 pu)                                      |

| Table 4.1: Frequency domain measures for the controls simulated in Figure 4.7                                                                   |

| Table 4.2: Impact of current loop bandwidth on the FF Control and the FB control(feedback power loop bandwidth=12.5Hz, SCR=4)129                |

| Table 4.3: Impact of SCR on the frequency domain measures ( $i_d$ loop BW=200 Hz,<br>$P_o=0.3$ pu INV)                                          |

| Table 4.4: Impact of the power OP on the frequency domain indicators (for SCR=5, $i_d$ loop BW=250 Hz)131                                       |

| Table 4.5: Maximum droop gain $K_{droop}$ allowed for the FF and the 20 Hz FB power control, with SCR=4 and current BW=200 Hz (rectifier OP)133 |

| Table 4.6: Frequency domain measures for the droop control with $C_{dc}$ =66 µF and $P_o$ =-0.8 pu REC, SCR=4                                   |

| Table 5.1: Selected eigenvalues and the corresponding dominant participant variables.                                                           |

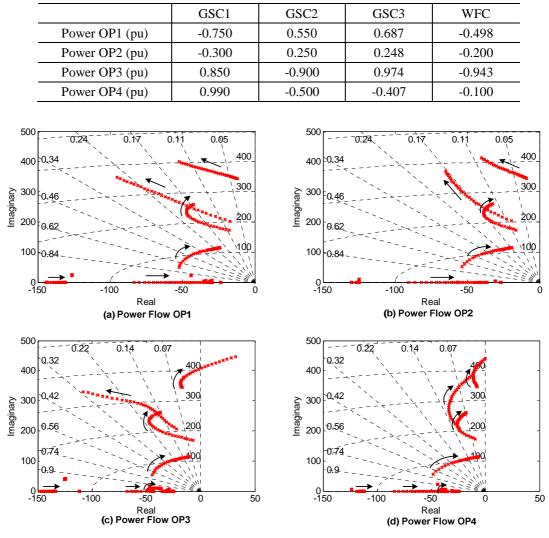

| Table 5.2: Four power flow operating points (OP) for the four-terminal system155                                                                |

| Table 6.1: Frequency domain indicators as converter power varies                                                                                |

| Table 6.2: Parameters of the droop controllers.    169                                                                                          |

| Table 6.3: Frequency domain measure of the droop controllers                                                                                    |

| Table 6.4: Four control cases for the four-terminal test system                                                                                 |

| Table 7.1: Selected participation factors for the seven-terminal system.         193                                                            |

| Table 7.2: Control modes and droop gains of GSCs for Case 1 and 2                                                                               |

| Table 7.3: DCPSS parameters for two case studies.    195                                                                                        |

| Table 7.4: Low-frequency modes with and without DCPSS (Case 1)197                                                                               |

| Table 7.5: Low-frequency modes with and without DCPSS (Case 2)                                                                                  |

|                                                                                                                                                 |

| Table A.1: Base data of AC and DC systems.                                             | 232      |

|----------------------------------------------------------------------------------------|----------|

| Table A.2: Grid side model parameters.                                                 | 232      |

| Table A.3: DC cable model parameters.                                                  | 232      |

| Table A.4: Nominal controller data (in per unit) for grid side converters              | 232      |

| Table A.5: Wind farm side converter model parameters                                   | 234      |

| Table A.6: Nominal control parameters (in per unit) for wind farm side converters      | 234      |

| Table A.7: Parameters of the simplified wind farm modelled by static generators        | 234      |

| Table A.8: DC chopper data corresponding to Figure 2.19.                               | 235      |

| Table A.9: Vector current controller data corresponding to Table 2.1.                  | 235      |

| Table A.10: DC voltage controller data corresponding to Table 2.2 ( $C_{dc}$ =146 µF). | 235      |

| Table A.11: Parameters of the GSC model used in Chapter 4                              | 235      |

| Table A.12: Parameters of the current and active power controllers used in Chapter     | er 4.235 |

|                                                                                        |          |

| Table B.1: IGBT/Diode data used for converter loss calculation [123].                  | 237      |

|                                                                                        |          |

|                                                                                        |          |

Table C.1: The participation variables and participation factors for the base-case four-terminal model shown in Figure 5.9.

| Table D.1: Default settings for the controllers to be studied | 258 |

|---------------------------------------------------------------|-----|

|---------------------------------------------------------------|-----|

## Nomenclature

## List of Acronyms

| AC    | Alternating Current                    |

|-------|----------------------------------------|

| ACE   | Area Control Error                     |

| AGC   | Automatic Generation Control           |

| ASC   | Additive Stabilising Control           |

| AVM   | Average-Value Model                    |

| AWU   | Anti-Windup                            |

| BPF   | Band-Pass Filter                       |

| BW    | Bandwidth                              |

| DC    | Direct Current                         |

| DCCB  | HVDC Circuit Breaker                   |

| DCPSS | Direct Current Power System Stabiliser |

| DFIG  | Double-Fed Induction Generator         |

| DSC   | Direct Setpoint Calculation            |

| DSPF  | DIgSILENT PowerFactory                 |

| EMT   | Electromagnetic Transient              |

| FB    | Feedback                               |

| FF    | Feedforward                            |

| FRC   | Fully Rated Converter                  |

| FRT   | Fault Ride-Through                     |

| GM    | Gain Margin                            |

| GSC   | Grid Side Converter                    |

| HVDC  | High Voltage Direct Current            |

| IMC   | Internal Model Control                 |

| INV   | Inverter                               |

| ISC   | Integrator-based Setpoint Control      |

| LA    | Lower Arm                              |

| LCC   | Line Commutated Converter              |

| LHP   | Left-Half Plane                        |

| MI    | Mass Impregnated                       |

| MIMO  | Multi-Input-Multi-Output               |

| MMC   | Modular Multilevel Converter           |

| MPC   | Model Predictive Control               |

| MSC   | Multiplicative Stabilising Control     |

|       |                                        |

| MTDC    | Multi-Terminal High Voltage Direct Current |

|---------|--------------------------------------------|

| OP      | Operating Point                            |

| OPF     | Optimal Power Flow                         |

| OPWM    | Optimum Pulse-Width Modulation             |

| PCC     | Point of Common Coupling                   |

| PI      | Proportional-Integral                      |

| PID     | Proportional-Integral-Derivative           |

| PLL     | Phase-Locked Loop                          |

| PM      | Phase Margin                               |

| PMSG    | Permanent Magnet Synchronous Generator     |

| POD     | Power Oscillation Damping                  |

| PSS     | Power System Stabiliser                    |

| PWM     | Pulse-Width Modulation                     |

| REC     | Rectifier                                  |

| RHP     | Right-Half Plane                           |

| RMS     | Root Mean Square                           |

| SCR     | Short-Circuit Ratio                        |

| SIMC    | Skogestad Internal Model Control           |

| SISO    | Single-Input-Single-Output                 |

| SM      | Sub-Module                                 |

| SO      | Symmetrical Optimum                        |

| SRF     | Synchronous Reference Frame                |

| STATCOM | Static Compensator                         |

| STFT    | Sensitivity Transfer Function Based Tuning |

| SWF     | Simplified Wind Farm Model                 |

| TGR     | Transient Gain Reduction                   |

| TSO     | Transmission System Operator               |

| UA      | Upper Arm                                  |

| VCO     | Voltage Controlled Oscillator              |

| V-I     | Voltage-Current                            |

| V-P     | Voltage-Power                              |

| VSC     | Voltage Source Converter                   |

| WFC     | Wind Farm Side Converter                   |

| WTG     | Wind Turbine Generator                     |

| XLPE    | Cross-Linked Polyethylene                  |

|         |                                            |

## List of Symbols

| A, B, C, D               | State-Space matrices                                                               |

|--------------------------|------------------------------------------------------------------------------------|

| С                        | Capacitance                                                                        |

| $C_0$                    | Equivalent capacitance with a value close to 0                                     |

| $C_c$                    | Cable capacitance                                                                  |

| $C_{dc}$                 | Equivalent converter capacitance                                                   |

| $C_{f}$                  | Capacitance of the filter at PCC bus                                               |

| d                        | Disturbance variable                                                               |

| $e_{(abc)}$              | Phase voltages of VSC AC terminal                                                  |

| f                        | Frequency                                                                          |

| $G_d(s)$                 | Disturbance transfer function                                                      |

| $\dot{i}_{(abc)}$        | VSC phase currents                                                                 |

| <i>i<sub>brake</sub></i> | DC chopper current                                                                 |

| <i>i</i> <sub>con</sub>  | DC current of average-value model                                                  |

| $i_d$                    | d-axis current across converter reactor                                            |

| $i_{dc}$                 | DC current into converter                                                          |

| $i_q$                    | q-axis current across converter reactor                                            |

| $i_{sd}$                 | d-axis current across the AC system impedance                                      |

| $i_{sq}$                 | q-axis current across the AC system impedance                                      |

| J                        | Jacobian matrix                                                                    |

| $K_d$                    | Derivative gain                                                                    |

| $K_{droop}$              | Droop gain of DC voltage droop control                                             |

| $K_i$                    | Integral gain                                                                      |

| $K_p$                    | Proportional gain                                                                  |

| $K_t$                    | Anti-windup gain                                                                   |

| $K_{VQ}$                 | Droop gain of AC voltage droop control                                             |

| L                        | Inductance                                                                         |

| l                        | Length of a cable section                                                          |

| Larm                     | Arm inductance                                                                     |

| Larmdc                   | DC side equivalent arm inductance                                                  |

| $L_c$                    | Cable inductance                                                                   |

| $L_{dc}$                 | DC reactance of a DC breaker system                                                |

| $L_s$                    | Equivalent AC system inductance                                                    |

| $L_t$                    | Aggregated inductance of AC system, converter transformer<br>and converter reactor |

| $L_T$                    | Transformer inductance                                                             |

| $M_s$                     | Frequency domain peak of sensitivity transfer function                          |

|---------------------------|---------------------------------------------------------------------------------|

| $M_T$                     | Frequency domain peak of complementary sensitivity transfer function            |

| n                         | Index of numbers or noise signal                                                |

| $N_p$                     | Number of sub-modules in parallel in each arm                                   |

| $N_s$                     | Number of sub-modules in series in each arm                                     |

| Р                         | Active power                                                                    |

| Ploss                     | Converter loss                                                                  |

| Q                         | Reactive power                                                                  |

| R                         | Resistance                                                                      |

| R <sub>arm</sub>          | Arm resistance                                                                  |

| <i>R</i> <sub>armdc</sub> | DC side equivalent arm resistance                                               |

| R <sub>brake</sub>        | DC braking resistor                                                             |

| $R_c$                     | Cable resistance                                                                |

| <i>R</i> <sub>droop</sub> | Droop constant of DC voltage droop control                                      |

| $R_o$                     | On-State slope resistance of IGBT                                               |

| $R_s$                     | Equivalent AC system resistance                                                 |

| $R_t$                     | Aggregated inductance of AC system, converter transformer and converter reactor |

| $R_T$                     | Transformer capacitance                                                         |

| U                         | Control signal(s)                                                               |

| $\mathcal{V}_{(abc)}$     | Phase voltages at PCC                                                           |

| V <sub>ac</sub>           | Instantaneous AC voltage                                                        |

| $V_{ac}$                  | Steady-State AC voltage                                                         |

| $v_d$                     | d-axis component of PCC voltage                                                 |

| $V_{dc}$                  | Steady-state DC voltage                                                         |

| <i>V<sub>dc</sub></i>     | Converter DC voltage                                                            |

| Veq                       | DC voltage across the equivalent converter capacitor                            |

| V <sub>l(abc)</sub>       | Lower arm phase voltage                                                         |

| $V_o$                     | On-State slope voltage of IGBT                                                  |

| $V_{pcc}$                 | Steady-State PCC bus voltage                                                    |

| $v_q$                     | q-axis component of PCC voltage                                                 |

| $\mathcal{V}_{s(abc)}$    | AC source phase voltage                                                         |

| V <sub>sd</sub>           | d-axis AC source voltage                                                        |

| Vsq                       | q-axis AC source voltage                                                        |

| $V_{u(abc)}$              | Upper arm phase voltage                                                         |

| X             | Reactance                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------|

| X             | State variable                                                                                |

| $X_s$         | AC system reactance                                                                           |

| Ζ             | Impedance                                                                                     |

| Z             | Exogenous output                                                                              |

| α             | Tuning parameter                                                                              |

| $\delta$      | Angle of PCC bus voltage                                                                      |

| $\delta_c$    | Angle of converter AC terminal voltage                                                        |

| ζ             | Damping ratio                                                                                 |

| $	heta_d$     | Effective time delay                                                                          |

| $	heta_i$     | Current measurement delay                                                                     |

| $	heta_m$     | Reference angle generated by PLL                                                              |

| $	heta_{pcc}$ | Angle of PCC bus voltage                                                                      |

| λ             | Eigenvalue or stored energy constant                                                          |

| $	au_{id}$    | Equivalent time constant of current control loop                                              |

| $	au_m$       | Time constant of measurement filter                                                           |

| $	au_{ u}$    | Equivalent time constant of VSC modulation control                                            |

| $\phi$        | Right eigenvector                                                                             |

| $\psi$        | Left eigenvector                                                                              |

| ω             | Frequency                                                                                     |

| $\omega_B$    | Closed-Loop bandwidth, defined as the frequency where $ S(j\omega) $ crosses 0.707 from below |

| $\omega_{BT}$ | The highest frequency where $ T(j\omega) $ crosses 0.707 from above                           |

| $\omega_d$    | Desired closed-loop bandwidth                                                                 |

| $\omega_n$    | Natural frequency                                                                             |

| $\omega_o$    | Nominal AC system frequency (50 Hz)                                                           |

## Subscripts

| $\infty$         | Infinity                                            |

|------------------|-----------------------------------------------------|

| AC               | AC system quantity                                  |

| av               | Average                                             |

| base             | Base values                                         |

| С                | Converter or cable                                  |

| con              | Converter                                           |

| cond             | Conduction                                          |

| d                | d-axis                                              |

| dc               | DC system quantity                                  |

| des              | Desired                                             |

| eq               | Equivalent                                          |

| f                | Filter                                              |

| G                | DC grid network                                     |

| Н                | Higher reference                                    |

| i                | Integral, or index value (where $i=1,2,3$ )         |

| id               | d-axis current control                              |

| in               | Input                                               |

| iq               | q-axis current control                              |

| j                | Index value, where $j=1,2,3$                        |

| L                | Lower reference                                     |

| $lim_L$          | Lower limit                                         |

| lim <sub>H</sub> | Higher limit                                        |

| m                | Measurement, or index value (where <i>j</i> =1,2,3) |

| max              | Maximum                                             |

| min              | Minimum                                             |

| 0                | Operating point or output                           |

| Р                | Active power                                        |

| pll              | Phase-Locked loop                                   |

| pss              | DC damping control                                  |

| Q                | Reactive power                                      |

| q                | q-axis                                              |

| r                | Reference                                           |

| rated            | Rated                                               |

| red              | Reduced                                             |

| S  | AC system or supplementary |

|----|----------------------------|

| SM | Sub-Module                 |

| sp | Specified                  |

| Т  | Transformer or transient   |

| tr | Transform                  |

| wf | Wind farm                  |

## Superscripts

| -    | Negative               |

|------|------------------------|

| *    | Control setpoint       |

| +    | Positive               |

| id   | d-axis current control |

| iq   | q-axis current control |

| LA   | Lower arm              |

| line | Line                   |

| теа  | Measured value         |

| Р    | Active power control   |

| ри   | Per unit               |

| pll  | Phase-locked loop      |

| Q    | Reactive power control |

| ref  | Reference              |

| UA   | Upper arm              |

| vac  | AC voltage control     |

| vdc  | DC voltage control     |

|      |                        |

Classical control system

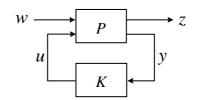

Generalised multivariable control system [1]

## List of Symbols for Control Studies

| G(s)                | System plant model                                                             |

|---------------------|--------------------------------------------------------------------------------|

| K(s)                | Controller model                                                               |

| L(s)                | Loop transfer function $L(s)=G(s)\cdot K(s)$                                   |

| T(s)                | Complementary sensitivity transfer function $T(s) = [I+G(s)K(s)]^{-1}G(s)K(s)$ |

| S(s)                | Sensitivity transfer function $S(s) = [I+G(s)K(s)]^{-1}$                       |

| $G_d(s)$            | Disturbance model                                                              |

| $G_d S(s)$          | Closed-Loop disturbance model $G_dS(s)=G_d(s)\cdot S(s)$                       |

| и                   | Control input(s)                                                               |

| у                   | Plant output(s)                                                                |

| r or y <sup>*</sup> | Reference(s)/Set-point(s)                                                      |

| d                   | Disturbance(s)                                                                 |

| y <sup>mea</sup>    | Measured output(s)                                                             |

| Р                   | Generalised plant model, including $G$ and $G_d$                               |

| W                   | Exogenous inputs                                                               |

| Z.                  | Exogenous outputs                                                              |

| n                   | Noise                                                                          |

|                     |                                                                                |

## Abstract

Name of University: The University of Manchester Candidate's name: Wenyuan Wang Degree Title: Doctor of Philosophy Thesis Title: Operation, Control and Stability Analysis of Multi-terminal VSC-HVDC Systems Date: May 2015

Voltage source converter high voltage direct current (VSC-HVDC) technology has become increasingly cost-effective and technically feasible in recent years. It is likely to play a vital role in integrating remotely-located renewable generation and reinforcing existing power systems. Multi-terminal VSC-HVDC (MTDC) systems, with superior reliability, redundancy and flexibility over the conventional point-to-point HVDC, have attracted a great deal of attention globally. MTDC however remains an area where little standardisation has taken place, and a series of challenges need to be fully understood and tackled before moving towards more complex DC grids. This thesis investigates modelling, control and stability of MTDC systems.

DC voltage, which indicates power balance and stability of DC systems, is of paramount importance in MTDC control. Further investigation is required to understand the dynamic and steady-state behaviours of various DC voltage and active power control schemes in previous literature. This work provides a detailed comparative study of modelling and control methodologies of MTDC systems, with a key focus on the control of grid side converters and DC voltage coordination.

A generalised algorithm is proposed to enable MTDC power flow calculations when complex DC voltage control characteristics are employed. Analysis based upon linearised power flow equations and equivalent circuit of droop control is performed to provide further intuitive understanding of the steady-state behaviours of MTDC systems.