# FABRICATION AND CHARACTERISATION OF 3D MULTILAYER CIRCUITS FOR COMPACT MMIC APPLICATIONS

A thesis submitted to The University of Manchester for the degree of

Doctor of Philosophy

in the Faculty of Engineering and Physical Sciences

2015

Peter Kalemeera Balwayo Kyabaggu School of Electrical and Electronic Engineering

| LIST OF | F <b>F</b> IG | URES                                        | 6  |

|---------|---------------|---------------------------------------------|----|

| LIST OF | F TA          | BLES                                        | 16 |

| ABSTRA  | ACT.          |                                             | 18 |

| DECLA   | RATI          | ON                                          | 19 |

| COPYR   | IGHT          | с Statement                                 | 19 |

| Ackno   | WLE           | DGEMENTS                                    | 20 |

| LIST OF | F <b>P</b> UI | BLICATIONS                                  | 21 |

| Снарт   | er 1          | INTRODUCTION                                | 23 |

| 1.1     | KE            | Y AIMS AND OBJECTIVES OF THIS RESEARCH      | 26 |

| 1.2     | KE            | Y RESEARCH CONTRIBUTIONS                    | 27 |

| 1.3     | Тн            | ESIS OVERVIEW                               | 27 |

| Снарт   | er 2          | LITERATURE REVIEW                           | 29 |

| 2.1     | MN            | MIC TECHNOLOGY                              | 29 |

| 2.2     | Tr.           | ANSMISSION LINE THEORY                      | 31 |

| 2.3     | Тн            | IN-FILM MICROSTRIP (TFMS) TRANSMISSION LINE | 34 |

| 2.4     | Со            | PLANAR WAVEGUIDE TRANSMISSION LINE          | 35 |

| 2.5     | CP            | W TO THIN-FILM MICROSTRIP TRANSITION        | 36 |

| 2.6     | SC            | ATTERING PARAMETERS                         |    |

| 2.7     | Tr.           | ANSMISSION LINE EXTRACTED PARAMETERS        | 40 |

| 2.7     | .1            | Characteristic Impedance                    | 40 |

| 2.7     | .2            | Phase Velocity                              | 40 |

| 2.7     | .3            | Effective dielectric constant               | 41 |

| 2.7     | .4            | Dissipation Loss                            | 42 |

| 2.8     | Eli           | ECTRICAL LENGTH                             | 43 |

| 2.9     | Tr.           | ANSISTORS                                   | 43 |

| 2.9     | .1            | PN Junctions                                | 45 |

| 2.9     | .2            | Basic Principles of Transistors             | 46 |

| 2.9     | .3            | Field Effect Transistors (FET)              | 46 |

| Pri     | ncipl         | e of the GaAs Pseudomorphic HEMT            | 48 |

## Contents

| 2.9   | 9.4   | Small-Signal Analysis                                                               | 51  |

|-------|-------|-------------------------------------------------------------------------------------|-----|

| 2.10  | MIG   | CROWAVE DIODES AND POWER LIMITERS                                                   | 54  |

| 2.1   | 0.1   | Microwave PIN Diodes                                                                | 54  |

| 2.1   | 0.2   | Schottky Diodes                                                                     | 55  |

| 2.1   | 0.3   | Microwave Power Limiters                                                            | 61  |

| 2.1   | 0.4   | Comparisons between the PIN diode and Schottky diode limiters                       | 63  |

| Снарт | ER 3  | EXPERIMENTAL AND FABRICATION TECHNIQUES                                             | 64  |

| 3.1   | Elf   | ECTROMAGNETIC MODELLING                                                             | 64  |

| 3.2   | EXT   | TRACTION OF TRANSMISSION LINE PARAMETERS USING S-PARAMETERS                         | 68  |

| 3.2   | 2.1   | Calculation methodology for the Characteristic Impedance, Z <sub>0</sub>            | 68  |

| 3.2   | 2.2   | Calculation methodology for effective dielectric constant $\mathcal{E}_{effective}$ | 68  |

| 3.2   | 2.3   | Dissipation Loss                                                                    | 69  |

| 3.3   | ON    | -wafer Measurements                                                                 | 70  |

| 3.3   | 3.1   | DC Characterization                                                                 | 70  |

| 3.3   | 8.2   | Parameter Extraction in IC-CAP                                                      | 72  |

| 3.3   | 3.3   | Device Modelling Tool                                                               | 74  |

| 3.3   | 8.4   | On-wafer RF measurements                                                            | 75  |

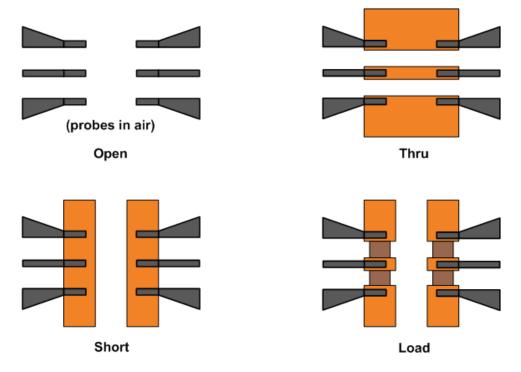

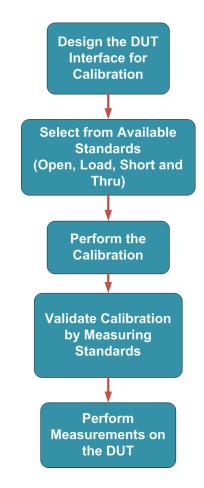

| 3.4   | NE    | IWORK ANALYSER CALIBRATION                                                          | 77  |

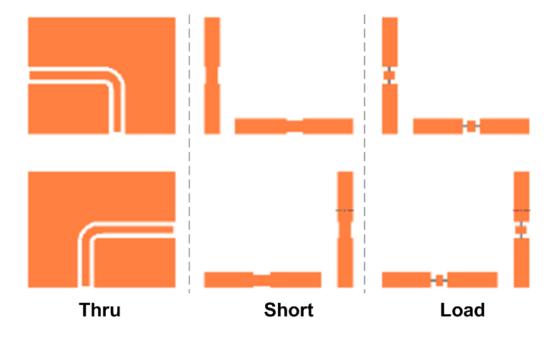

| 3.4   | l.1   | SOLT Calibration                                                                    | 78  |

| 3.4   | 1.2   | SOLR Calibration                                                                    | 78  |

| 3.4   | 1.3   | LMMR Calibration                                                                    | 79  |

| 3.5   | MU    | LTILAYER MMIC FABRICATION                                                           | 80  |

| 3.5   | 5.1   | Multilayer MMIC fabrication procedure for active and passive components             | 82  |

| 3.5   | 5.2   | Fabrication Challenges Encountered and Possible Solutions                           | 90  |

| Снарт | 'ER 4 | MMIC FABRICATION RESULTS AND DISCUSSIONS                                            | 96  |

| 4.1   | FAI   | BRICATION PROCESS CALIBRATIONS                                                      | 96  |

| 4.1   | .1    | Tooling Factor                                                                      | 96  |

| 4.1   | .2    | Photoresist and polyimide deposition                                                | 98  |

| 4.1   | .3    | Pre-Bake (Soft-Bake)                                                                | 101 |

| 4.1   | .4    | Polyimide Curing                                                                    | 102 |

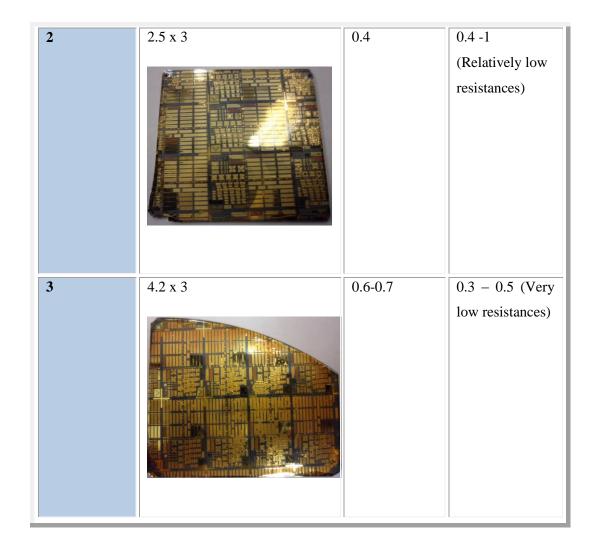

| 4.2  | MAS   | SK SET DESCRIPTION AND HISTORY                                                | 104  |

|------|-------|-------------------------------------------------------------------------------|------|

| 4.   | .2.1  | Description of Mask set Ver.2                                                 | 104  |

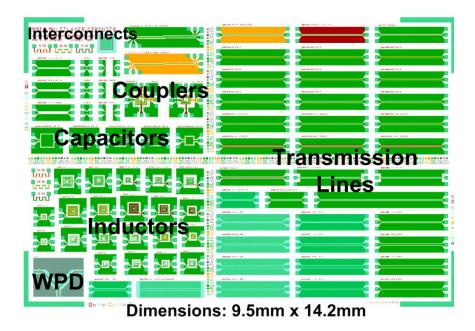

| 4.   | .2.2  | Description of Mask set Ver.5                                                 | 106  |

| 4.   | .2.3  | Interconnect Resistances                                                      | 108  |

| 4.   | .2.4  | Thin film GaAs Resistors                                                      | 109  |

| 4.   | .2.5  | Processing Validation Module (PVM)                                            |      |

| 4.   | .2.6  | Fabrication History for Mask set Ver.2                                        | 112  |

| 4.   | .2.7  | Fabrication History for Mask set Ver.5                                        | 114  |

| Снар | ter 5 | MICROWAVE CHARACTERISATION OF 3D MMIC COMPONENTS                              | .117 |

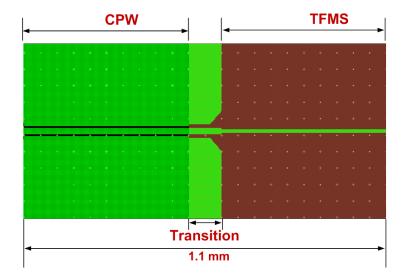

| 5.1  | CPV   | W TO THIN-FILM MICROSTRIP (TFMS) TRANSITION                                   | 117  |

| 5.   | 1.1   | Choosing CPW-to-TFMS Transition Transmission Line Design Parameters           | 117  |

| 5.   | .1.2  | Coplanar Waveguides                                                           |      |

| 5.   | .1.3  | CPW Transmission Line with a Footprint (Metal 2)                              | 119  |

| 5.   | 1.4   | Thin-Film Microstrip Line                                                     | 122  |

| 5.   | .1.5  | Transition Region                                                             | 124  |

| 5.   | 1.6   | Transition Effect on the Transmission Line                                    | 130  |

| 5.   | 1.7   | Choosing the Transition Design Parameters                                     | 131  |

| 5.   | 1.8   | Transition tapered region                                                     | 132  |

| 5.   | .1.9  | Transition length analysis in relation to integrated transmission line length | 132  |

| 5.   | 1.10  | CPW and TFMS Length Optimisations                                             | 134  |

| 5.   | 1.11  | Effects of the transition region length                                       | 135  |

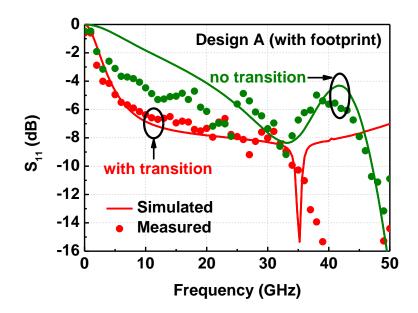

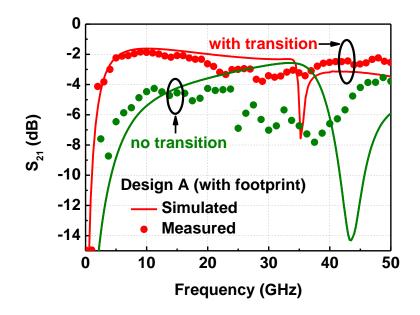

| 5.   | 1.12  | Comparison of Design A with and without transition region                     | 138  |

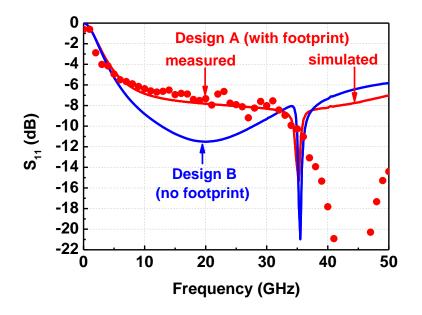

| 5.   | .1.13 | Comparison of Designs A and B                                                 | 140  |

| 5.   | 1.14  | Compact Transitions                                                           | 141  |

| 5.   | .1.15 | New Wideband Compact Transition Designs                                       | 145  |

| 5.2  | MM    | IIC-ACTIVE COMPONENTS AND CIRCUITS INTERCONNECTION                            | 150  |

| 5.   | .2.1  | pHEMT Characterisation                                                        | 150  |

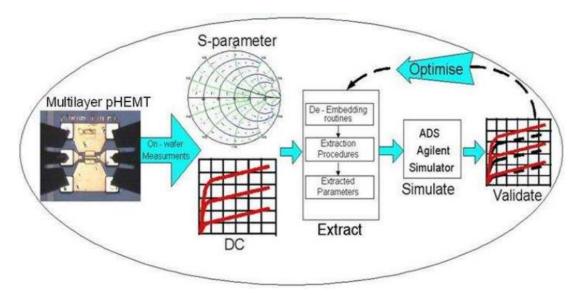

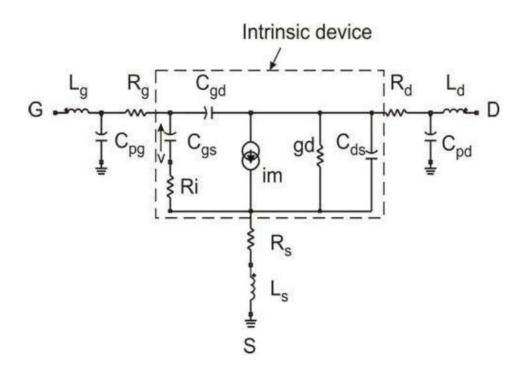

| 5.   | .2.2  | Multilayer pHEMT Modelling                                                    | 151  |

| 5.   | .2.3  | DC Characterisation a (0.5x200 µm <sup>2</sup> ) pHEMT                        | 151  |

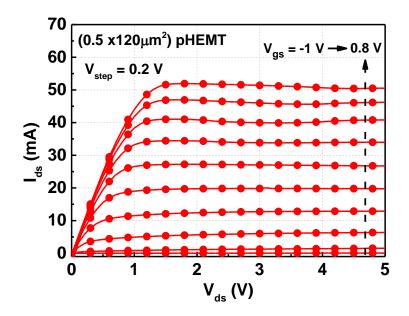

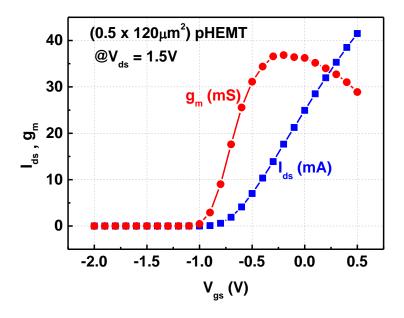

| 5.   | .2.4  | DC Characterisation of a (0.5x120 $\mu m^2)$ pHEMT                            | 153  |

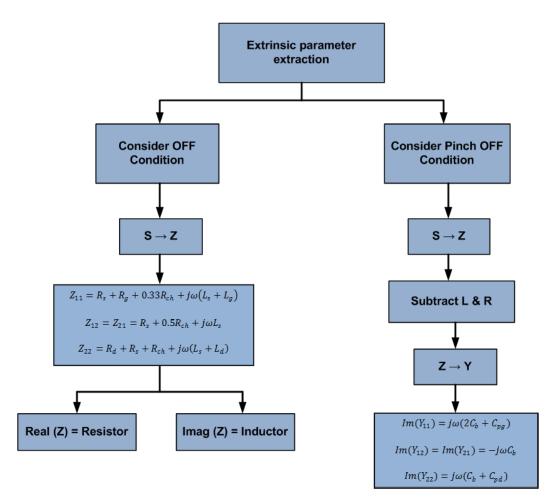

| 5.   | .2.5  | RF Parameter Extraction Procedure                                             | 155  |

| 5.2   | 2.6   | pHEMT DIODES                                                           | 171 |

|-------|-------|------------------------------------------------------------------------|-----|

| Сна   | АРТЕБ | <b>R 6</b> INTEGRATION OF MULTILAYER CPW PASSIVE COMPACTIVE COMPONENTS |     |

| 6.1   | MU    | LTILAYER MMIC LIMITERS                                                 | 179 |

| 6.1   | .1    | Limiter Mode of Operation                                              |     |

| 6.1   | .2    | MMIC Power Measurement Set-up                                          |     |

| 6.2   | A 1   | 0 GHz Low-noise Amplifier (LNA)                                        |     |

| 6.2   | 2.1   | Stability Considerations of an Amplifier                               |     |

| 6.2   | 2.2   | Stability of Small-Signal pHEMT Model                                  |     |

| 6.2   | 2.3   | Conjugate matched network design                                       |     |

| 6.2   | 2.4   | 10 GHz Low-Noise Amplifier (LNA) Layout design                         |     |

| Снарт | TER 7 | CONCLUSIONS AND FUTURE WORK                                            | 210 |

| 7.1   | Cor   | NCLUSIONS                                                              | 210 |

| 7.2   | Fut   | TURE WORK                                                              | 213 |

| Refer | ENCE  | S                                                                      | 215 |

# **List of Figures**

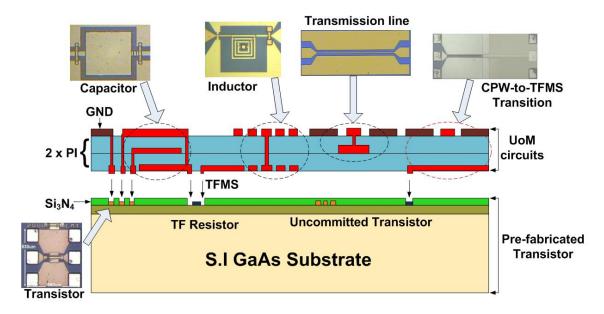

| Figure 2.1: Cross-sectional view of a 3-D MMIC incorporating passive CPW multilayer and GaAs pHEMT technologies [2, 31]                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

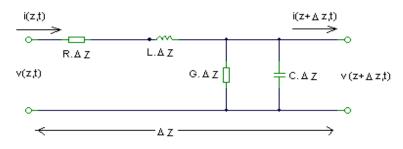

| Figure 2.2: Equivalent circuit of a transmission line [33]                                                                                                                                                                                                               |

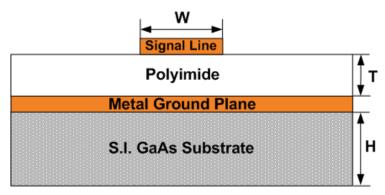

| Figure 2.3: Cross-sectional sketch of a thin-film microstrip                                                                                                                                                                                                             |

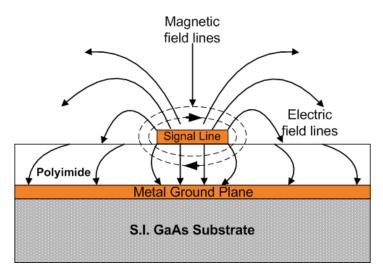

| Figure 2.4: Cross-sectional view of a thin-film microstrip transmission line showing electric and magnetic field patterns                                                                                                                                                |

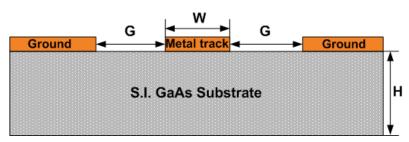

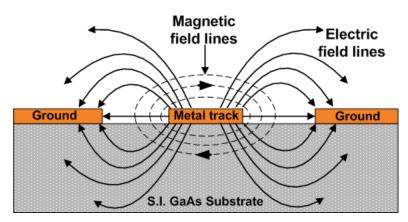

| Figure 2.5: Cross-sectional view of a conventional CPW transmission line                                                                                                                                                                                                 |

| Figure 2.6: Cross-sectional view of a conventional CPW transmission line showing electric and magnetic field patterns                                                                                                                                                    |

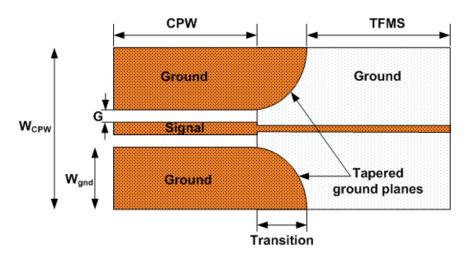

| Figure 2.7: Top view of a CPW to thin-film microstrip transition                                                                                                                                                                                                         |

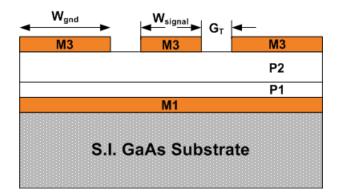

| Figure 2.8: Cross-sectional view of CPW to thin-film microstrip transition for figure 2.7                                                                                                                                                                                |

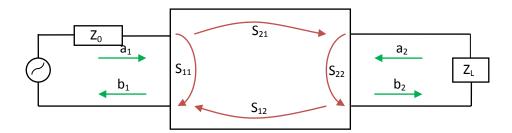

| Figure 2.9: Two-port network model                                                                                                                                                                                                                                       |

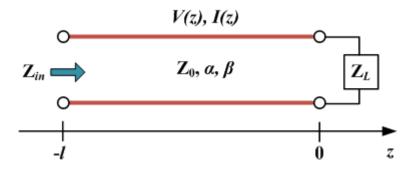

| Figure 2.10: A lossy transmission line terminated in the impedance $Z_L$ [30]42                                                                                                                                                                                          |

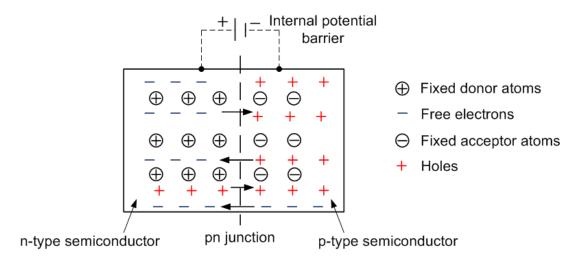

| Figure 2.11: Pattern of fixed and mobile charges in the region of a pn junction [48]                                                                                                                                                                                     |

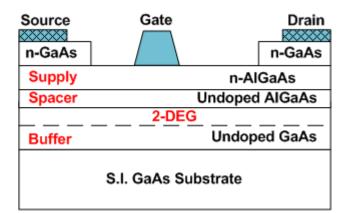

| Figure 2.12: Basic HEMT epitaxial layer schematic structure [53]47                                                                                                                                                                                                       |

| Figure 2.13: pHEMT epitaxial layer structure [53]                                                                                                                                                                                                                        |

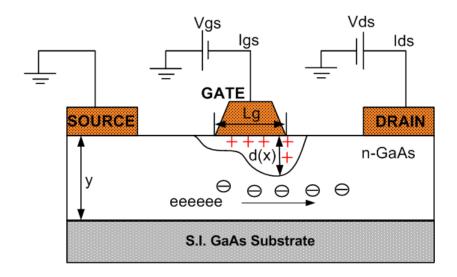

| Figure 2.14: Cross-sectional view of a GaAs MESFET under common source configuration [61].49                                                                                                                                                                             |

| Figure 2.15: A typical measured DC output characteristics of a pHEMT                                                                                                                                                                                                     |

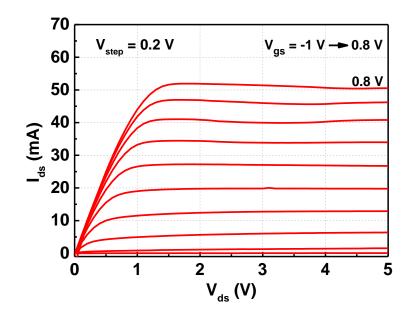

| Figure 2.16: Small-Signal equivalent circuit of a FET in common source configuration [55, 62]52                                                                                                                                                                          |

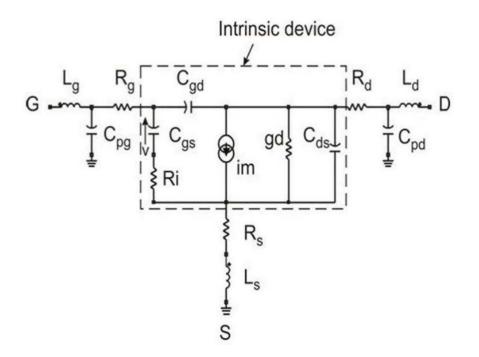

| Figure 2.17: PIN diode and the corresponding equivalent circuits [70]                                                                                                                                                                                                    |

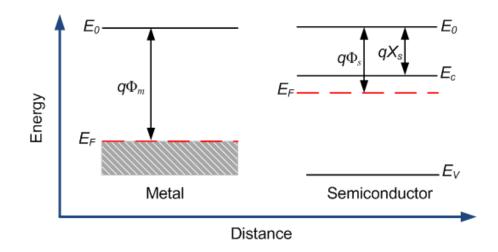

| Figure 2.18: Schematic energy band diagram for electrons in conduction bands of a metal and of a semiconductor [61, 71]                                                                                                                                                  |

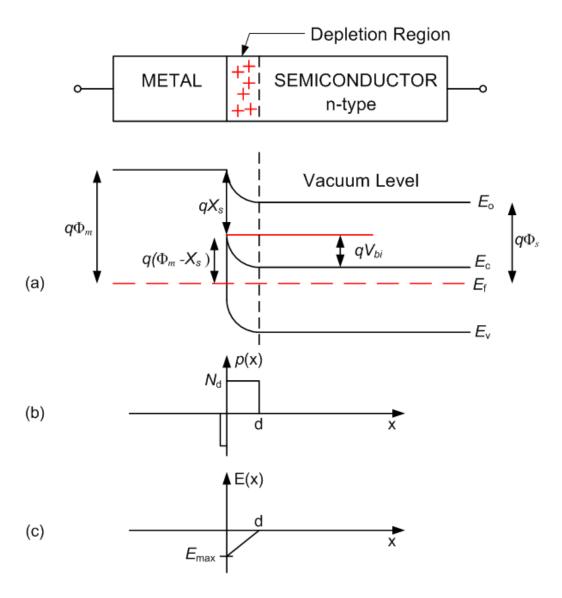

| Figure 2.19: (a) Energy band structure of the Schottky junction in thermal equilibrium in n-type semiconductor; (b) charge densities at the junction (negative component is the surface electron concentration on the metal); (c) electric field in the depletion region |

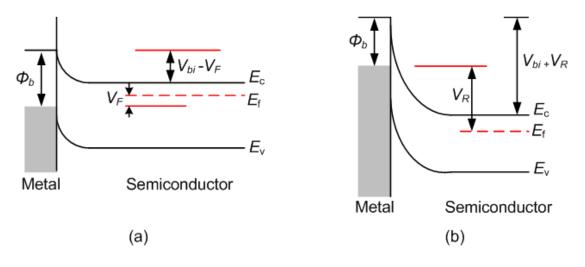

| Figure 2.20: Energy-band diagram for a metal-semiconductor system under (a) forward-biased condition; (b) reverse-biased condition [73]                                                                                                                                  |

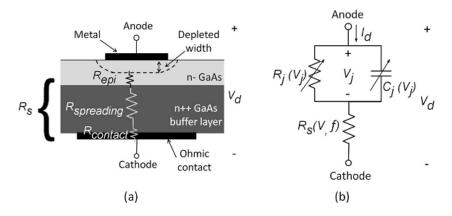

| Figure 2.21: A typical Schottky diode: (a) cross-sectional view; (b) equivalent circuit model but with R <sub>s</sub> is independent of voltage [73]                                                                                                                     |

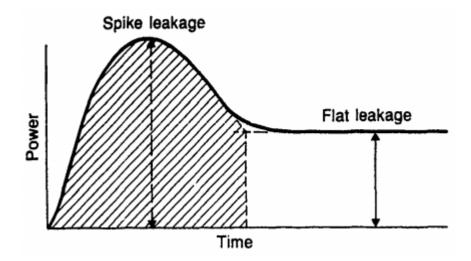

| Figure 2.22: Illustration of the Spike leakage [56]                                                                                                                                                                                                                      |

| Figure 3.1: Inserting the ports onto the device                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------|

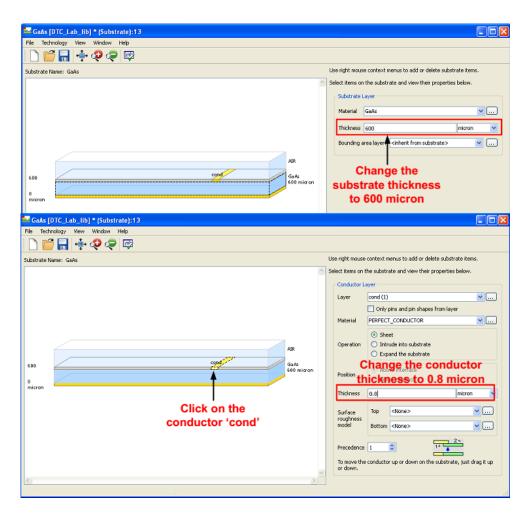

| Figure 3.2: Menu of substrate configuration in Momentum                                                                               |

| Figure 3.3: Setting-up the substrate and conductor layers                                                                             |

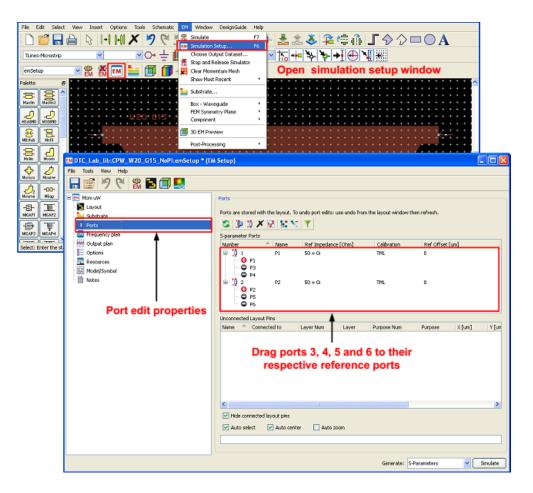

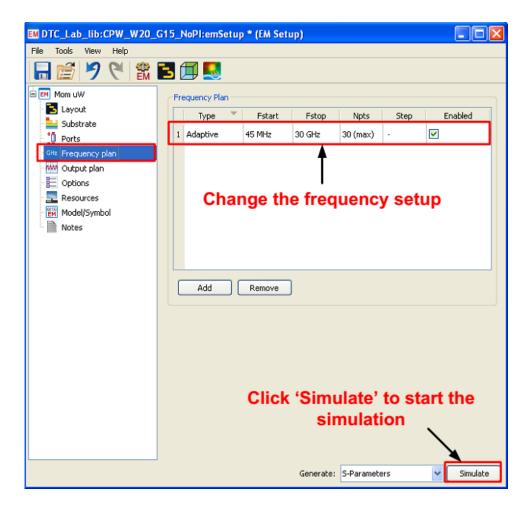

| Figure 3.4: Setting-up the Ports Editor                                                                                               |

| Figure 3.5: Setting-up the S-parameters simulation menu                                                                               |

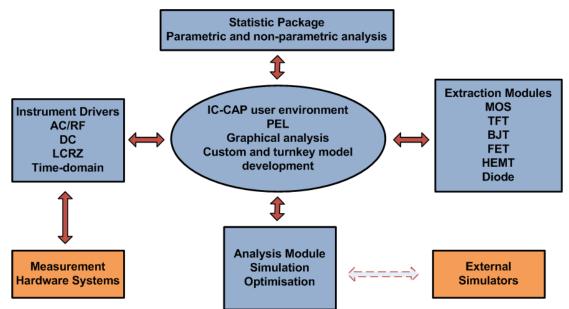

| Figure 3.6: Pictorial view of IC-CAP environment                                                                                      |

| Figure 3.7: Typical IC-CAP window showing the DUT and setups (blue oval) and the instrument server option (red oval)                  |

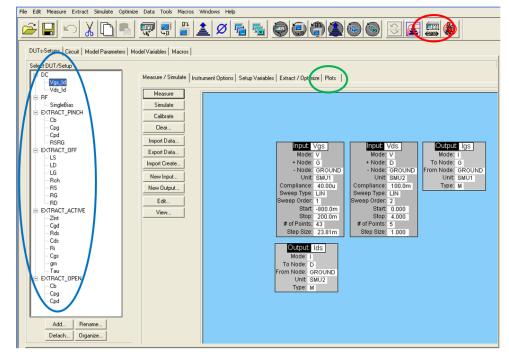

| Figure 3.8: Flow diagram of parameter extraction using IC-CAP [53]                                                                    |

| Figure 3.9: DUT tabs that allow options to define test circuits and corresponding parameters and local variables                      |

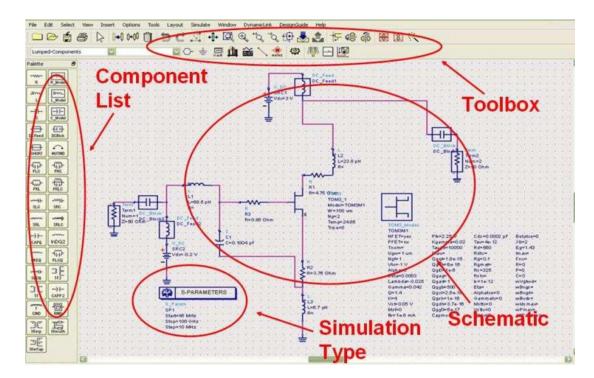

| Figure 3.10: ADS Schematic simulator user interface75                                                                                 |

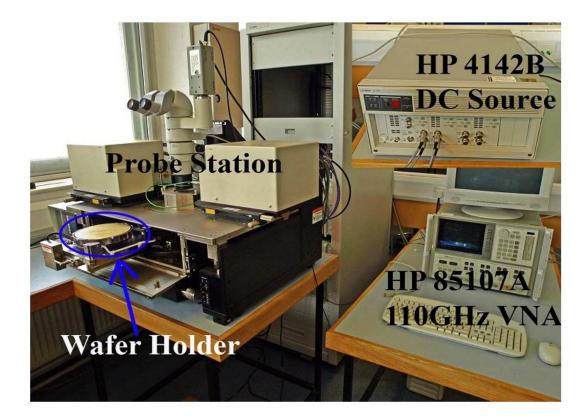

| Figure 3.11: Probe stations and VNA systems used in this work; (a) for frequencies up to 110 GHz and (b) for frequencies up to 50 GHz |

| Figure 3.12: Sketch of the GSG probes on Impedance Standard Substrate (ISS) standard77                                                |

| Figure 3.13: Schematic diagram of a calibration standard used in SOLT calibration [81]78                                              |

| Figure 3.14: Flow chart of the calibration procedure                                                                                  |

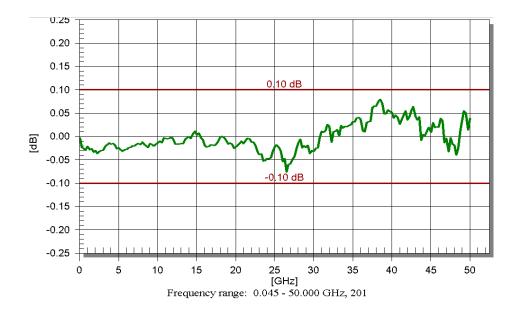

| Figure 3.15: Magnitude (S <sub>11</sub> ) corresponding to a good calibration80                                                       |

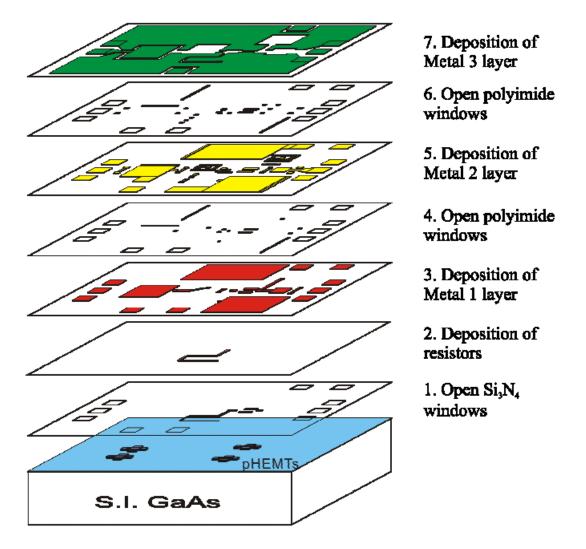

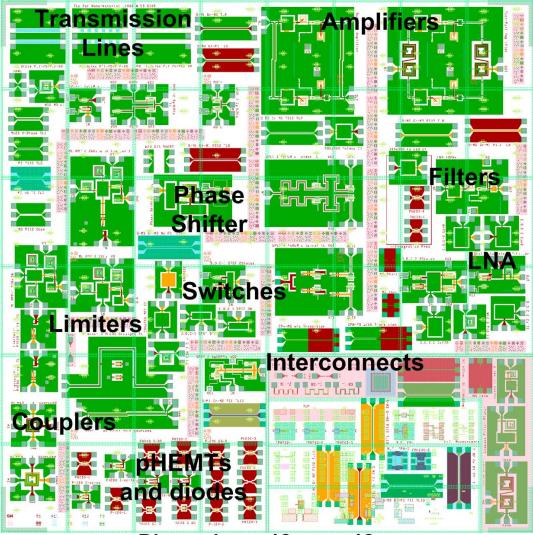

| Figure 3.16: 3D multilayer mask set (ver.5) layout                                                                                    |

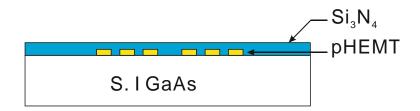

| Figure 3.17: GaAs substrate wafer with pHEMTs82                                                                                       |

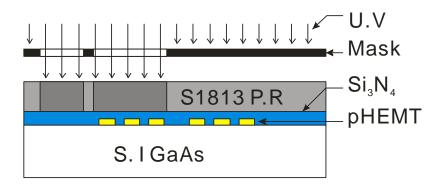

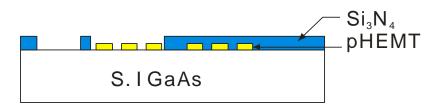

| Figure 3.18: Applying photoresist for photolithography to open $Si_3N_4$ window                                                       |

| Figure 3.19: GaAs wafer is opened $Si_3N_4$ window                                                                                    |

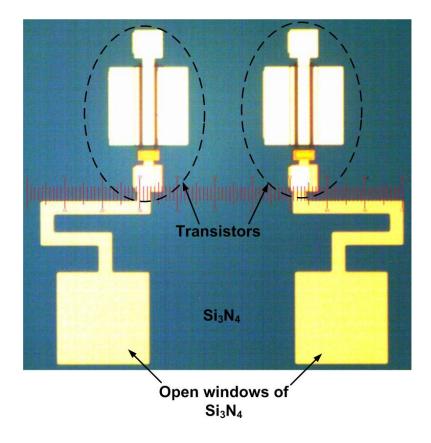

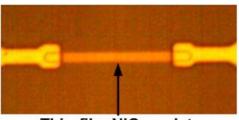

| Figure 3.20: Micrograph showing opened $Si_3N_4$ widows                                                                               |

| Figure 3.21: Thin film NiCr resistor deposition process; (a) photolithography, (b) NiCr deposition<br>and (c) NiCr lift-off           |

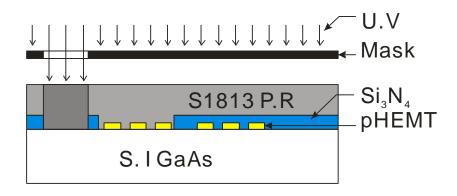

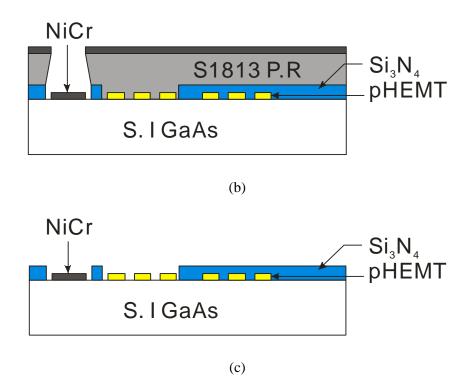

| Figure 3.22: Thin film NiCr resistor micrograph after deposition                                                                      |

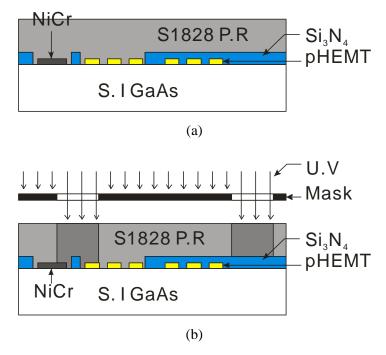

| Figure 3.23: Multilayer fabrication process: (a) photoresist deposition. (b) Photolithography86                                       |

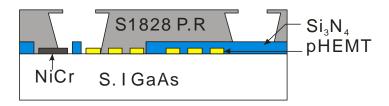

| Figure 3.24: Developed profile of photoresist ready for metal evaporation                                                             |

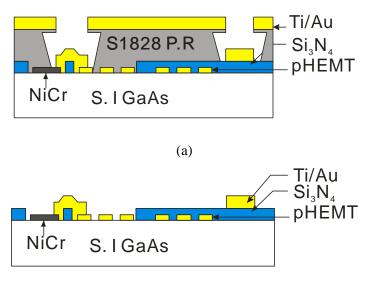

| Figure 3.25: Metal deposition: (a) Titanium and gold evaporated. (b) Metal lift-off                                                   |

| Figure 3.26: Micrograph of deposited Ti/Au on a developed pattern                                                                     |

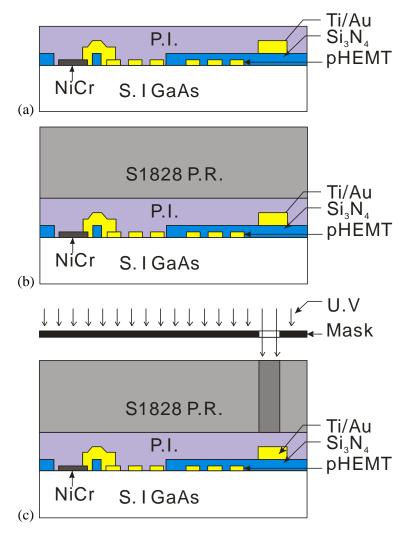

| Figure 3.27: Multilayer fabrication steps of polyimide deposition: (a) applying polyimide, (b) applying photoresist and (c) mask alignment and exposure |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

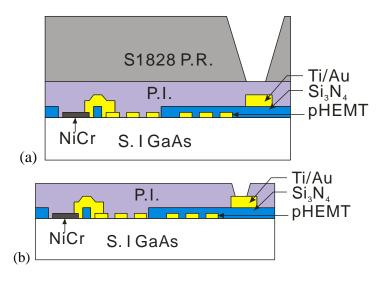

| Figure 3.28: Multilayer fabrication steps of polyimide deposition: (a) developed photoresist pattern and (b) etched away polyimide profile              |

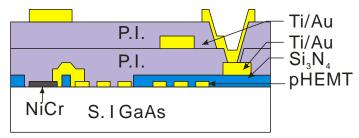

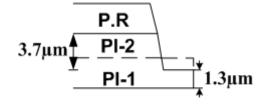

| Figure 3.29: Cross-sectional view of all multilayer fabricated layers                                                                                   |

| Figure 3.30: Polyimide surface after plasma etching off 1 µm91                                                                                          |

| Figure 3.31: Image of the desiccator setup [83]                                                                                                         |

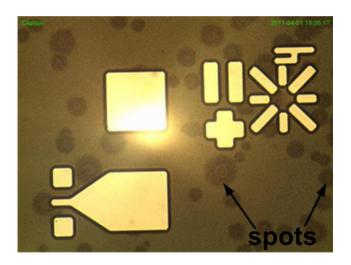

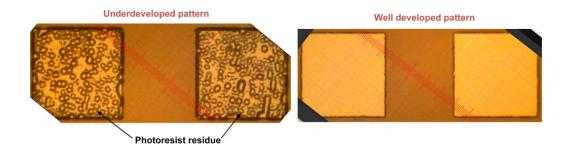

| Figure 3.32: Micrographs of an underdeveloped pattern and a well-developed photoresist pattern.93                                                       |

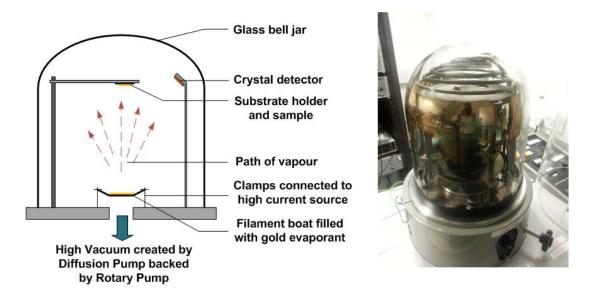

| Figure 3.33: Sketch and actual photo of the thermal evaporator94                                                                                        |

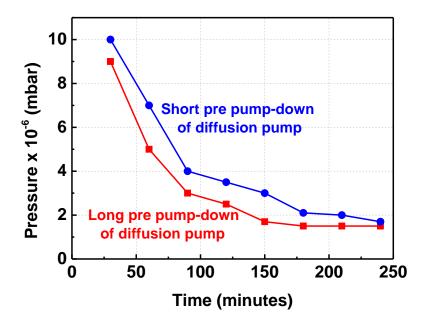

| Figure 3.34: Thermal evaporator pump-down                                                                                                               |

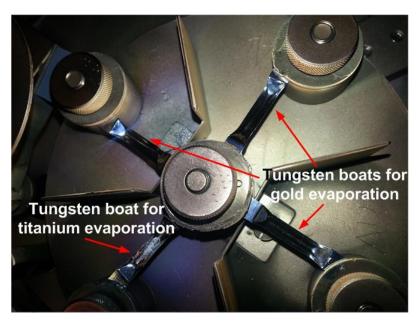

| Figure 3.35: Actual photo of tungsten boats on the electrodes inside the thermal evaporator95                                                           |

| Figure 3.36: Tungsten boats of different sizes                                                                                                          |

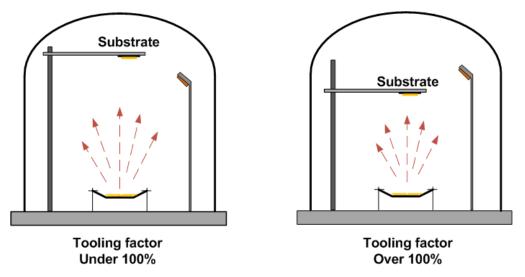

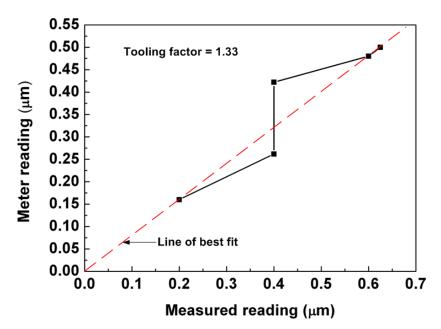

| Figure 4.1: Thermal evaporator with the substrate at different distances from crystal sensor96                                                          |

| Figure 4.2: Graph showing the tooling factor of the evaporated Ti/Au metals                                                                             |

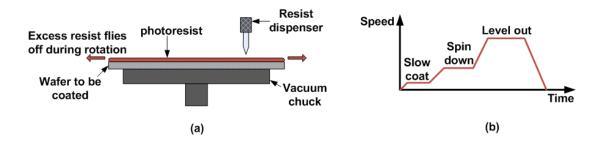

| Figure 4.3: Spin coating: (a) sketch of a wafer on vacuum chuck with photoresist being applied; (b) plot of speed against time                          |

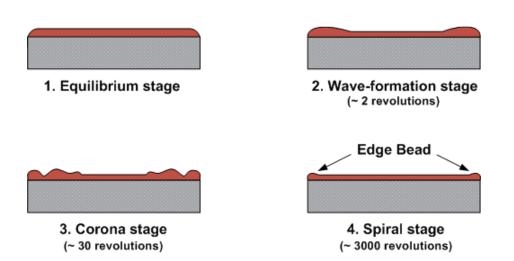

| Figure 4.4: Stages of photoresist coating [85]                                                                                                          |

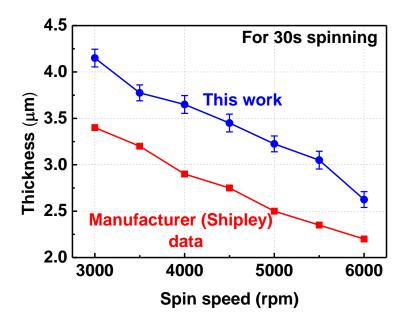

| Figure 4.5: The thickness of S1828 photoresist as a function of spinning speed                                                                          |

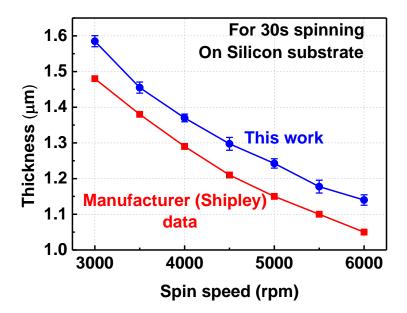

| Figure 4.6: The thickness of S1813 photoresist as a function of spinning speed on silicon substrate.                                                    |

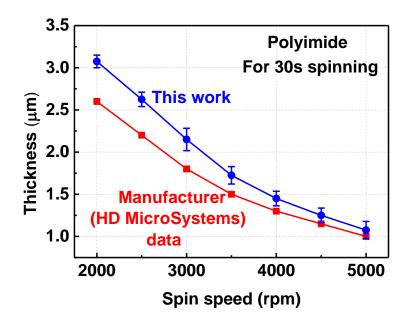

| Figure 4.7: The thickness of polyimide as a function of spinning speed on GaAs substrate100                                                             |

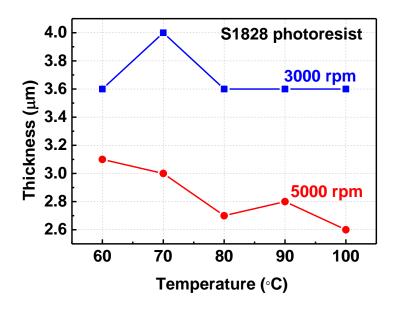

| Figure 4.8: S1828 photoresist thickness as a function of temperature for spin speeds 3000rpm and 5000rpm                                                |

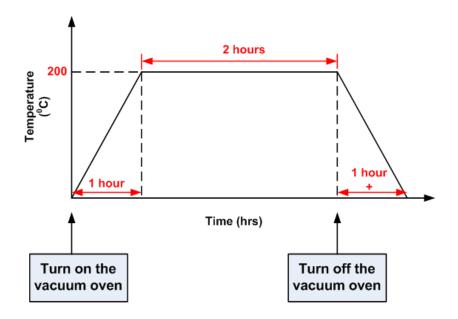

| Figure 4.9: Sketch of a plot of temperature against time for the post curing process102                                                                 |

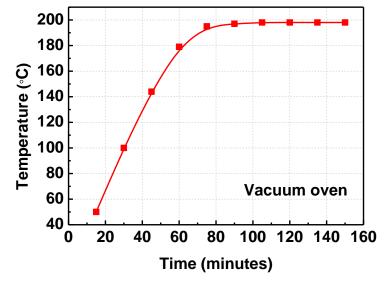

| Figure 4.10: Temperature rise rate of the vacuum oven                                                                                                   |

| Figure 4.11: Layout of a cell in mask set Ver.2 with passive components                                                                                 |

| Figure 4.12: Layout of a cell in mask set Ver.5 with both active and passive components                                                                 |

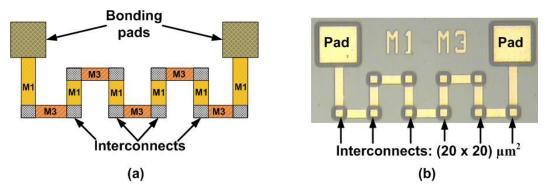

| Figure 4.13: Top view of the M1-M2 interconnect (a) sketch, (b) micrograph of the fabricated sample                                                     |

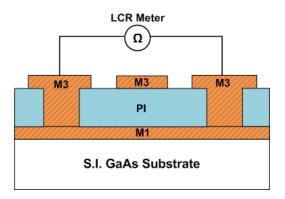

| Figure 4.14: Sketch of an M1 – M3 interconnect test                                                                                                     |

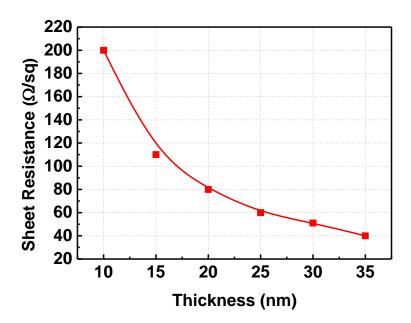

| Figure 4.15: Measured sheet resistance against NiCr film thickness                                                                                      |

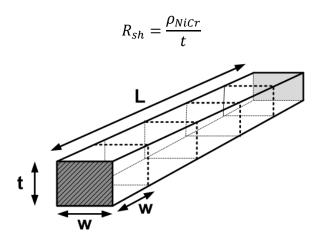

| Figure 4.16: 3D cross-sectional sketch of an integrated resistor                                                                            |

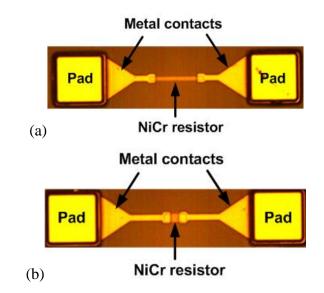

|---------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.17: Micrographs of thin film resistors: (a) 500 $\Omega$ , (b) 50 $\Omega$                                                         |

| Figure 4.18: Sketch of the Processing Validation Module (PVM)                                                                               |

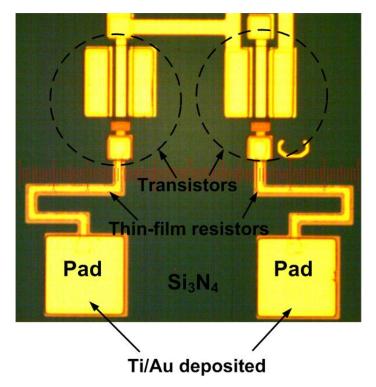

| Figure 4.19: Micrograph of the fabricated Processing Validation Module (PVM) area112                                                        |

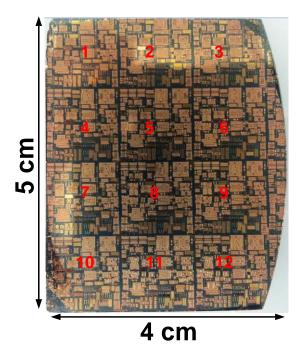

| Figure 4.20: Micrograph of fabricated wafer sample no. 4 containing twelve cells                                                            |

| Figure 4.21: Measured profile of polyimide following dry etching in the PVM area                                                            |

| Figure 5.1: Top view layout of the CPW-to-TFMS transition transmission line without probing pads                                            |

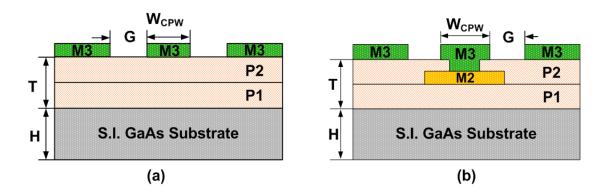

| Figure 5.2: Cross-sectional view of the multilayer Coplanar Waveguide (CPW) transmission lines<br>with (a) no footprint and (b) a footprint |

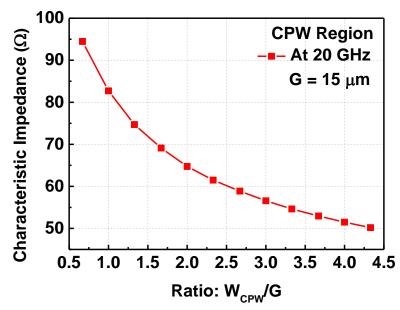

| Figure 5.3: Simulated impedances of CPW lines with different width and gap parameters118                                                    |

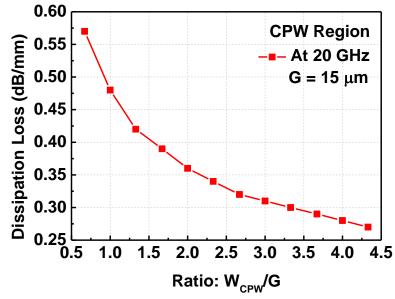

| Figure 5.4: Simulated dissipation losses of CPW lines with different width and gap parameters119                                            |

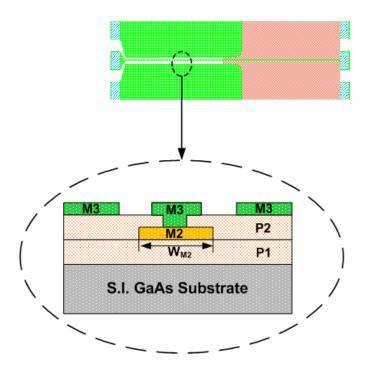

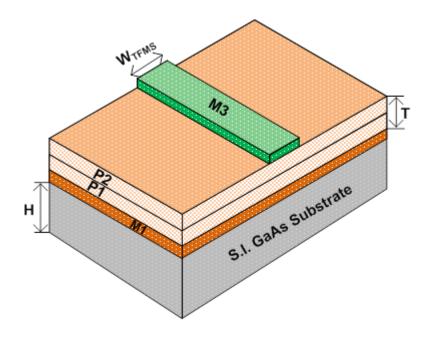

| Figure 5.5: Cross-sectional view of the CPW of the transition elaborating the width of Metal 2120                                           |

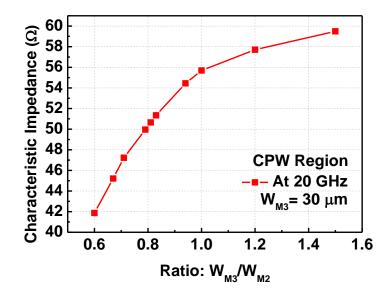

| Figure 5.6: Simulated impedances of CPW lines with different values of metal 2 widths120                                                    |

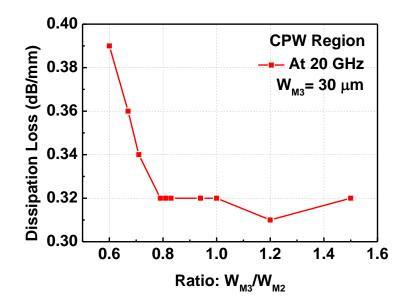

| Figure 5.7: Simulated dissipation losses of the CPW line with different ratios of metal 3 to metal 2 widths                                 |

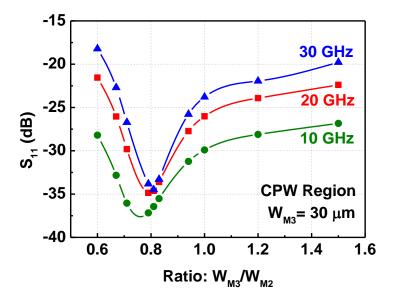

| Figure 5.8: Simulated S <sub>11</sub> parameters versus ratios of metal 3 to metal 2 widths for different frequencies                       |

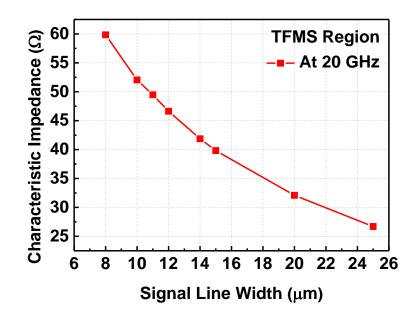

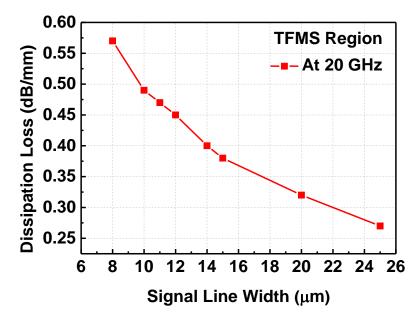

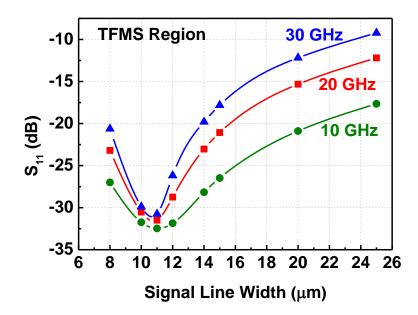

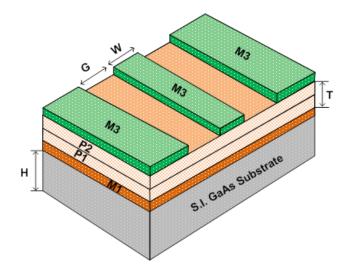

| Figure 5.9: 3D cross-sectional view of a thin-film microstrip line122                                                                       |

| Figure 5.10: Simulated characteristic impedances of thin-film micostrip lines with different signal width parameters                        |

| Figure 5.11: Simulated dissipation losses of thin-film micostrip lines with different signal width parameters                               |

| Figure 5.12: Simulated S <sub>11</sub> parameters of thin-film microstrip lines with different signal width parameters                      |

| Figure 5.13: 3D cross-sectional view of the transition region for a CPW-to-TFMS transition transmission line                                |

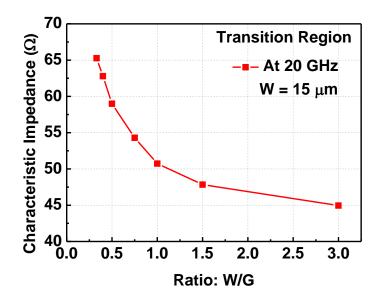

| Figure 5.14: Simulated characteristic impedances of the transition region with different width and gap parameters                           |

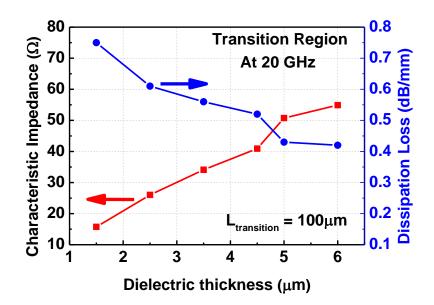

| Figure 5.15: Simulated characteristic impedance and dissipation loss of the transition against dielectric thickness                         |

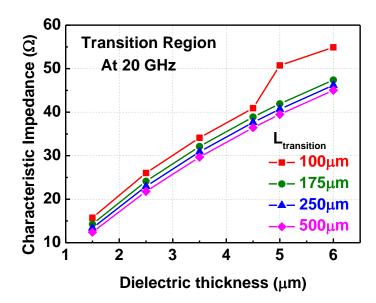

| Figure 5.16: Simulated characteristic impedance against dielectric thickness at different transition lengths                                |

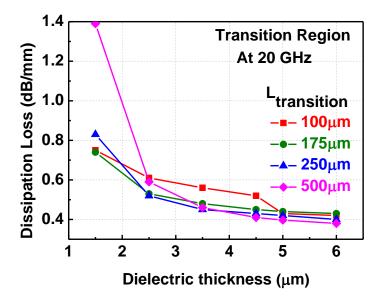

| Figure 5.17: | Simulated dissipation loss against dielectric thickness at different transition lengths.                                                                                                                                                                                                                                                                                                 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

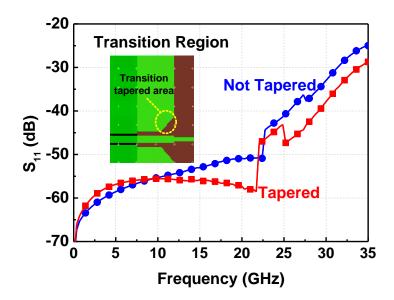

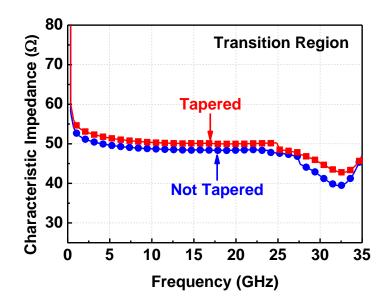

| Figure 5.18: | Simulated S <sub>11</sub> parameters of the transition region with and without tapered CPW ground planes                                                                                                                                                                                                                                                                                 |

| Figure 5.19: | Simulated dissipation losses of the transition region, with and without tapered CPW ground planes                                                                                                                                                                                                                                                                                        |

| Figure 5.20: | Simulated characteristic impedances of the transition region with and without tapered CPW ground planes                                                                                                                                                                                                                                                                                  |

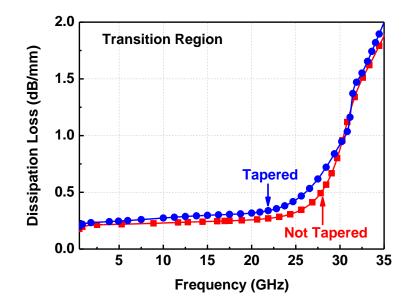

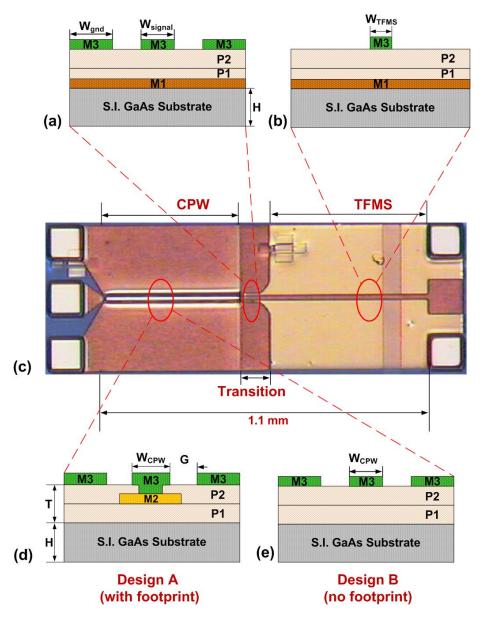

| Figure 5.21: | CPW to thin-film microstrip transition structure (a) cross-sectional view of the transition, (b) cross-sectional view of the TFMS end which does not have a footprint, (c) top view of the fabricated structure with bonding pads (d) cross-sectional view of the CPW line end with a footprint (design A) and (e) cross-sectional view of the CPW line end with no footprint (design B) |

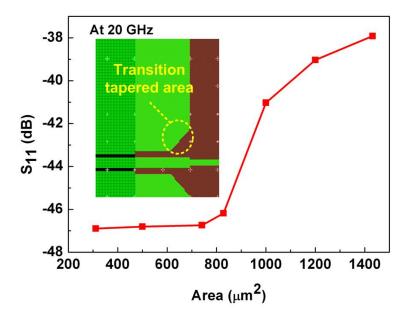

| Figure 5.22: | Simulated return loss of the transition tapered section at different CPW ground plane areas for design B (without a footprint)                                                                                                                                                                                                                                                           |

| Figure 5.23: | Return loss simulation analysis of the ratio of the transmission line length to transition length                                                                                                                                                                                                                                                                                        |

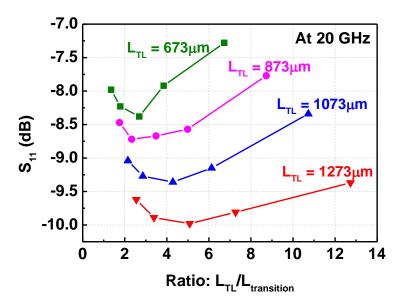

| Figure 5.24: | Insertion loss simulation analysis of the ratio of the transmission line length to transition length                                                                                                                                                                                                                                                                                     |

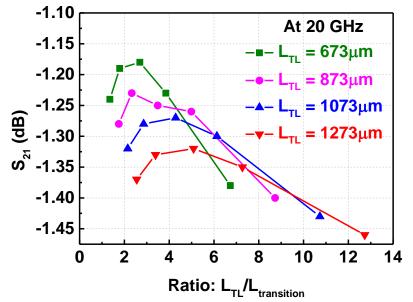

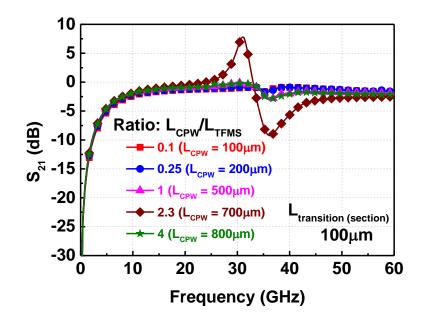

| Figure 5.25: | Simulation analysis of return loss for various ratios of the CPW length section to the TFMS line length section ( $L_{CPW}$ // $L_{TFMS}$ ) for a transition length of 100µm (design B).<br>                                                                                                                                                                                             |

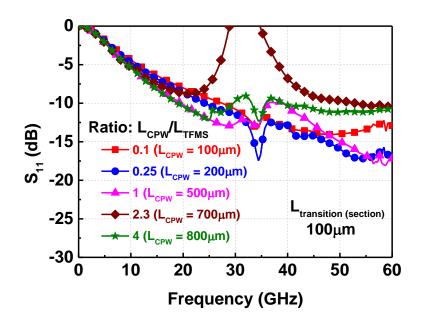

| Figure 5.26: | Simulation analysis of insertion loss for various ratios of the CPW length section to the TFMS line length section ( $L_{CPW}/L_{TFMS}$ ) for a transition length of 100µm (design B)                                                                                                                                                                                                    |

| Figure 5.27: | Simulation analysis of return losses of design B with different transition section lengths                                                                                                                                                                                                                                                                                               |

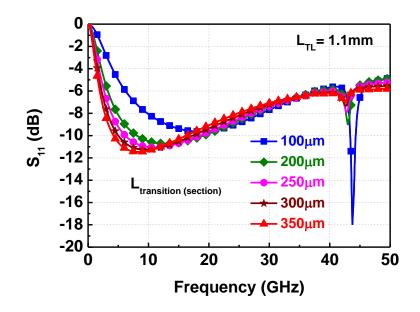

| Figure 5.28: | Simulation analysis of insertion losses of design B with different transition section lengths                                                                                                                                                                                                                                                                                            |

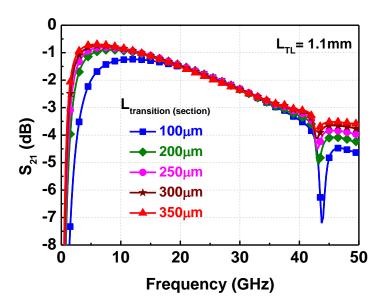

| Figure 5.29: | Simulation analysis of dissipation losses of design B with different transition section lengths                                                                                                                                                                                                                                                                                          |

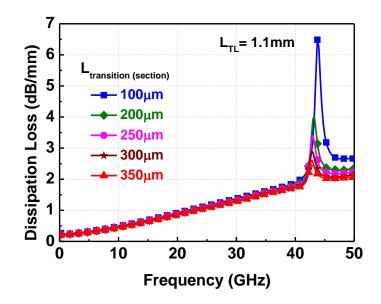

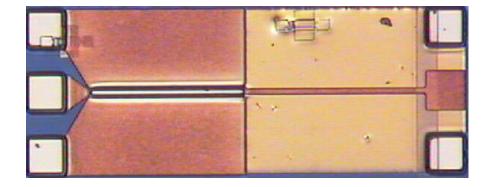

| Figure 5.30: | Fabricated design A, transmission line structure with no transition region                                                                                                                                                                                                                                                                                                               |

| Figure 5.31: | Measured and simulated return loss for design A, with and without a transition section.<br>                                                                                                                                                                                                                                                                                              |

| Figure 5.32: | Measured and simulated insertion loss for design A with and without a transition section                                                                                                                                                                                                                                                                                                 |

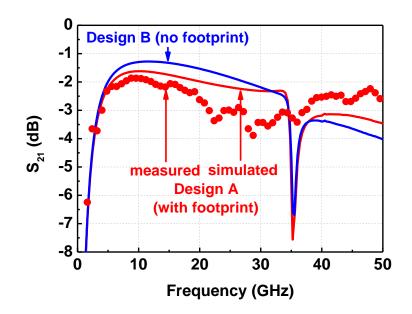

| Figure 5.33: | Measured and simulated return loss for design A and the simulated data for design B.<br>                                                                    |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.34: | Measured and simulated insertion loss for design A and the simulated data for design B                                                                      |

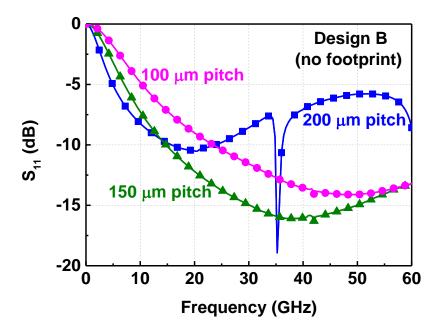

| Figure 5.35: | Simulated return loss comparison for design B with 200 µm, 150 µm and 100 µm signal-to-ground (pitch) spacing                                               |

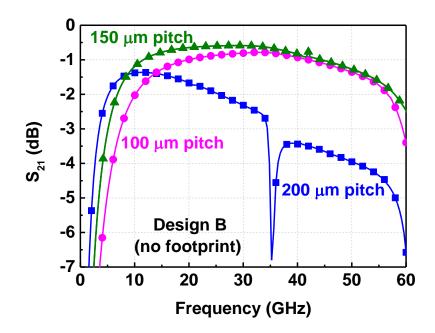

| Figure 5.36: | Simulated insertion loss comparison for design B with 200 $\mu$ m, 150 $\mu$ m and 100 $\mu$ m signal-to-ground (pitch) spacing                             |

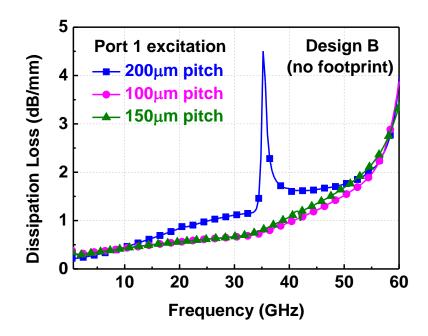

| Figure 5.37: | Simulated dissipation loss for design B with 100 $\mu$ m, 150 $\mu$ m and 200 $\mu$ m signal-to-<br>ground (pitch) spacings at port 1 (CPW end) excitation  |

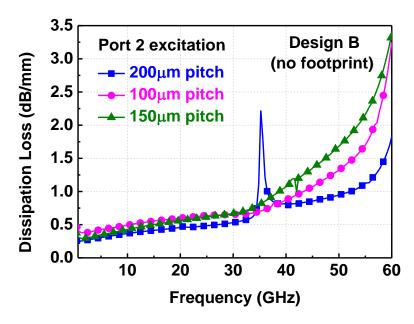

| Figure 5.38: | Simulated dissipation loss for design B with 100 $\mu$ m, 150 $\mu$ m and 200 $\mu$ m signal-to-<br>ground (pitch) spacings at Port 2 (TFMS end) excitation |

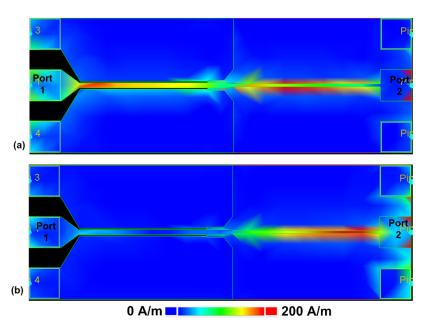

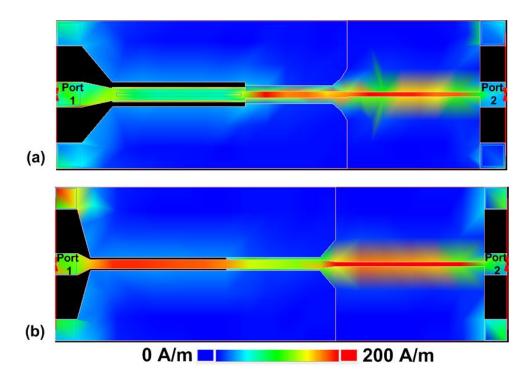

| Figure 5.39: | EM current distribution in CPW-to-TFMS transition at 20 GHz with; (a) Port 1 excitation and (b) Port 2 excitation (design B with 200 µm pitch)              |

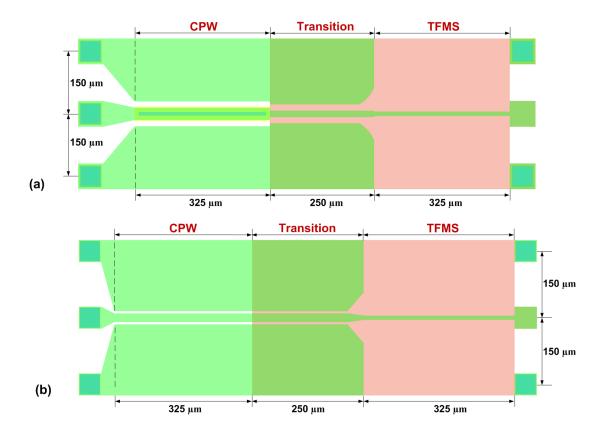

| Figure 5.40: | Top view of the new compact CPW-to-TFMS transition design structures; (a) design A (with a footprint) and (b) design B (no footprint)145                    |

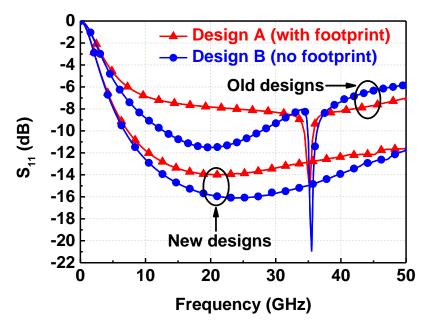

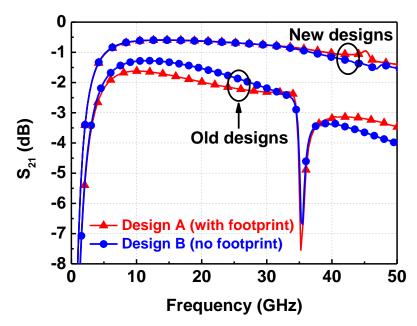

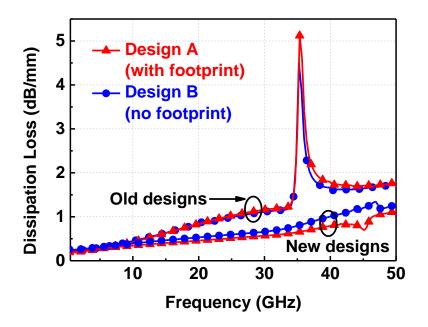

| Figure 5.41: | Simulated return losses for old and new A and B transmission line structure designs.<br>                                                                    |

| Figure 5.42: | Simulated insertion losses for old and new A and B transmission line structure designs                                                                      |

| Figure 5.43: | Simulated dissipation losses for old and new designs A and B transmission line structures                                                                   |

| Figure 5.44: | E.M current distribution at 20 GHz with port 1 excitation of; (a) new compact design A (with footprint) and (b) new compact design B (no footprint)         |

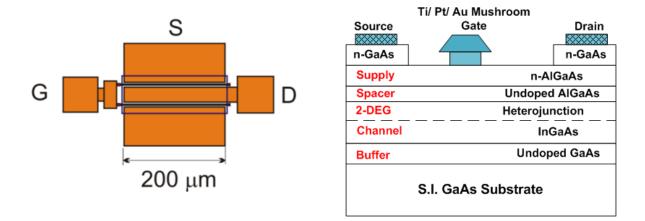

| Figure 5.45: | Top and cross-sectional view of the AlGaAs/InGaAs pHEMT                                                                                                     |

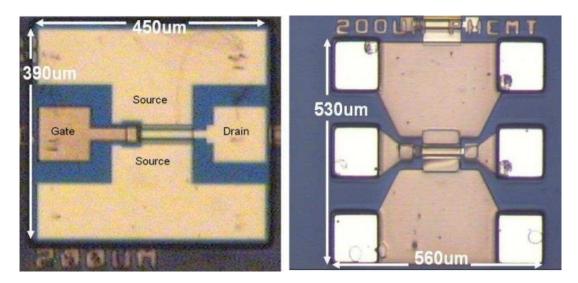

| Figure 5.46: | Micrographs of the fabricated pre- (virgin) and post-multilayer processed (0.5x200µm <sup>2</sup> ) pHEMTs                                                  |

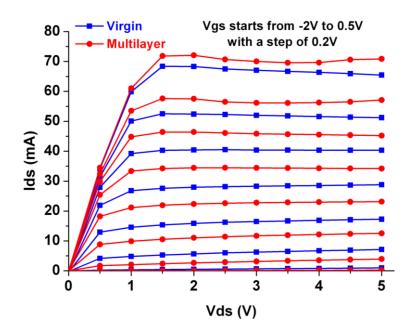

| Figure 5.47: | Comparison of output characteristics between virgin and multilayer $(0.5 \times 200 \ \mu m^2)$ pHEMTs                                                      |

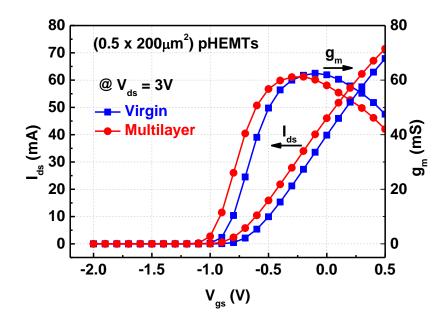

| Figure 5.48: | Comparison of measured $I_{ds}$ and $g_m$ characteristics between virgin and multilayer (0.5×200 $\mu$ m <sup>2</sup> ) pHEMTs                              |

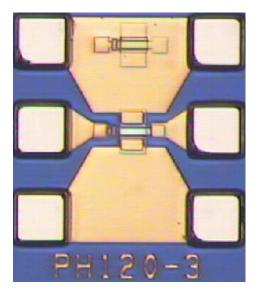

| Figure 5.49: | Micrograph of a fabricated multilayer (0.5x120 µm <sup>2</sup> ) pHEMT153                                                                                   |

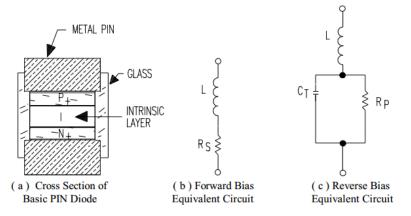

| Figure 5.50: | Measured output characteristics of the fabricated two-gate fingered (0.5 x 120 $\mu$ m <sup>2</sup> ) pHEMT                                                 |

| Figure 5.51: | Measured transfer characteristics of the fabricated two-gate fingered (0.5 x 120 $\mu$ m <sup>2</sup> ) pHEMT                                                      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.52: | Small-signal equivalent circuit of a pHEMT in a common source configuration [53].<br>                                                                              |

| Figure 5.53: | Flow chart for determining pHEMT extrinsic parameters                                                                                                              |

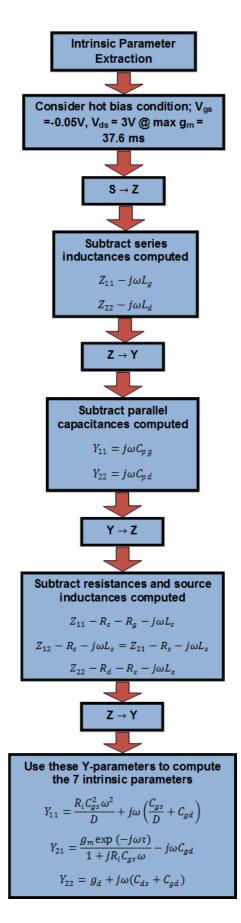

| Figure 5.54: | Flowchart for the intrinsic parameter extraction of the pHEMT159                                                                                                   |

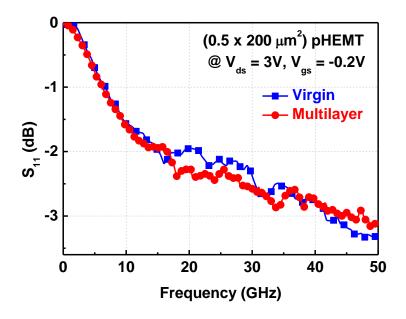

| Figure 5.55: | $S_{11}$ parameter comparison between a virgin and a multilayer (0.5×200 $\mu$ m <sup>2</sup> ) pHEMT                                                              |

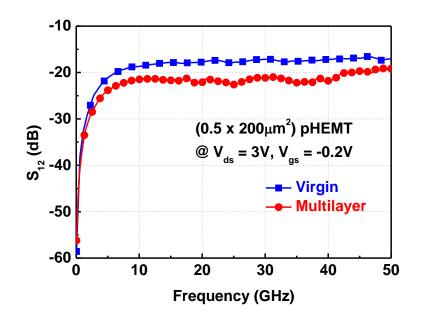

| Figure 5.56: | $S_{12}$ parameter comparison between a virgin and a multilayer (0.5×200 $\mu m^2)$ pHEMT162                                                                       |

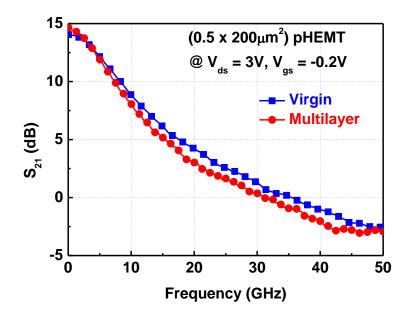

| Figure 5.57: | $S_{21}$ parameter comparison between a virgin and a multilayer (0.5×200 $\mu$ m <sup>2</sup> ) pHEMT.<br>                                                         |

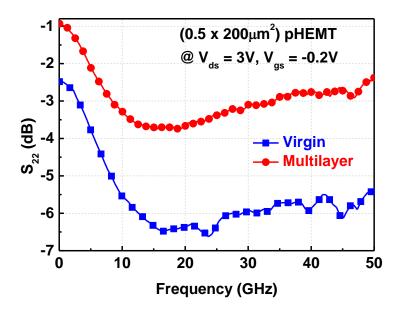

| Figure 5.58: | $S_{22}$ parameter comparison between a virgin and a multilayer (0.5×200 $\mu m^2)$ pHEMT                                                                          |

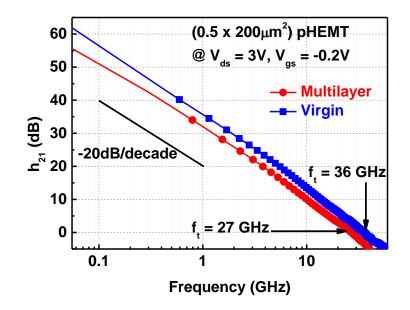

| Figure 5.59: | Comparison of $h_{21}$ parameters for a virgin and a multilayer (0.5×200 $\mu$ m <sup>2</sup> ) pHEMT.<br>                                                         |

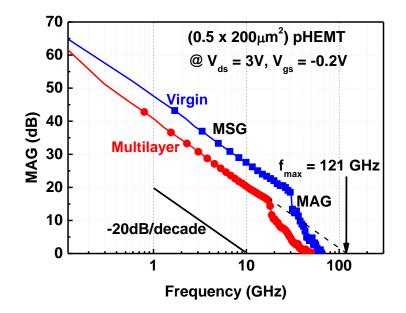

| Figure 5.60: | Comparison of MAG for a virgin and a multilayer (0.5×200 $\mu m^2)$ pHEMT164                                                                                       |

| Figure 5.61: | Schematic model of the small-signal pi circuit for the fabricated (0.5 x 120 $\mu$ m <sup>2</sup> ) GaAs pHEMT                                                     |

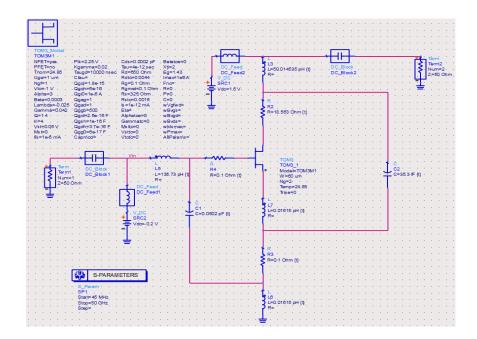

| Figure 5.62: | Schematic equivalent circuit of the TOM3 large-signal model for the (0.5 x 120 $\mu$ m <sup>2</sup> )<br>GaAs pHEMT                                                |

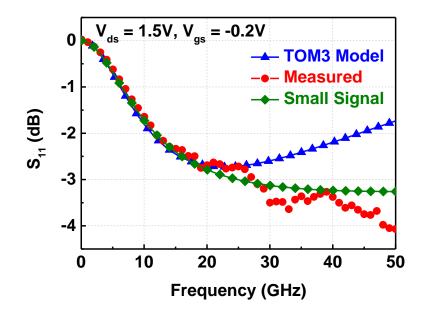

|              | Comparison of $S_{11}$ parameters between the TOM3 large-signal model, small-signal model and the measured (0.5 x 120 $\mu$ m <sup>2</sup> ) GaAs pHEMT            |

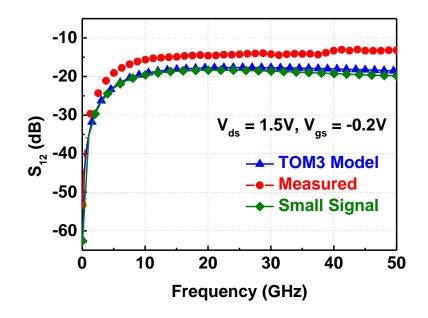

| Figure 5.64: | Comparison of $S_{12}$ parameters between the TOM3 large-signal model, small-signal model and the measured (0.5 x 120 $\mu$ m <sup>2</sup> ) GaAs pHEMT            |

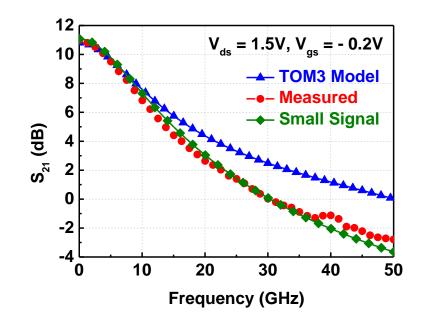

| Figure 5.65: | Comparison of $S_{21}$ parameters between the TOM3 large-signal model, small-signal model and the measured (0.5 x 120 $\mu$ m <sup>2</sup> ) GaAs pHEMT            |

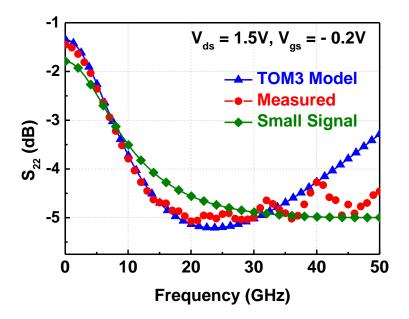

| Figure 5.66: | Comparison of $S_{22}$ parameters between the TOM3 large-signal model, small-signal model and the measured (0.5 x 120 $\mu$ m <sup>2</sup> ) GaAs pHEMT            |

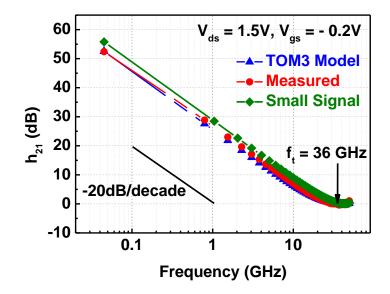

| Figure 5.67: | Comparison of current gain, $h_{21}$ between the TOM3 large-signal model, small-signal model and the measured (0.5 x 120 $\mu$ m <sup>2</sup> ) GaAs pHEMT         |

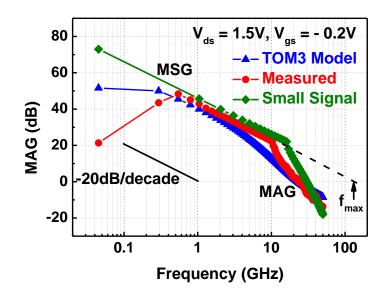

| Figure 5.68: | Comparison of maximum available gain, MAG between the TOM3 large-signal model, small-signal model and the measured (0.5 x 120 $\mu$ m <sup>2</sup> ) GaAs pHEMT170 |

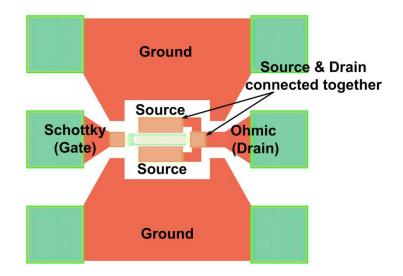

| Figure 5.69: | Layout of a multilayer pHEMT diode172                                                                                                                              |

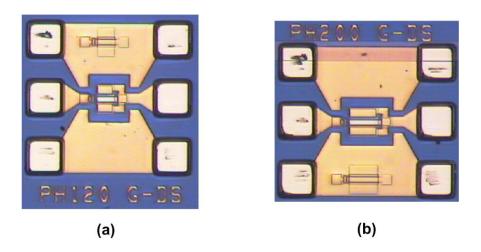

| -             | Micrograph of fabricated pHEMT diodes; (a) 0.5 μm x (2x60) μm diode. (b) 0.5 μm x (2x100) μm diode                            |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|

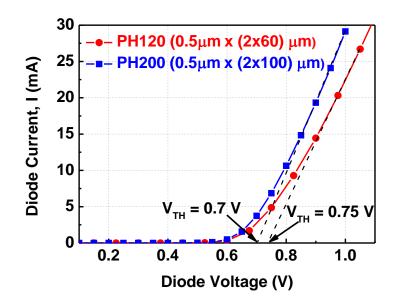

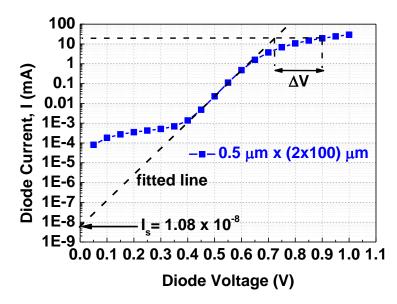

| Figure 5.71:  | Measured I-V characteristics of the pHEMT diodes173                                                                           |

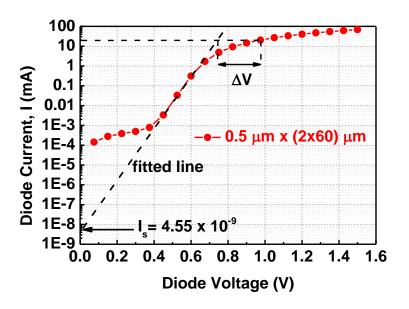

| Figure 5.72:  | Measured I-V characteristics of the 0.5 µm x (2x60) µm PH diode in a semi log scale.<br>                                      |

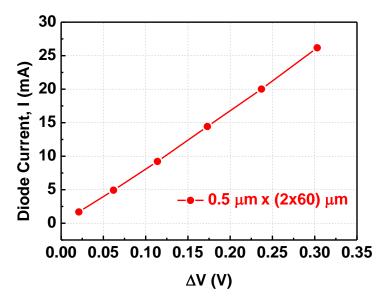

|               | Diode current against a change in diode voltage of the 0.5 µm x (2x60) µm PH diode,<br>using data from Figure 4.90            |

| -             | Measured I-V characteristics of the 0.5 µm x (2x100) µm PH diode in a semi log scale                                          |

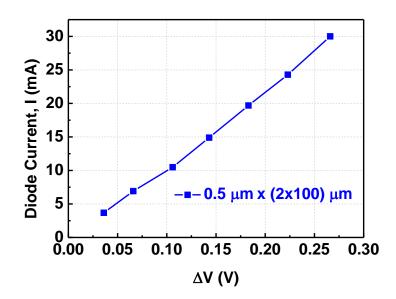

| -             | Diode current against a change in diode voltage of the 0.5 μm x (2x100) μm PH diode,<br>using data from Figure 4.92175        |

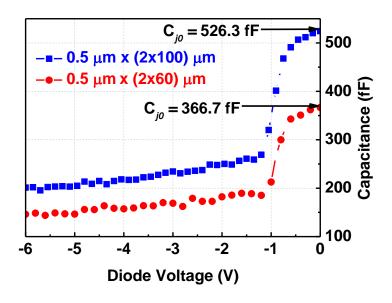

| -             | Measured C-V characteristics of both 0.5 μm x (2x100) μm and 0.5 μm x (2x60) μm<br>pHEMT diodes                               |

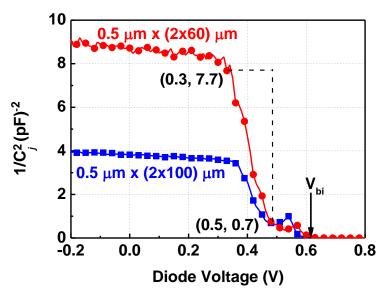

| -             | Measured C-V characteristics of both 0.5 µm x (2x100) µm and 0.5 µm x (2x60) µm pHEMT diodes showing the built-in voltage     |

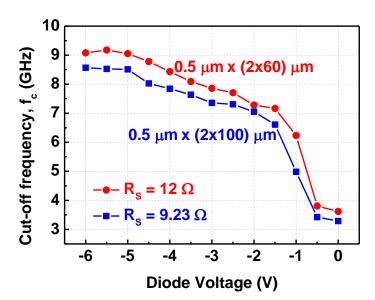

| •             | Cut-off frequency of both 0.5 µm x (2x100) µm and 0.5 µm x (2x60) µm pHEMT diodes                                             |

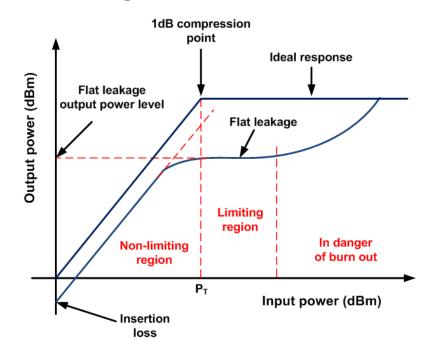

| Figure 6.1: T | ypical output power profile of a microwave power limiter                                                                      |

| Figure 6.2: S | chematic circuit of an ideal limiter                                                                                          |

| Figure 6.3: S | chematic circuit of an ideal limiter with LC components                                                                       |

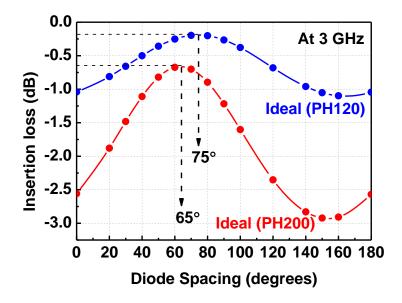

| Figure 6.4: S | imulated insertion loss of both the ideal (PH200) and (PH120) limiters at 3 GHz181                                            |

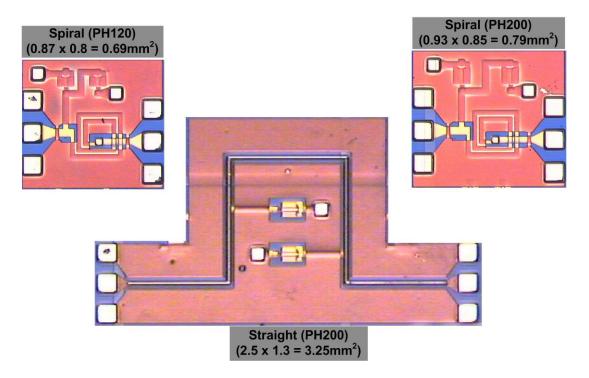

| •             | Aicrographs of the fabricated spiral (PH120), straight (PH200) and spiral (PH200)<br>limiters                                 |

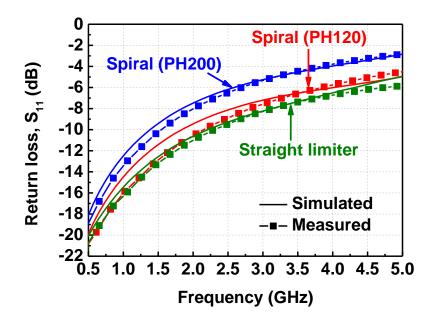

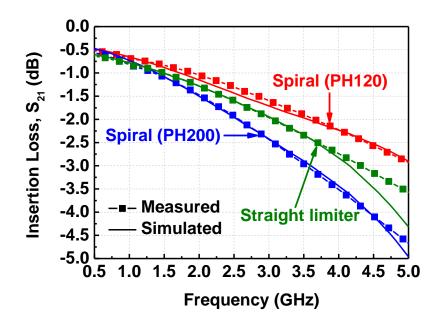

| -             | Comparison of measured and simulated return loss of three MMIC limiter circuits at zero biasing conditions                    |

| -             | Comparison of measured and simulated insertion loss of three MMIC limiter circuits at zero biasing conditions                 |

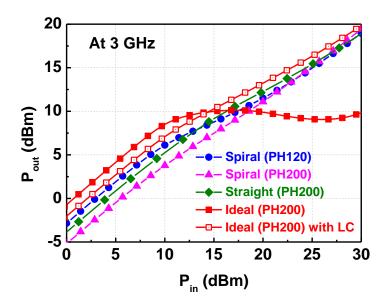

| -             | imulated output power response of the three MMIC limiter circuits as well as the ideal limiter circuit at 3GHz                |

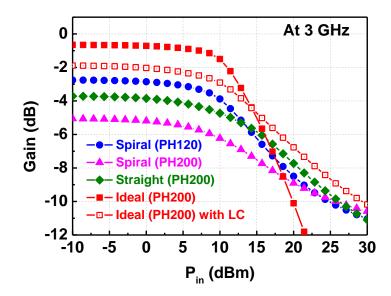

| -             | imulated gain response of three MMIC limiter circuits as well as the ideal limiter circuit at 3GHz                            |

| Figure 6.10:  | Simplified block diagram measurement set-up for the MMIC power limiters                                                       |

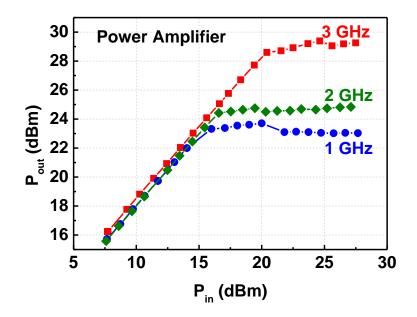

| e             | Comparison of measured output power response of a Mini-Circuits coaxial power<br>amplifier (ZHL-42W) at different frequencies |

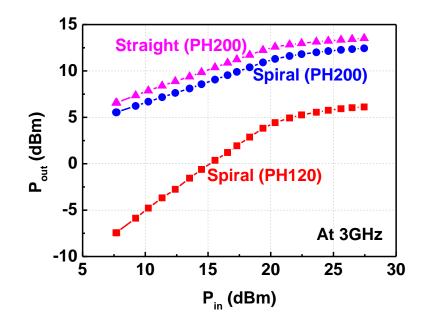

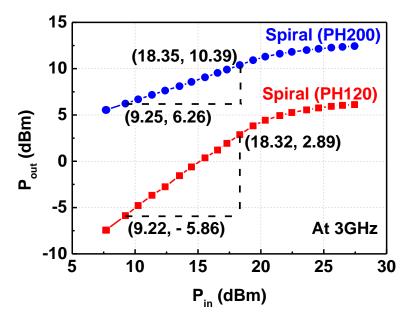

| Figure 6.12: | Measured output power response of three MMIC limiter circuits at 3GHz                                                               | 89  |

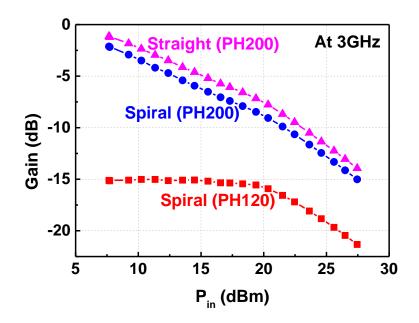

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.13: | Measured gain response of three MMIC limiter circuits at 3GHz                                                                       | 90  |

| Figure 6.14: | Slopes of the measured output power response of the spiral (PH120) and spiral (PH200) limiters at 3GHz                              | .91 |

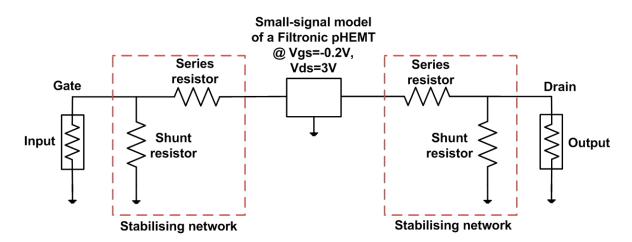

| Figure 6.15: | Small-signal pHEMT model with the stabilising resistor networks at both input and output ports                                      | .95 |

| Figure 6.16: | Small-signal model pHEMT without stabilising resistors1                                                                             | .96 |

| Figure 6.17: | Small-signal pHEMT model with stabilising resistors1                                                                                | .96 |

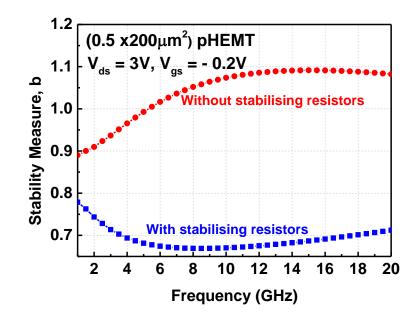

| Figure 6.18: | Stability factor of the small-signal model for a GaAs pHEMT, with and without stabilising resistors1                                | .97 |

| Figure 6.19: | Stability measure of the small-signal model for a GaAs pHEMT, with and without stabilising resistors                                | .97 |

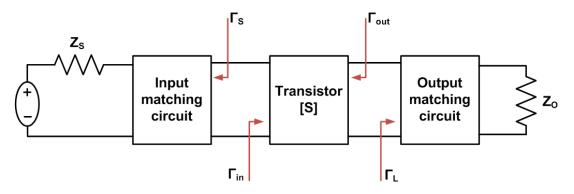

| Figure 6.20: | Block diagram for a single stage amplifier design1                                                                                  | 98  |

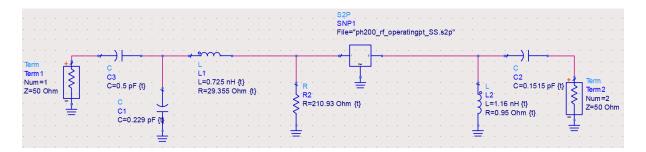

| Figure 6.21: | Schematic of a conjugate matched 10GHz low-noise amplifier with ideal L and C2                                                      | :01 |

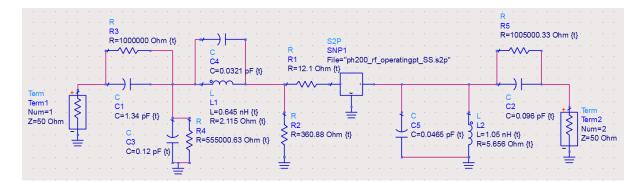

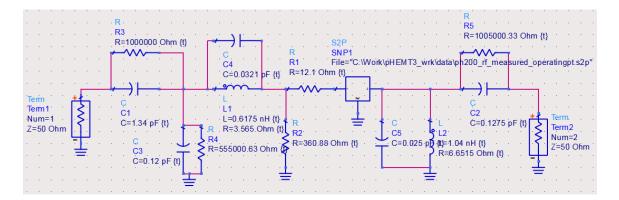

| Figure 6.22: | Schematic of a conjugate matched 10GHz low-noise amplifier with parasitics associated with the passive components (lossy L and C)2  | 201 |

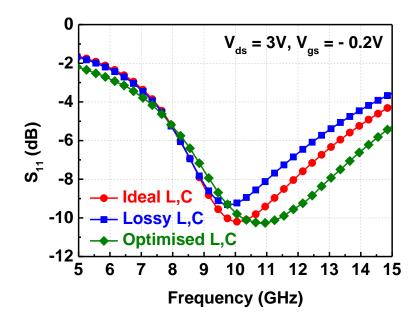

| Figure 6.23: | Comparison of the simulated $S_{11}$ parameters of a 10 GHz low-noise amplifier using ideal, lossy and optimised passive components | 202 |

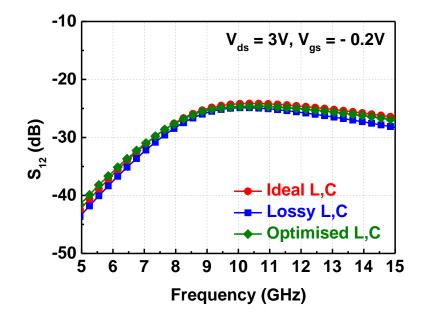

| Figure 6.24: | Comparison of the simulated $S_{12}$ parameters of a 10 GHz low-noise amplifier using ideal, lossy and optimised passive components | 202 |

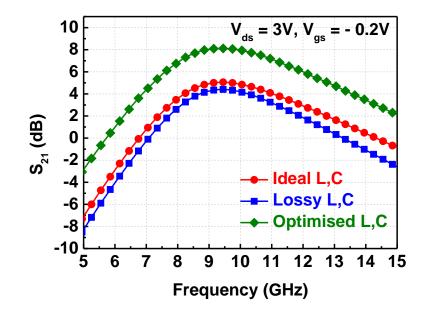

| Figure 6.25: | Comparison of the simulated $S_{21}$ parameters of a 10 GHz low-noise amplifier using ideal, lossy and optimised passive components | 203 |

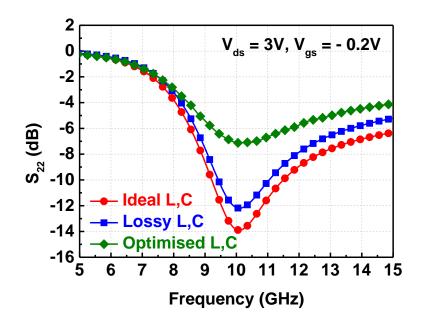

| Figure 6.26: | Comparison of the simulated $S_{22}$ parameters of a 10 GHz low-noise amplifier using ideal, lossy and optimised passive components | 203 |

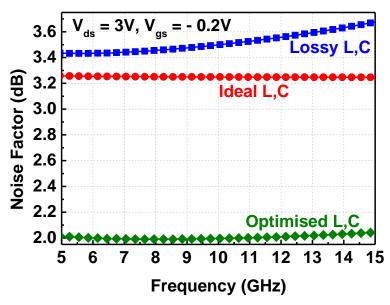

| Figure 6.27: | Comparison of the noise factors of a 10 GHz low-noise amplifier using ideal, lossy<br>and optimised passive components              | 204 |

| Figure 6.28: | Schematic circuit of a 10GHz LNA                                                                                                    | :05 |

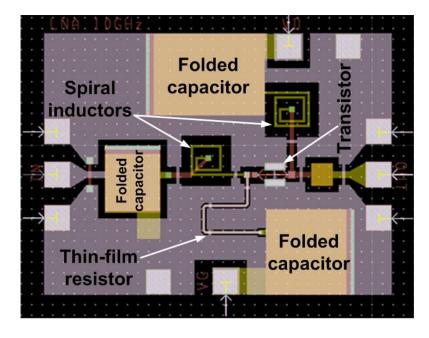

| Figure 6.29: | Layout design of a multilayer 3D MMIC 10 GHz LNA.                                                                                   | :05 |

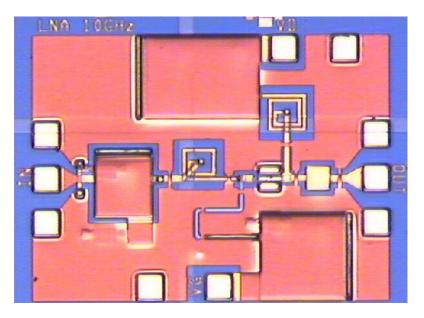

| Figure 6.30: | Micrograph of a fabricated multilayer 3D MMIC 10 GHz LNA.                                                                           | :06 |

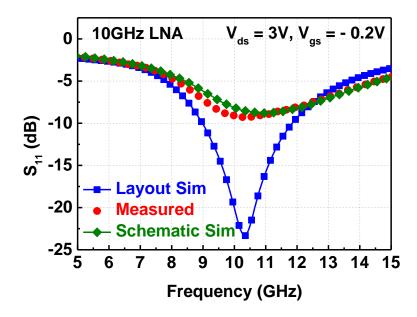

| Figure 6.31: | Return loss comparison for measured, layout simulation and schematic simulation of<br>the 10 GHz LNA.                               |     |

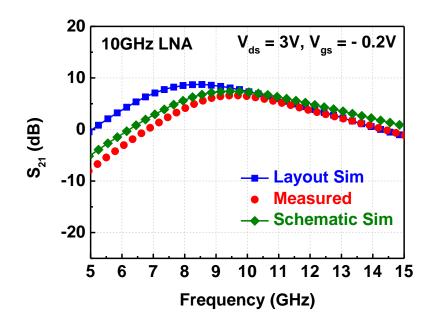

| Figure 6.32: | Gain comparison for measured, layout simulation and schematic simulation of the 10 GHz LNA.                                         |     |

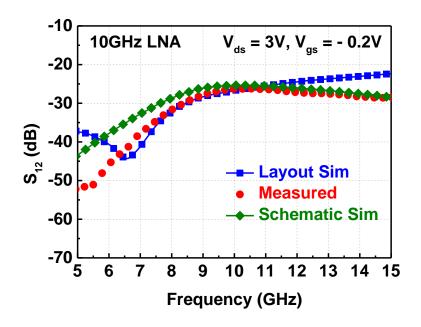

| Figure 6.33: | gure 6.33: Reverse isolation comparison for measured, layout simulation and schematic |     |  |  |

|--------------|---------------------------------------------------------------------------------------|-----|--|--|

|              | simulation of the 10 GHz LNA.                                                         | 207 |  |  |

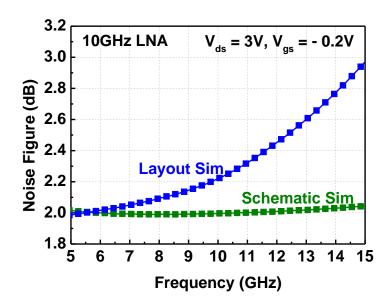

| Figure 6.34: | Noise figure comparison for layout simulation and schematic simulation of the 10      |     |  |  |

|              | GHz LNA.                                                                              | 208 |  |  |

## List of Tables

| Table 2.1: Advantages and disadvantages of MMIC and Hybrid MIC [30]                                                             |

|---------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2: Relationships of small-signal parameters to physical properties of FET [53, 62]                                      |

| Table 3.1: Descriptions of ADS simulation types [53].    74                                                                     |

| Table 4.1: Vacuum oven temperature rise.    103                                                                                 |

| Table 4.2: Various component structures designed in Mask set Ver.2.    105                                                      |

| Table 4.3: Various component structures designed in Mask set Ver.5.                                                             |

| Table 4.4: History of fabricated multilayer samples using Mask set ver.2.                                                       |

| Table 4.5: Measured polyimide and thin metal thicknesses measurement on PVM for sample 2 of         Mask set of Mask set Ver.2. |

| Table 4.6: Measured interconnect metal resistances on test sample 2 of Mask set Ver.2                                           |

| Table 4.7: Measured interconnect metal resistances and resistors for sample no. 4 of Mask set         Ver.5.                    |

| Table 4.8: Thickness measurement results for sample 4 of Mask set Ver.5.                                                        |

| Table 5.1: Dimensions for the CPW to TFMS transition transmission line for designs A and B [17]                                 |

| Table 5.2: Design parameter comparison between old and new A and B transmission line structure designs.                         |

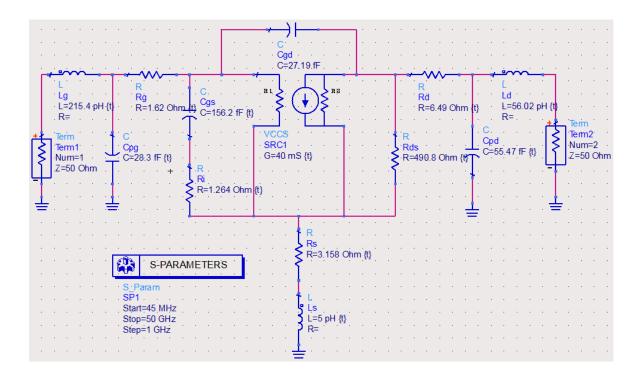

| Table 5.3: Extracted small-signal parameters for the multilayer (0.5x200µm <sup>2</sup> ) pHEMT161                              |

| Table 5.4: Extracted small-signal parameters for the fabricated (0.5 x 120 $\mu$ m <sup>2</sup> ) GaAs pHEMT167                 |

| Table 5.5: Summary of parameters from IV and CV pHEMT diodes characteristics                                                    |

| Table 6.1: Ideal limiter diode spacing at 3 GHz.    182                                                                         |

| Table 6.2: Summary of 1dB compression power ratings at 1 GHz                                                                    |

| Table 6.3: Summary of 1dB compression power ratings at 2 GHz.    186                                                            |

| Table 6.4: Summary of 1dB compression power ratings at 3 GHz.    187                                                            |

| Table 6.5: 1dB compression power ratings at 1 GHz.    192                                                                       |

| Table 6.6: 1dB compression power ratings at 2 GHz.    192                                                                       |

| Table 6.7: 1dB compression power ratings at 3 GHz.    192                                                                       |

| Table 6.8: Summary of the performance comparison of the MMIC Limiters.       193                                                |

| Table 6.9: Stability factor, stability measure, noise figure and gain of the pHEMT, with and w | without |

|------------------------------------------------------------------------------------------------|---------|

| stabilising network at 10 GHz                                                                  | 198     |

| Table 6.10: Comparison of the matching network values of a low-noise amplifier with ideal,     | lossy   |

| and optimised passive components at 10 GHz                                                     | 204     |

| Table 6.11: Summary of the S-parameters and noise figure of the layout, schematic and measure  | sured   |

| results for the 10 GHz LNA.                                                                    | 208     |

| Table 6.12: Summary of the performance comparison of the MMIC LNAs                             | 209     |

#### Abstract

The expansion of the market for wireless communications and sensors has led to the recent increase in demand for highly integrated MMICs for millimetre-wave wireless applications. These applications require MMICs that offer low cost, high integration, high functionality and high performance as well as simpler, more rapid development. An effective way of meeting these requirements and realising highly integrated MMICs is by employing multilayer three-dimensional (3-D) MMIC technology. The research work described in this thesis presents the modelling and characterisation of newly developed passive components such as coplanar waveguides (CPWs), thin-film microstrips (TFMSs) and transition transmission line structures using 3-D multilayer technology. These structures have been developed with low losses in mind, along with variable characteristic impedances and miniaturised size. With the knowledge obtained from the design and optimisation of CPW and TFMS transmission lines, new and improved compact CPW-to-TFMS transitions have been successfully achieved. Accurate electromagnetic modelling was carried out using the 2.5-dimensional ADS Momentum simulator. Newly improved fabrication techniques were employed to produce reported compact microwave components and circuits, in order to lower cost and simplify the process. Compact MMIC components were fabricated using a seven-layer fabrication procedure on semi-insulating GaAs substrate where pseudomorphic high electron mobility transistors (pHEMTs) prefabricated by the manufacturer. High frequency on-wafer RF measurements were carried out using Agilent 8510 series vector network analysers (VNAs). In-depth analysis and comparisons between the simulated and measured results are provided. Analysis of active MMIC components was achieved by developing small-signal equivalent circuits of the GaAs pHEMTs, and knowledge extracted from this analysis was employed in the development of large signal models of the pHEMT devices. Furthermore, the design and characterisation of a few MMIC circuits, such as limiters and amplifiers, demonstrates the integration of multilayer CPW passive components with prefabricated pHEMTs. These components are compatible with RF systems-on-chip sub-systems providing low cost, low loss performance with their ease of fabrication.

#### Declaration

I declare that no portion of the work referred to in the thesis has been submitted in support of an application for another degree of this or any other university or other institute of learning.

## **Copyright Statement**

- The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made only in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trademarks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see <a href="http://www.campus.manchester.ac.uk/medialibrary/policies/intellectual-property.pdf">http://www.campus.manchester.ac.uk/medialibrary/policies/intellectual-property.pdf</a>), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see <a href="http://www.manchester.ac.uk/library/aboutus/regulations">http://www.manchester.ac.uk/library/aboutus/regulations</a>) and in The University's policy on presentation of Theses.

## Acknowledgements

First of all, I would like to thank God for the strength, courage and blessings throughout this whole journey.

My most sincere gratitude and deepest appreciation go to my supervisor Professor Ali. A. Rezazadeh for his continual advice and motivation for the entirety of this work. Without his mentorship and persistent help this research would not have been possible.

Next I would also like to extend my sincere thanks to Dr. Qing Sun, Dr. Graham Parkinson, Mr. Malachy Mcgowan, Mr. Keith Williams and Dr. Chris Duff for their expert advice on all experimental set-ups. I also wish to express my deep appreciation to some colleagues in our research group, Dr. Emerson Sinuligga, Dr. Mayahsa Ali, Mr. Yongjian Zhang, Ms. Norshakila Haris, Mr. Abdul Alim and Mr. Mohammed Aqeeli for their help and friendship given to me throughout this project.

I am also deeply grateful to my friends especially, Moses, Zarina, Simon, Rogers, Roger and Edward who offered me great guidance, encouragement and stuck with me throughout the length of my studies.

Finally, special thanks and immense gratitude goes to my family. Firstly I would like to thank my brother, Mathias and my sisters, Pauline, Paula, Pamela and Patricia for their encouragement and work behind the scenes. Then, I would like to extend my sincere gratitude to the Kalema family, Auntie Barbara, Uncle Fred, Fredrick, David and George, and Uncle Julius Kigonya for their warm hospitality during my stay overseas. Lastly my greatest appreciation goes to my parents, Mr. Paul Kyabaggu and Mrs. Margaret Kyabaggu for their never ending guidance, encouragement and all the financial sacrifices they made, to see to it that I reach to this stage of my education. For this, I dedicate this thesis to them together with the children and grandchildren of the late Jjaaja Yosefu Lugwana of Kanabulemu in Uganda.

#### **List of Publications**

- [1] P. B. K. Kyabaggu, A. A. Rezazadeh, "3D Multilayer Heterogeneously Integrated Systems-On-Chip," *EEE Postgraduate Poster Conference, The University of Manchester*, November 2010.

- [2] P. B. K. Kyabaggu, E. Sinulingga, M. M. Ali, Q. Sun and A. A. Rezazadeh, "Wideband 3D Coplanar Waveguide to Thin-Film Microstrip Transition in Multilayer Technology," *European Microwave Integrated Circuits Conference*, Manchester, October 2011, pp. 604-607.

- [3] E. P. Sinulingga, P. B. K. Kyabaggu and A. A. Rezazadeh, "Dispersion Characteristics and Loss Analysis of Low-Impedance 3D Interconnects for Compact MMIC," UK Semiconductor Conference, Sheffield, July 2011.

- [4] M. Mohammed-Ali, P. B. K. Kyabaggu, E. Sinulingga and A. A. Rezazadeh, "Nonlinearity Study of Double and Single Channel GaAs HEMTs," *European Microwave Integrated Circuits Conference*, 2011 IEEE 6<sup>th</sup>, Manchester, October 2011, pp. 362 – 365.

- [5] P. B. K. Kyabaggu, E. Sinulingga and A. A. Rezazadeh, "Design and Realisation of 3D Multilayer Components for Compact MMIC Applications," *EEE Postgraduate Poster Conference, The University of Manchester*, November 2012.

- [6] E. P. Sinulingga, P. B. K. Kyabaggu and A. A. Rezazadeh, "A Sub-THz Parameter Extraction of Low Loss 3D Compact Multilayer MMIC Coplanar Waveguides," UK Semiconductor Conference, Sheffield, July 2014.

- [7] M. A. Alim, A. A. Rezazadeh, M. M. Ali, E. P. Sinulingga, P. B. K. Kyabaggu, Y. Zhang and C. Gaquiere, "Thermal Characterisation of AlGaN/GaN HEMTs on Silicon Carbide Substrate for High Frequency Application," *Proceedings of European Microwave Week Conference*, Rome, October 2014, pp. 210-213.

- [8] Y. Zhang, A. A. Rezazadeh, H. A. Khan, E. P. Sinulingga, P. B. K. Kyabaggu and M. A. Alim, "Simulation and Analysis of InGaP/GaAs DHPTs using Eye Diagrams for Short Wavelength Optical Detection," *Proceedings of European Microwave Week Conference*, Rome, October 2014, pp. 524-527.

- [9] P. B. K. Kyabaggu, E. P. Sinulingga, N. Haris and A. A. Rezazadeh, "Design and Realisation of 3D Multilayer Components for Compact MMIC Applications," *The University of Manchester Postgraduate Summer Research Showcase*, June 2014.

- [11] P. B. K. Kyabaggu, N. Haris, A. A. Rezazadeh and E. P. Sinulingga, "Design and Realisation of a MMIC Power Limiter using 3D GaAs Multilayer CPW Technology," *European Microwave Week Conference*, Paris, September 2015– (accepted).

- [12] M. A. Alim, A. A. Rezazadeh, M. M. Ali, P. B. Kyabaggu, N. Haris and C. Gaquiere, "0.25 Î<sup>1</sup>/<sub>4</sub>m AlGaN/GaN HEMT Nonlinearity Modelling and Characterization Over a WideTemperature Range," *European Microwave Week Conference*, Paris, September 2015– (accepted).

- [13] M. A. Alim, A. A. Rezazadeh, M. M. Ali, P. B. Kyabaggu, N. Haris and C. Gaquiere, "Nonlinearity Measurement and Analysis of 0.25 Î<sup>1</sup>/4m GaN HEMT Over Frequency and Temperature Using Two-Tone Intermodulation Distortion," *European Microwave Week Conference*, Paris, September 2015– (accepted).

- [14] N. Haris, P. B. Kyabaggu, M. A. Alim and A. A. Rezazadeh, and, "Device Considerations and Characterisation of Double-Channel GaAs pHEMT Schottky Diodes for Limiter Applications," *European Microwave Week Conference*, Paris, September 2015– (accepted).

- [15] P. B. K. Kyabaggu, N. Haris, A. A. Rezazadeh and E. P. Sinulingga, "Design and Realisation of Compact MMIC Limiters using 3D Multilayer Technology," to be submitted for journal publication.

## Chapter 1 Introduction

In the Monolithic Microwave Integrated Circuit (MMIC), the monolithic describes the fundamental nature of MMICs, namely that they are fabricated on one single piece of semiconductor, while 'microwave' refers to an electromagnetic wave with a free-space wavelength and a frequency ranging from 300 MHz up to 300 GHz. Finally, 'integrated circuit' refers to the act of integration between the passive and active components and with interconnects fabricated on the same semiconductor substrate. The expansion of the market for wireless communications and sensors has led to the recent interest in highly integrated MMICs for millimetre-wave wireless applications. These applications require MMICs that are low cost, high integration levels and high performance, as well as simpler, more rapid development [1]. An effective way of meeting these requirements and producing highly integrated MMICs is by employing three-dimensional (3-D) MMIC technology [1]. A key part of this 3-D MMIC technology is the thin-film microstrip (TFMS) transmission line, which is formed on a 3-D structure – as shown in Figure 1. The TFMS line offers a narrow line width and spacing because of its thin substrate, with thicknesses ranging from 1 to 20 μm. A 3-D structure offers several other benefits, including compactness and the isolation of passive components from substrate properties using the ground plane.

In addition, recently there has been an increasing demand in the field of microwave integrated-circuit technologies to lower the dissipation loss of transmission lines, in order to improve noise output and efficiency performance of circuits such as low-noise and power amplifiers [2]. Low-loss transmission lines are also desirable when creating low-loss passive components such as filters, baluns, transitions and couplers. In a CPW design, via holes are not necessary and fragile semiconductors do not need to be excessively thin. In addition, individual component sizes are unlimited [2]; these factors can greatly reduce processing costs. For applications such as reduced-size couplers and non-linear transmission lines, it is desirable to use high impedance transmission lines. On the other hand, ultra-low transmission lines are required in matching networks where low impedance devices, such as power field-effect transistors (FETs) or photodiodes, are used. The range of maximum impedance is limited by the practical size of the slot and the width of the centre line, while a practical low limit is imposed by fabricating the very narrow slot, and high losses result from current crowding on the edges [2].

One problem associated with the CPW is that the ground must be on either side of the signal lines, which increases the complexity of the circuit designs. A potential solution to this problem is to utilise a multilayer technique in which several metal layers are sandwiched by insulators. This technique gives microwave engineers flexibility in designing multilayer structures with improved circuit performance [2].

Increasing demand for high-density and high-functionality microwave and millimetre-wave circuits has led to innovative circuit architectures such as three-dimensional (3D) multilayer MMICs. The major advantage of the multilayer techniques is not only that one can design miniature microstrip lines, but they also allow for employing other 3D passive components [3]–[10]. However, these complex architectures require interconnect transitions with low insertion and return losses, in order to yield low-loss, compact multilayer MMIC circuits.

Various types of transitions have already been developed and reported, including transitions by electrical contact [4] and those that use electromagnetic coupling [5]. Electrical contact transitions usually call for via holes, bonding wires or abrupt steps in the conductor [6], and they are compact in size and have a relatively wide bandwidth despite involving some degree of mechanical complexity [6]-[8]. Electromagnetic coupling transitions, on the other hand, require no via holes or wire bonds, though most of them suffer from narrow bandwidth and are larger in size. Several reports [3]–[5], [9]–[12] have discussed transitions based on electromagnetic coupling, which occurs in the overlap region between the coplanar waveguide (CPW) and the microstrip (MS). However, existing published transitions have poor robustness due to their simple structures and the lack of availability of multilayer technology for flexible compact designs. In addition, to the best of our knowledge, there is no information available on thin film microstrips (TFMSs) in the construction of transitions. This work discusses and provides for the first time full analyses of transitions operating at high frequencies between CPWs and thin film microstrips, by using multilayer technology. Most characterisations of MMIC interconnects reported so far have been carried out using analytical approaches such as quasi-static analysis [13], developed further by Bedair et al. [14]. However the accuracy of these analytical techniques is limited at higher frequencies (above 40GHz) due to some higher order modes occurring in the CPW transmission lines. Since wideband CPW transition structures in this work are designed and modelled up to a frequency of 50 GHz, quasi-static approximation is not suitable to be applied as a primary modelling technique. Eisenstadt et al. [15] reported another characterisation technique based on S-parameters for the non-multilayer structure. Since this technique enables wideband characterisation, regardless of how the modes occur in the structure, we have therefore chosen this method as the main modelling tool in our work.

The major advantage of multilayer techniques is that with either a conventional or a multilevel technique, one can not only design miniature microstrip lines, but can also employ 3D passive components [16]. At millimetre frequencies, CPWs provide many solutions to the design of low-loss, uniplanar, low-cost and compact integrated circuits. However, many applications, such as on-wafer measurements of microstrip circuits or vertically integrated circuits, require the flexibility to use a combination of planar technologies. Consequently, this leads to the development of transition structures such as CPW to thin-film microstrip transition.

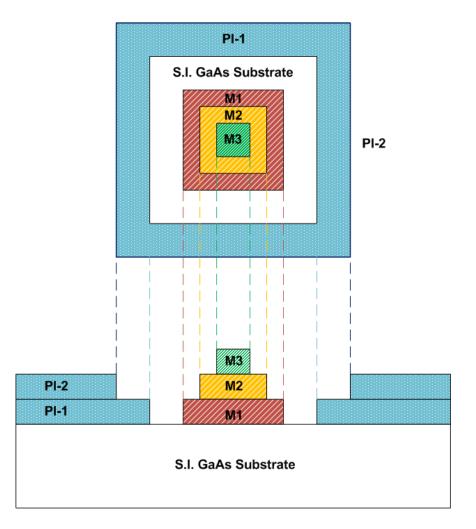

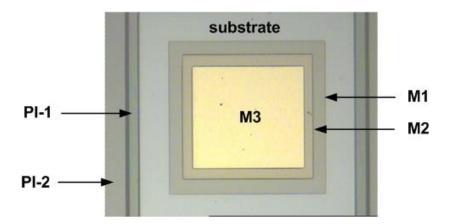

In this work, the design and characterisation of compact multilayer CPW components and circuits fabricated on semi-insulating GaAs substrates has been carried out successfully. Three-dimensional MMICs are realised on a semi-insulating GaAs substrate by stacking two dielectric layers separated by three metal conductor layers. A number of passive components, such as thin film resistors, inductors, capacitors and CPW-to-TFMS transitions, were designed and realised. Furthermore, active circuit components such as pHEMT diodes, limiters and LNAs were realised at the University of Manchester with prefabricated pHEMT devices from Filtronic on a S.I. GaAs substrate. An improved 7-layer multilayer fabrication procedure is also demonstrated in this work.

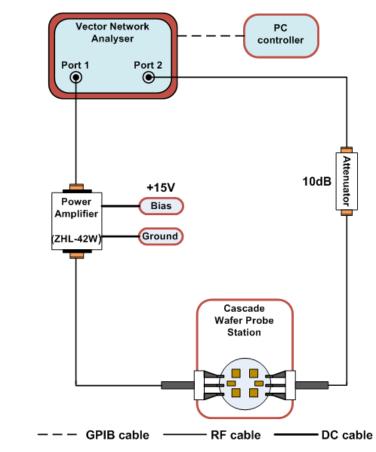

In order to analyse and predict the properties of these multilayer active and passive CPW components and circuits, electromagnetic simulations were carried out using a 2.5-dimensional ADS Momentum simulator as well as Agilent IC-CAP. RF on-wafer measurements were performed using the Cascade wafer probe station and HP8510 Vector Network Analyser (VNA) aligned with the LRRM calibration technique. Good agreements between the measured and simulated results are reported from the comparative analyses performed in this work.

This research presents design guidelines for the development of compact, wideband multilayer coplanar waveguide to thin-film microstrip transitions, which does not require any via holes between the CPW ground strips and the TFMS backside ground plane. Two transition designs are studied: a design with a footprint on the CPW end (design A) and a design without a footprint (design B) [17]. The work presented in this thesis shows the

performance of a compact transition design using multilayer technology, along with their design characteristics and optimisations. The results provide RF engineers a better understanding of the electromagnetic behaviour of the transition and hence reduce the design time required to develop broadband transitions.

The integration between passive components with commercially available active components such as pHEMTs is also demonstrated in this work. This shows the advantage of using 3D multilayer CPW technology in regards to making circuits compact and reducing overall fabrication costs. Circuit compactness in this work is demonstrated in the spiral limiters and a 10 GHz low-noise amplifier. Therefore, the knowledge acquired from the design and characterisation of multifunctional passive and active multilayer CPW components and circuits in this research work can be adopted by RF circuit designers for various compact MMIC applications.

#### 1.1 Key aims and objectives of this research

The aims of this research is to design and produce an array of multifunctional passive and active CPW components and circuits that can be employed for compact MMIC applications. To achieve compactness while maintaining better performance at a wide band, 3D multilayer technology is employed.

The main objectives of this research include:

- Analysing published theoretical and experimental literature on the transmission line theorem, in order to establish a solid foundation for the modelling of 3D MMICs.

- Developing novel simulation techniques to improve the accuracy of the results obtained and comparing these results with data already published, thus demonstrating the merits of 3D multilayer MMICs;

- Improving multilayer fabrication techniques for creating multilayer passive and active circuits.

- Analysing and establishing optimisation techniques for multilayer components and exploiting available flexibility in multilayer technology in producing low-loss performance chips at low cost, reduced sizes and which are easy to fabricate.

- Attaining in-depth knowledge on different loss parameters involved in multilayer CPW components, such as transitions. Identifying solutions to minimise these losses and optimising their performance to make them suitable for RF applications.

- Carrying out parameter extractions to develop both small- and large-signal GaAs pHEMTs models to facilitate the integration of passive and active components. Hence, this helps yield compact circuits such as limiters and amplifiers.

### 1.2 Key Research Contributions

The key research contributions of this work that highlight the mentioned objectives in subchapter 1.1 are summarised as:

- The development of an improved step by step guide for multilayer fabrication of MMICs.

- Design guidelines for a noval CPW-to-TFMS transition have been developed based on 3D multilayer technology and employs electromagnetic coupling.

- New Schottky diodes using pHEMT configurations have been designed and fabricated.

- New MMIC power limiters using pHEMT diodes have been designed and fabricated.

- A low noise amplifier is used to demonstrate the integration between active devices with passive components using 3D multilayer technology. Hence this leads to the reduction of the overall chip size.

#### 1.3 Thesis overview

Chapter 1

This chapter gives a general overview of the key research contributions along with the realised aims and objectives.

Chapter 2

Any research work being undertaken requires a strong foundation or background in-depth study. This chapter provides background reviews on MMIC technology and also discusses its applications. A background study of different types of transmission lines, including CPW-to-TFMS transition, is undertaken. An insight into unipolar and bipolar transistors is also given as well as HEMT transistors, in particular for the pHEMT transistor. An indepth review of the microwave diodes and limiter circuits is also presented herein.

#### Chapter 3 and Chapter 4

Experimental techniques and methodologies, which include electromagnetic simulator momentum in ADS and the detailed fabrication procedure involved in 3D multilayer passive and active components, are presented in Chapter 3. Calculation methodologies for parameter extraction using the S-parameters are also detailed in this chapter, and different types of on-wafer calibration techniques are presented. Any fabrication problems encountered, and their solutions, are discussed along with the fabrication calibration results in chapter 4.

#### Chapter 5 and Chapter 6

Multilayer transmission lines, such as CPW and thin-film microstrips (TFMSs), are designed and modelled in chapter 5, and their design parameters are used later to design CPW-to-TFMS transitions. This chapter also discusses why different parameters were chosen for the transition transmission line design. CPW, TFMS and transition regions are analysed and discussed in relation to why a tapered design was used for the transition and why a footprint on the CPW region was considered a good design aspect. Improved compact and low-loss transitions are also provided. Chapter 5 further includes fabricated GaAs pHEMTs characterised over fixed bias points and frequencies. The small-signal analysis of these GaAs pHEMTs, and their integration with MMIC passive components to form integrated circuits such as a low noise amplifier and microwave limiters, are discussed in chapter 6. Comparisons of the measured results with the small-signal and large-signal TOM3 models are also presented in chapter 6.

#### Chapter 7

This chapter details the key objectives achieved in this work, and then it identifies and discusses some aspects of future work for compact MMIC applications.

## **Chapter 2** Literature Review

### 2.1 MMIC TECHNOLOGY