## THE UNIVERSITY OF MANCHESTER

## **Dynamic Program Analysis and Optimization under DynamoRIO**

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF MASTER OF PHILOSOPHY (MPHIL) IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

Author: Naweiluo ZHOU Supervisors: Prof. John GURD Prof. Alasdair RAWSTHORNE

School of Computer Science 2014

# Contents

| A | bstrac                   | et                                        | 10 |  |

|---|--------------------------|-------------------------------------------|----|--|

| D | Declaration<br>Copyright |                                           |    |  |

| C |                          |                                           |    |  |

| A | Acknowledgements         |                                           |    |  |

| G | Glossary                 |                                           |    |  |

| 1 | 1 Introduction           |                                           |    |  |

|   | 1.1                      | Contribution                              | 24 |  |

|   | 1.2                      | Thesis Structure                          | 25 |  |

| 2 | Background               |                                           |    |  |

|   | 2.1                      | Introduction                              | 27 |  |

|   | 2.2                      | Terminology                               | 28 |  |

|   | 2.3                      | Profiling Techniques                      | 28 |  |

|   | 2.4                      | Data Flow and Control Flow Analysis       |    |  |

|   | 2.5                      | Optimization Techniques                   | 31 |  |

|   |                          | 2.5.1 Introduction                        | 31 |  |

|   |                          | 2.5.2 Software Prediction                 | 31 |  |

|   |                          | 2.5.3 Optimization Algorithms in Software | 32 |  |

|   |                          | 2.5.4 Hardware Prediction                 | 34 |  |

|   |                          | 2.5.5 Code Reuse in Hardware              | 35 |  |

|   | 2.6                      | Static Optimizers                         | 36 |  |

|   |                          | 2.6.1 Introduction                        | 36 |  |

|   |                          | 2.6.2 MAO                                 | 37 |  |

|   |                          | 2.6.3 Superoptimizer                      | 38 |  |

#### CONTENTS

|   |     | 2.6.4                                          | Peephole Optimizer                                 | 39 |  |  |

|---|-----|------------------------------------------------|----------------------------------------------------|----|--|--|

|   |     | 2.6.5                                          | Summary                                            | 40 |  |  |

|   | 2.7 | Dynan                                          | nic Optimizer                                      | 41 |  |  |

|   |     | 2.7.1                                          | Introduction                                       | 41 |  |  |

|   |     | 2.7.2                                          | Dynamo                                             | 43 |  |  |

|   |     | 2.7.3                                          | DynamoRIO                                          | 44 |  |  |

|   |     | 2.7.4                                          | Mojo                                               | 48 |  |  |

|   |     | 2.7.5                                          | Wiggins/Redstone                                   | 49 |  |  |

|   |     | 2.7.6                                          | Java Virtual Machine and JIT compiler              | 49 |  |  |

|   |     | 2.7.7                                          | Pin and its JIT compiler                           | 51 |  |  |

|   |     | 2.7.8                                          | HDTrans                                            | 52 |  |  |

|   |     | 2.7.9                                          | Summary                                            | 55 |  |  |

|   | 2.8 | Chapte                                         | er Summary                                         | 56 |  |  |

| 3 | Dyn | amic C                                         | ode Analysis and Optimization                      | 59 |  |  |

|   | 3.1 | Introd                                         | uction                                             | 59 |  |  |

|   | 3.2 |                                                | dology                                             | 59 |  |  |

|   |     | 3.2.1                                          | Evaluation Test Case: SPEC CPU2006                 | 60 |  |  |

|   |     | 3.2.2                                          | Configuration                                      | 62 |  |  |

|   | 3.3 | Base F                                         | Performance of DynamoRIO                           | 62 |  |  |

|   | 3.4 | Experiment 1—Removal of Redundant Instructions |                                                    |    |  |  |

|   |     |                                                | iment 2—Strength Reduction                         | 70 |  |  |

|   |     |                                                | iment 3—Instruction Alignment                      | 72 |  |  |

|   |     | 3.6.1                                          | Analysis of Rationales for <i>nop</i> Optimization | 77 |  |  |

|   |     | 3.6.2                                          | Memory References Simulator                        | 78 |  |  |

|   |     | 3.6.3                                          | Branch Target Prediction Simulator                 | 79 |  |  |

|   |     | 3.6.4                                          | Cache Simulator                                    | 81 |  |  |

|   | 3.7 | Experi                                         | iment 4—Persistent Code                            | 83 |  |  |

|   | 3.8 | Experi                                         | iment 5—Glacial Address Propagation                | 84 |  |  |

|   |     | 3.8.1                                          | Constant Addresses Analysis                        | 85 |  |  |

|   |     | 3.8.2                                          | Instrumentation Optimization                       | 90 |  |  |

|   | 3.9 | Chapte                                         | er Summary                                         | 92 |  |  |

| 4 | Con | clusion                                        | and Discussion                                     | 95 |  |  |

|   | 4.1 | Introd                                         | uction                                             | 95 |  |  |

|   | 4.2 | Conclu                                         | usion and Discussion                               | 95 |  |  |

| Bibliogr | _      |                                                       |    |

|----------|--------|-------------------------------------------------------|----|

|          | 4.3.5  | Energy Consumption Management                         | 99 |

|          | 4.3.4  | Possible Application Analysis                         | 99 |

|          | 4.3.3  | Memory Management                                     | 98 |

|          | 4.3.2  | Glacial Addresses Optimization and Multiple Threading | 97 |

|          | 4.3.1  | Integration of Static and Dynamic Optimization        | 97 |

| 4.3      | Future | Work                                                  | 97 |

# **List of Figures**

| 1.1  | The working layer of virtual systems                             | 23 |

|------|------------------------------------------------------------------|----|

| 2.1  | Value prediction                                                 | 34 |

| 2.2  | Instruction reuse in a typical processor                         | 35 |

| 2.3  | Structure of the peephole optimizer                              | 40 |

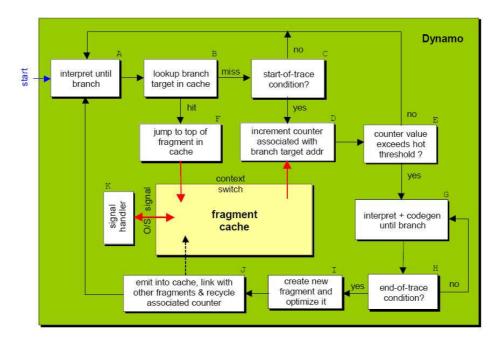

| 2.4  | How Dynamo works                                                 | 44 |

| 2.5  | Basic infrastructure of DynamoRIO                                | 46 |

| 2.6  | The deployment of DynamoRIO and its client                       | 47 |

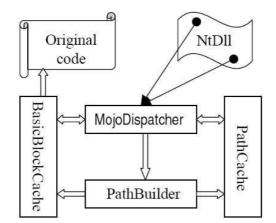

| 2.7  | Basic structure of Mojo                                          | 48 |

| 2.8  | How JVM works                                                    | 50 |

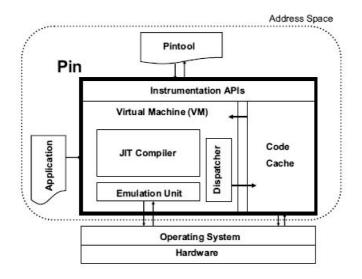

| 2.9  | The basic architecture of Pin                                    | 52 |

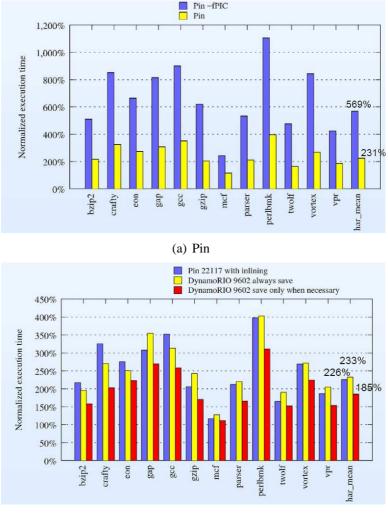

| 2.10 | Benchmarks performance of Pin and DynamoRIO                      | 53 |

| 2.11 | An example of source instructions                                | 54 |

| 2.12 | An example of translated instructions                            | 54 |

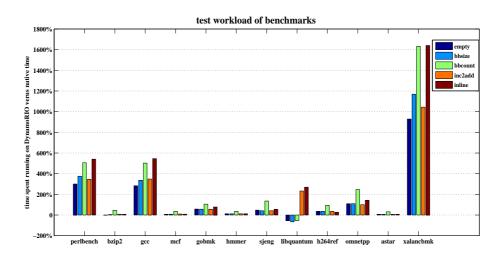

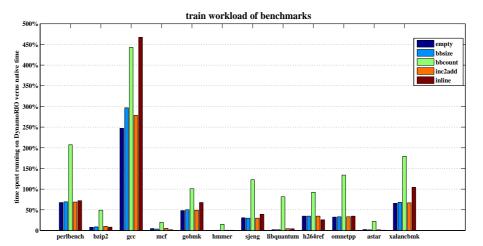

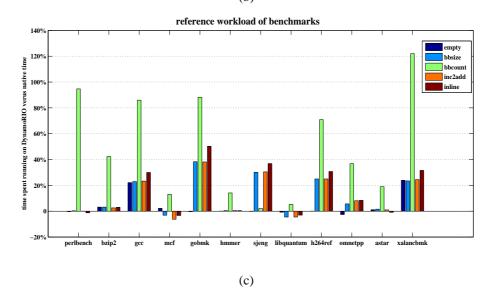

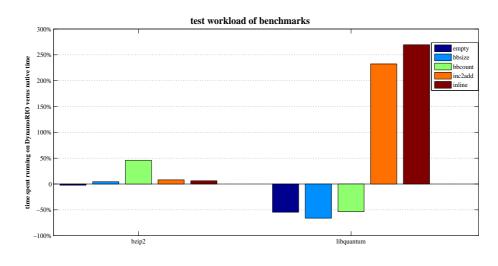

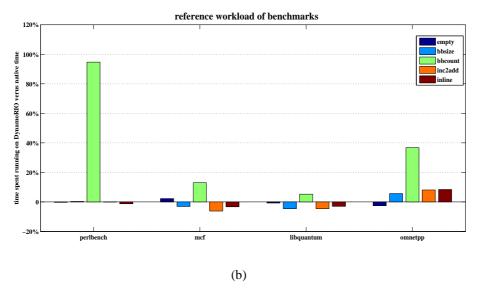

| 3.1  | Simple benchmark performance for all workloads                   | 65 |

| 3.2  | Simple benchmark performance of test and reference workload      | 66 |

| 3.3  | Redundant <i>test</i> instruction                                | 67 |

| 3.4  | DynamoRIO routine for instrumenting in a trace                   | 69 |

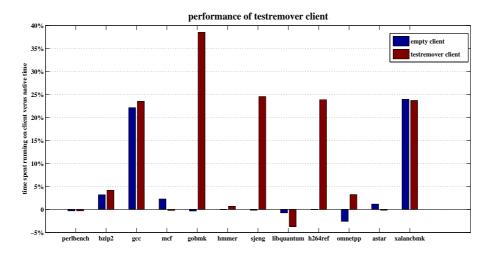

| 3.5  | Benchmark performance on the <b>testremover</b> and <b>empty</b> | 70 |

| 3.6  | Equivalent instructions                                          | 71 |

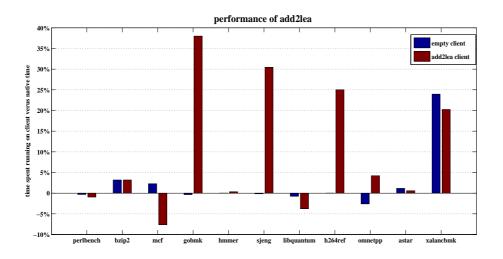

| 3.7  | Benchmark performance for add2lea client and empty client        | 72 |

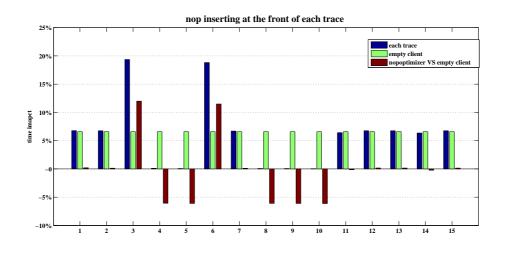

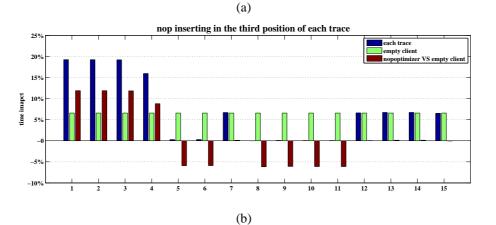

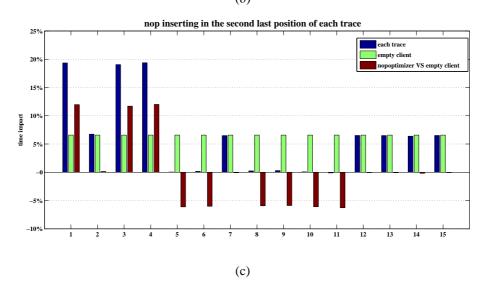

| 3.8  | Benchmark performance fluctuation when removing <i>nop</i>       | 74 |

| 3.9  | A trace example                                                  | 75 |

| 3.10 | Performance fluctuation of each trace                            | 76 |

| 3.11 | A DynamoRIO function call for inserting <i>nop</i>               | 77 |

| 3.12 | The DynamoRIO calls to determine memory references               | 79 |

| 3.13 | The DynamoRIO branch instrumentation function calls              | 80 |

| 3.14 | Thread initialisation and termination routines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.15 | DynamoRIO calls to enable data to be saved in persistent cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83 |

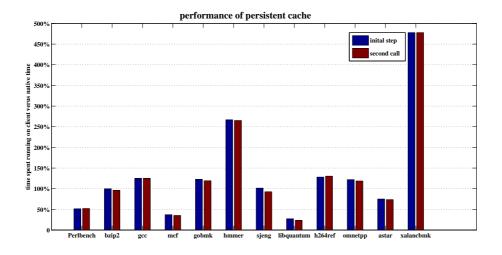

| 3.16 | Persistent code performance comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 84 |

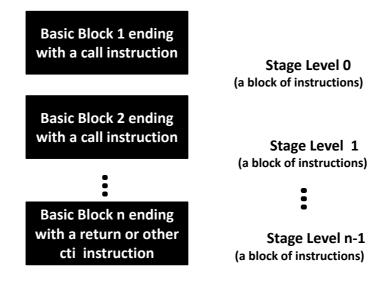

| 3.17 | The way for labelling stage levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 87 |

| 3.18 | Codes to obtain the register value under DynamoRIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 88 |

| 3.19 | Codes to obtain the execution frequency of each block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 88 |

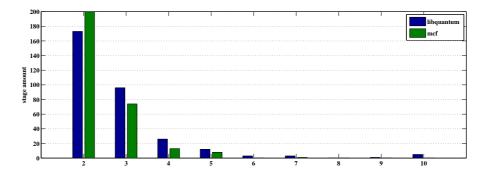

| 3.20 | Stage information of <b>libquantum</b> and <b>mcf</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89 |

| 3.21 | The DynamoRIO function to generate a client thread                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 91 |

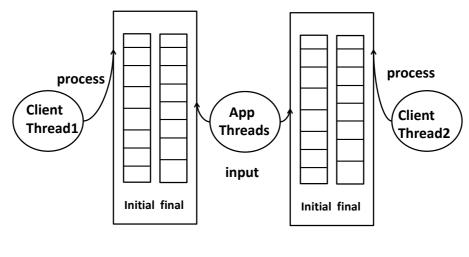

| 3.22 | Multi-threading procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 92 |

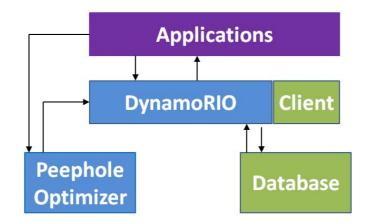

| 4.1  | The infrastructure of the optimization system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 98 |

|      | i jan in the second sec | -  |

# **List of Tables**

| 3.1  | SPEC CPU2006 packages                                         | 62 |

|------|---------------------------------------------------------------|----|

| 3.2  | Default DynamoRIO client details                              | 63 |

| 3.3a | Time spent on each test workload benchmark                    | 67 |

| 3.3b | Time spent on each train workload benchmark                   | 68 |

| 3.3c | Time spent on each reference workload benchmark               | 69 |

| 3.4  | Total number of <i>test</i> instructions detected and deleted | 70 |

| 3.5  | Total number of <i>add</i> in the traces of benchmarks        | 72 |

| 3.6  | Equivalent to <i>nop</i> instructions in DynamoRIO            | 73 |

| 3.7  | An example of indirect address candidates                     | 85 |

| 3.8  | An example of substitution instructions                       | 86 |

| 3.9  | Stage information of <b>libquantum</b> and <b>mcf</b>         | 89 |

| 3.10 | Average glacial address number in each stage level            | 89 |

| 3.11 | Sum of glacial addresses in each stage level of the program   | 90 |

| 3.12 | A list of all the implemented clients                         | 93 |

## Abstract

A thesis submitted for the degree of Master of Philosophy Title: Dynamic Program Analysis and Optimization under DynamoRIO By Naweiluo Zhou, The University of Manchester, 5th February 2014

The thesis presents five experiments using DynamoRIO to analyse and optimize machine codes at runtime in various ways and observe the effect of each optimisation using the SPEC CPU2006 benchmarks as test case codes.

Software often stays unchanged for periods measured in years, while new CPU chips are introduced every 18 months or so. In addition, it is often not realized how modern CPU chips adjust their behaviour, and their performance, in response to dynamic conditions arising in the software that is running. Dynamic optimization is carried out while a program runs. It calls on the knowledge of runtime behaviour of the program, which causes high runtime overhead.

Programs can show performance gain by applying removal of redundant instructions, strength reduction, instruction alignment and persistent code. Strength reduction replaces expensive instructions with cheap counterparts. The code layout in the memory could affect the cache miss rate and the branch mis-prediction rate of the processor, which affect program performance. An optimized program could be recorded as persistent cache, then loaded directly in the subsequent calls. One dynamic program analysis method, glacial address propagation, is also presented. The values of glacial indirect addresses change slowly, making each value act as a constant address for a period, thus enabling a cascade of optimizations. To accelerate information processing, profile information is processed by multiple threads in parallel.

Therefore, programs can be made to run more quickly using a variety of optimization carried out at runtime, aided by observation of control flow, data flow, and memory access patterns of programs. Future work could perform static optimization before dynamic optimization. The hardware power consumption will be taken into account.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

# Copyright

- i The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and she has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner of the relevant Intellectual Property and/or Reproductions.

- iv Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx?DocID=487), in any relevant Thesis restriction declarations deposited in the University Library, Them University Library's regulations<sup>1</sup> and in The University's policy on Presentation of Theses.

<sup>&</sup>lt;sup>1</sup> See http://www.manchester.ac.uk/library/aboutus/regulations

## Acknowledgements

The two years spent in Manchester is one of my most joyful, peaceful periods in life. I must express my appreciation to all the people who have helped me. I shall and will remember all the kindness.

I would like to take this chance to especially thank my supervisor Prof. John Gurd. He advised me on the experiments and support me to fix and complete the thesis. He also offers great help on my future career.

I also would like to express my gratitude to my supervisor Prof. Alasdair Rawsthorne who leaded me to the research area in program analysis and optimization.

I have to express my gratitude to Dr. Barry Cheetham who has helped me for the last two years. I would like to thank him for his constructive advice on my research as well as my future career.

## Glossary

#### Symbols | L

#### **Symbols**

#### **Boolean Test**

test if two instructions' minterms of the Boolean arguments match. 38

#### Constant propagation

analyse a variable whose value is a constant. 30

#### DynamoRIO basic block

a sequence of instructions ending with a control transfer instruction. 45

#### DynamoRIO trace

a piece of hot code constructed by modified NET algorithm. 32, 45

#### **DynamoRIO**

a runtime code manipulation system. 44

#### Mojo fragment

a piece of code with additional control transfer instructions in Mojo. 48

#### Mojo path

consists of multiple basic blocks. 48

#### **Probabilistic Test**

test if the output results match the original program. 38

#### SPEC CPU2006

a benchmark suite. 60

#### address profile

memory addresses references. 29

#### application thread

works in DynamoRIO's code cache. 90

#### basic block cache

DynamoRIO's code cache. 45

#### benchmark

a computer program that performs set operations. 61

#### binary translation

translate one type of executable to another. 41

#### client thread

run natively. 90

#### client

perform runtime code manipulation. 46

#### code cache

a part of memory space allocated by an optimizer. 28

#### context switch

DynamoRIO saves and restores the general-purpose registers, the condition codes (eflags register) and any operating system dependent state. 45

#### context

information of integer registers, flag registers, instruction pointers and the program stacks. 36

#### control flow profile

information of program execution path. 29

#### dynamic optimization

performs optimization during program execution. 27

#### equivalence tests

test if two instructions perform the same function. 38

#### fragment

another expression of trace. 28

#### Glossary

#### glacial address propagation

label the indirect addresses with useful properties. 85

#### glacial variables

slowly change variables. 30

#### hot

the word hot in this thesis means frequently-executed. 23

#### instrumentation

a technology for inserting extra codes into a program. 51

#### just-in-time compilation

compile a machine-independent program for a processor. 41

#### offline profiling

performed before the program executes. 29

#### online profiling

records the information during program execution. 29

#### path

another expression of trace. 28

#### profile

information of the distribution of call sites, parameter values, the execution times of each basic block of the program, *etc.* 29

#### reference workload

simulate the function of the real application. 61

#### stage level

a stage level is a basic block labelled with useful properties. 86

#### stage

a set of basic blocks, a stage ends with a special control transfer instruction. 86

#### static optimization

optimizes the program during compile time. 27

#### test workload

a simple version of reference workload. 61

#### trace cache

DynamoRIO's code cache. 45

#### trace

a trace in a dynamic optimizer is a piece of code which is frequently executed. 28

#### traditional basic block

a sequence of instructions with a single entry and single exit. 36

#### traditional trace

a large sequence of instructions. 36

#### train workload

takes more time to finish than the test workload. 61

#### transparent optimization

take binary executable and re-optimize it. 41

#### value profile

information of the specific values. 29

#### L

#### LSD

Loop Stream Detector. 38

# Chapter 1

# Introduction

## Chapter 1

## Introduction

Program optimization is ubiquitous, as it improves program performance though either reducing the program size or accelerating program execution. Programs run faster on newer generation CPU silicon. Production software, though, often stays unchanged for periods measured in years, while new CPU chips are introduced every 18 months or so. In addition, it is often not realized how modern CPU chips adjust their behaviour, and their performance, in response to dynamic conditions arising in the program that is running. For example, a modern CPU chip will adjust the order of instructions issued, the memory references it carries out, and the order in which it fetches instructions depending on the exact pattern of execution in recent history, since it uses its own observation of that history to attempt to run future instructions more speedily.

A compiler takes the high-level input source program and outputs the equivalent but low-level sequences of instructions which are usually machine codes. Compilation mainly includes five phases [3]: lexical analysis, syntax analysis, intermediate code generation, code optimization and code generation. Code optimization carried out during compile time is called static optimization (details are given in Section 2.6) and no online information is available. In contrast, Dynamic optimization (details are given in Section 2.7) is performed as the program runs, enabling it to call on knowledge about the runtime behaviour of the program.

Modern software applications heavily make use of shared libraries, dynamic class loading, virtual functions, plugins, dynamically-generated code, and other dynamic mechanisms. Optimization decisions really need to be deferred until all the relevant information is available. Dynamic code optimization shows its advantage over static optimization in four respects (the detail will be covered in Chapter 2). First and foremost, it makes the program work more efficiently compared with static optimization. Secondly, dynamic optimization makes use of prediction of runtime program behaviour, as runtime profile information is available. Thirdly, modern software [7] is being shipped as a collection of DLLs (Dynamically Linked Libraries), making it difficult for a static compiler to analyse the whole program [11]. Finally, dynamic code manipulation systems can solve hardware compatibility problems for cross-platform application-level virtualization (*e.g.* Apple Rosetta<sup>1</sup>).

However, dynamic optimization suffers from its own problems. The most significant disadvantage is that it slows down program execution due to collection of the runtime information (*e.g. hot*  $^2$  region analysis, memory usage analysis). A number of runtime systems, such as Dynamo [15], DynamoRIO [13] and Wiggins/Redstone [18], have been developed in order to perform runtime code optimization and also confine overhead to a low level.

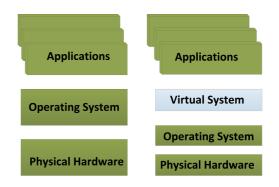

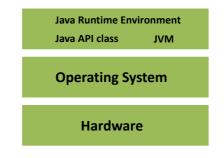

The most well-known and widely-used code manipulation system is the Java Virtual Machine.<sup>3</sup> Figure 1.1 gives a view of where these runtime code manipulation systems (known as virtual systems) reside in a compilation and execution procedure. The left of the figure shows the system without the virtual system. The right of the figure shows the system with the virtual system. The details of all these systems are presented in Chapter 2.

Figure 1.1: The working layer of virtual systems. The left side is the traditional view; the right side is the virtual system view

The thesis focuses on dynamic program analysis and optimization, as dynamic optimization is able to adapt its optimization approaches to match the runtime behaviour

<sup>&</sup>lt;sup>1</sup> Apple Rosetta, http://www.apple.com/asia/rosetta/, accessed on 30/05/2012.

<sup>&</sup>lt;sup>2</sup> The word *hot* in this thesis means frequently-executed.

<sup>&</sup>lt;sup>3</sup> JVM, available from http://docs.oracle.com/javase/specs/jvms/se7/html/jvms-1.html, accessed on 17/04/2012.

of the program. DynamoRIO, an open-source software, is the runtime code manipulation system employed in this thesis to perform program analysis and optimization. Firstly, its input is the binary stream, making the platform language-independent. Plus in some cases, source codes of the program are not available, hence code optimization cannot rely on the compiler. Secondly, DyanmoRIO is flexible, as it is able to perform optimizations which tailor the program to the actual processor it is running on. In other words, DynamoRIO can efficiently make use of underlying hardware mechanisms. Thirdly, DynamoRIO provides a good user interface for manipulating the runtime program. Additionally, DynamoRIO can tackle the machine code directly, such as branch inlining and instruction replacement, *etc*. The compiler usually performs optimization on intermediate representation codes which is generally considered to be easier than optimization on machine code. However, it is an open question whether recompilation in order to perform the optimization is more time-consuming or performing the optimization on the machine code directly causes more overhead.

## 1.1 Contribution

This thesis investigates runtime code analysis and optimization methodologies. Strength reduction (Section 3.5) has been applied in DynamoRIO in a previous publication [44], but this thesis expands and presents the method in detail. Three methods in this thesis are modifications of existing work. This includes redundant instruction detection (Section 3.4), instruction alignment optimization (Section 3.6) and glacial address propagation (Section 3.8). There are some publications that show similar research on redundant instruction detection as well as instruction alignment, but none of them apply the above schemes in the runtime environment under DynamoRIO as in this thesis. Glacial address propagation is a modification of glacial variable analysis [4]. This algorithm aims to discover the potential slowly changing addresses during program execution. As glacial indirect addresses are changed slowly and could be considered to be a constant address for a period, these indirect addresses are candidates for code replacement aiming for code optimization.

The experimental results in the thesis demonstrate that some benchmarks gain performance at a single digit percentage level through dynamic program optimization. A dynamic program analysis method, glacial address propagation, shows the potential candidates in a program which may enable a cascade of code optimization.

### **1.2 Thesis Structure**

The thesis investigates and explores runtime program analysis and optimization methodologies. The runtime code manipulation system, DynamoRIO, which supports code transformation on any part of programs, is exploited as a development tool to investigate the design space for optimizers between the current state of the art in static and dynamic languages. DynamoRIO provides interfaces (details are given in Section 2.7.3) which enable development of program analysers to observe and potentially manipulate every single instruction prior to its execution. Although there is runtime profile overhead, the overall execution time of the application can be decreased in certain cases.

This thesis first describes background techniques and technologies in Chapter 2. Then it presents the five experiments on program analysis and optimization in Chapter 3. The experiments incorporate redundant instruction detection and removing (Section 3.4), strength reduction optimization (Section 3.5), instruction alignment (Section 3.6), persistent cache (Section 3.7) and glacial address propagation (Section 3.8). Discussion of the experimental results and potential future work are presented in Chapter 4.

# Chapter 2

# Background

## **Chapter 2**

## Background

### 2.1 Introduction

The performance of a program is essentially determined by its size and running time. Program optimization is ubiquitous, as it improves program performance though either reducing the program size or accelerating program execution. *Static optimization*, which is employed in almost all compilers, optimizes the program during compile time to produce better performance of codes. *Dynamic optimization*, which is found for example in a Java Just-In-Time compiler, performs optimization during program execution, enabling the discovery of runtime information which is not available at compile time. Feeding back such information could enable the compiler to make better decisions in its optimization algorithms, but an alternative way of searching for code optimization is from dynamic optimizers. Such an optimizer does not perform complex lexical analysis and syntax analysis, as the compiler does [3], rather it performs optimization on the machine code (*e.g.* assembly level or binary level).

This chapter briefly reviews the background techniques and technologies for code analysis and optimization to help better understand Chapter 3. The chapter is organised as follows. It first reviews program analysis methods, as program analysis provides necessary information for the choice of program optimizations. Profiling techniques (Section 2.3) and data flow/control flow analysis (Section 2.4) are two program analysis techniques. Section 2.5 gives optimization techniques. These are the algorithms contributing to an optimizer, a compiler's basic working procedure or the basic code optimization algorithms guiding complex algorithm design. The two next sections (Section 2.6 and Section 2.7) review optimization technologies in the working procedure of some optimizers. Section 2.6 reviews three static optimizers. In Section 2.7

seven well-known dynamic optimizers are reviewed to help gain a better understanding of how a runtime system works on code optimization.

### 2.2 Terminology

This section explains some critical terminology used in this chapter and the rest of the thesis.

Dynamic optimizers share a common and important characteristic, that is building traces. A *trace* is a piece of code which is frequently executed. This piece of code may contain some repeated codes (due to code inlining) occupying a continuous space in the memory/cache, thus enabling faster code execution in the processor. As building a trace needs runtime program information, a traditional compiler is unable to construct a trace. The term trace is also expressed as *path* or *fragment* in some optimizers, however they all refer to a sequence of instructions with a large amount of code reuse, although the details may differ slightly. To build traces, prediction algorithms are required in order to know which branch will be executed next. A good prediction algorithm could significantly improve program performance. A dynamic optimizer and the underlying hardware could both provide branch prediction. Section 2.5 and Section 2.5.4 will explain the difference between the two.

Based on its static characteristics, a compiler can offer various optimization algorithms to the whole program. An example is the well-known algorithm known as loop inlining. A dynamic optimizer can provide the same optimization algorithms as a compiler, however, as a dynamic optimizer has more runtime program information, it can also use this to choose to only apply optimization algorithms to certain regions of a program and skip others. This can avoid time being wasted on optimizing infrequently executed instructions. In dynamic optimizers, optimized traces are typically placed in a code cache. A *code cache* is a part of memory space allocated by an optimizer. Code that executes from the code cache is like executing natively. In different dynamic optimizers, the code cache is also called by different names, such as fragment cache, trace cache, path cache and basic block cache.

### 2.3 **Profiling Techniques**

Program profiling collects the specified offline or online information of the program. This information can be called by a programmer or another program to influence the optimization strategy to make the program run faster [34]. The *profile* information refers to the distribution of call sites, parameter values, the execution times of each basic block of the program and so on. As modern CPUs are becoming more and more complex [34], programmers have little knowledge to understand how their program interacts with such complicated hardware. Program profiling is thus an important step for program optimization.

*Offline profiling* is performed before the program executes. The statistics are gathered when the program runs one or more times. In contrast, an *online profiling* tool records the information during program execution. Hardware can provide profiling information directly. For example, Intel processors have hardware performance counters [1] which can gather detailed profile information such as cycles executed, data cache misses, data cache lines allocated, branches mis-prediction, instruction cost *et al.* Program Counter Sampling [13] can be exploited to analyse where time is spent in execution of a program.

Different types of optimization require different types of profile information. Three types of profile [23] are often used, namely control flow profile, value profile and address profile. *Control flow profile* records the program execution path, which can help determine the execution frequencies of certain paths of a program. *Value profile* obtains information about the specific values of operands as well as their frequency of occurrence. *Address profile* collects the memory addresses references, which can be used to apply data layout and placement transformations for improving the performance of the memory hierarchy.

Profile-guided optimization [36] is widely applied in the compiler and the optimizer as discussed in Section 2.7. Data flow and control flow analysis, described in the next section, are also ways to collect profile information.

### 2.4 Data Flow and Control Flow Analysis

Data flow and control flow analysis help to profile useful information for program optimization; these are usually performed on programs written in a high-level language. Some optimizations can be achieved by knowing various pieces of information obtained from inspecting the whole program; for instance, expression analysis for global redundancy elimination. Live variable analysis is helpful for global register allocation, dead variable elimination and uninitialized variable detection. Some statements may cause redundant re-computation of values. If such re-computation can be safely eliminated, the program may execute faster. It is also helpful to divide the program into blocks and analyse the control transfer information among the blocks. This helps the programmer to understand the program execution direction. One way of doing control flow analysis [46] is to note down the starting address of each block. The above analyses are known as data flow analysis and control flow analysis.

*Constant propagation* [43] is a well-known global data flow analysis whose goal is to discover a value that is constant during all its possible executions and propagate the constant value as far as possible through the program. The constant propagation technique serves several purposes for program optimization:

- Codes that are never executed can be deleted, for instance unreachable expressions or branches, which simplifies the program.

- It can reduce the number of memory accesses. Variables whose values stay constant during their execution period can be replaced by constants.

- It avoids unnecessary computation by replacing an expression which holds a set result (a constant) every time it is used.

While a program executes, some data values change sufficiently slowly that they can be identified as "glacial variables". Such glacial variables can be worthy of generating special-case code in which each value is treated as a constant for a period, thus enabling a cascade of optimizations [4]. These glacial variables are discovered through online data flow and control flow analysis. Such analysis is a modification of constant propagation analysis. It is composed of two parts. The first part is called global recursion level analysis, which labels the stage level of the loop and identifies their execution frequency. The outer loop is Stage 0 and inner loop is Stage n (n=1,2,3...). The second part is glacial variable propagation, which measures how frequently the value of the variable changes. The stage level (*e.g.* Stage 0, Stage 1...) is captured for the variable modified in a loop as well as the final value of variable exiting the loop. This is an interesting approach to optimization which is investigated further in Section 3.8.

### 2.5 **Optimization Techniques**

#### 2.5.1 Introduction

The rationales [3] behind code optimization consist of detecting patterns in the program and replacing the patterns by more efficient constructs. The replacement strategies can be machine-dependent or machine-independent. This thesis mainly takes account of machine-independent strategies. This section focuses on optimization techniques that either are contributing to optimizers' basic working procedures or as the basic concepts to guide more complex user-designed optimization algorithms to implement in optimizers. Software and hardware optimization methods are reviewed. A variety of software and hardware prediction mechanisms (Section 2.5.2 and Section 2.5.4) are surveyed, as prediction mechanisms play an important role for code optimization. Section 2.5.3 and Section 2.5.5 discuss optimization algorithms on a program and underlying hardware mechanisms for code reuse to speed up program execution.

Optimization techniques reviewed in this section are the common and basic optimization strategies. Section 2.6 and Section 2.7 focus on program optimizers work.

#### 2.5.2 Software Prediction

Dynamic optimizers usually incorporate software prediction algorithms to improve program performance. Prediction algorithms provide useful information for building traces as well as selecting appropriate regions for code optimization.

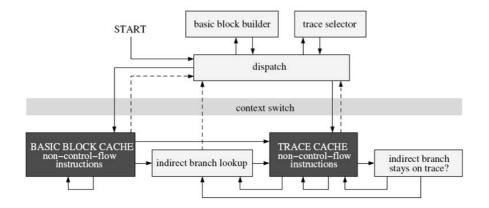

Dynamo (see Section 2.7.2), which is a dynamic optimizer, exploits a simple scheme for trace prediction: Most Recently Executed Tail (MRET). Dynamo starts a counter associated with a trace head. A backward taken branch (likely to be a loop head) or an exit branch from a previously hot trace is a candidate for a trace head. A counter keeps recording until it exceeds a threshold. When the counter reaches a threshold, the trace head is recorded. This simple scheme only records the trace head, as it is likely that, when an instruction or basic block becomes hot, its following instructions are also hot. Therefore, instead of profiling the rest of branch instructions, Dynamo predicts the tail of instructions following the hot trace head. This saves the storage space for the counter, as counters are only maintained for the potential loop head. MRET is called Next Executing Tail (NET) in later publications [19]. DynamoRIO, another dynamic optimizer (Section 2.7.3), utilises NET with a small change to control the overhead. In NET, it considers all backward branches as a trace head, DynamoRIO ignores backward indirect branches so that the number of trace heads is reduced. More trace heads may lead to larger numbers of tiny traces, which is undesirable.

Dynamic optimizers implement trace-based selection algorithms for hot-spot detection and construction. However, trace-selection algorithms suffer from two problems: trace separation and excessive code duplication [24]. Trace separation occurs when associated paths<sup>1</sup> are selected to be separate traces and these traces may be placed far apart from each other. This means there is always a delay when calling or identifying the next execution trace as well as the delay for control jumps between traces. The second problem stems from common parts of related traces; isolating these traces leads to code duplication. David *et al.* [24] give two prediction algorithms to solve the above problems: region-selection algorithms which are Last-Executed Iteration algorithm (LEI) and trace-combination algorithm.

LEI is similar to NET but surpasses NET when identifying cyclic paths<sup>2</sup> of execution. As in NET, LEI first searches whether the target branch is in the code cache. Working from the code cache is more efficient than working by emulation (more details are given in Section 2.7.3). If the target branch is in the code cache, control is transferred to the code cache, otherwise it is retrieved from the branch historic buffer. A hashtable is provided to make the retrieval more efficient. Only a cyclic path is selected from the historic buffer. The branches in the buffer are removed when selected to form a trace. Trace-combination is an extension of trace selection, it simply rejoins certain frequently-executed traces to prevent excessive code duplication. This operation requires space for caching traces before combination which causes a memory overhead even if only a compact representation of each trace is stored.

#### 2.5.3 Optimization Algorithms in Software

#### **Optimization Methods for Array References**

Compilers apply two approaches [3] that permit array references as operands:

• The reference to the array will not change until the code generation phase. It is in the code generation phase that the offset of an array and its base address are generated. And then an indexing operation is performed.

<sup>&</sup>lt;sup>1</sup> Path in Section 2.5.2 is not the terminology that is used in dynamic optimizers, but the literal meaning.

$<sup>^{2}</sup>$  A *cyclic path* is simply a path that ends with a branch to its beginning.

#### 2.5. OPTIMIZATION TECHNIQUES

The array references are expanded into three-address statements that do the offset calculation. The three-address statement is typically of the general form A:=B op C. Where A, B and C can be a programmer-defined name (a constant or compiler-generated temporary name) and op stands for any operator (such as an arithmetic operator). This approach is widely applied for optimization of array reference in loops to improve locality of reference in memory. *E.g.*, assuming a two-dimensional 10x20 array A, A[i,j] is in location *addr*(*A*)+20(*i*-1)+*j*-1 which is equal to (*addr*(*A*)-21)+20*i*+*j*. The machine code to reference A[i,j] will compute 20*i*+*j* in an index register. The three-address statement to evaluate the element of an A[i,j] into a temporary T would look like this: code to evaluate i into temporary T1 *T2:=20\*T1*

code to evaluate j into temporary T3

$$T4:=T2+T3$$

T:=(addr(A)-21)+[T4]

Usually there is a base register for storing the starting address of the array, so the compiler can determine the starting addresses at the beginning of the program. The offset is calculated either by the final compilation phase (code generation phase) or by the loader.

The details of optimization for array references are beyond the scope of the thesis; more information can be found in [3].

#### **Inner Loop**

It is generally accepted that most of the running time is spent in a small part of a program: for example, 90% of the time is used by 10% of the program. So the "inner loop", the most-frequently executed part, is the first target for code optimization.

The running time of a program may decrease when the length of an inner loop is shortened, even when the number of instructions outside the loop increases. Induction variable elimination can reduce the number of arguments in a loop by merging variables. Choosing cheaper operations, for instance substituting multiplications by additions, can improve the performance. This optimization is called strength reduction. On top of that, loop unrolling [3] and loop jamming [3] can sometimes be utilized to make the loop execute more quickly.

#### 2.5.4 Hardware Prediction

#### **Branch Prediction**

Hardware provides schemes [14, 33] to perform branch prediction. The simplest strategy is the so-called one-bit branch prediction buffer [29]. The buffer is a small memory indexed by the least significant bits of the branch instruction address. It incorporates a bit specifying whether the branch is recently taken or not: 1 is for taken, 0 is for not-taken. The bit will be inverted if the branch prediction turns out to be wrong. For example, bit=1 indicates that the associated branch is predicted to be taken when next executed. A slightly more complicated but more reliable branch prediction uses two bits for branch prediction. The value is between 0 and 3. Prediction must fail twice in succession before it is changed. Bits are incremented when branch is predicted as taken otherwise stays as 0 or decremented. Only 2 and 3 indicate that branch will be taken in the next round execution. Compared with 1-bit prediction, two-bit prediction can avoid the constant mis-prediction when a branch is taken and not-taken alternately.

#### **Value Prediction**

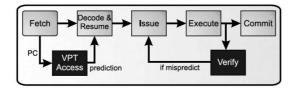

Value prediction [21, 30, 22] is similar to instruction reuse (see Section 2.5.5) but predicts the value of the input operands prior to execution. The procedure of value prediction is illustrated in Figure 2.1. This value prediction procedure is embodied in hardware. The predict value is obtained from a Value Prediction Table (VPT) which is implemented in hardware [20]. If the value predicted is wrong then the instructions have to re-execute, otherwise nothing needs to be done and the instruction completes earlier than without the prediction scheme.

Figure 2.1: Value prediction (taken from [20])

#### 2.5.5 Code Reuse in Hardware

#### **Instruction Reuse**

Some parts of the code are executed repeatedly during the lifetime of a program execution. Capitalizing on this, the results of previous operations, which can be instructions, basic blocks or traces, are cached so that they can be used again the next time they are detected [20]. According to Avinash *et al.* [37], there are three sources of instruction repeatability, as follows:

- The repetition of the input data being processed by a given program. Programs that manipulate texts can encounter the same characters (*e.g.* words, spaces) during execution.

- The repetition of loops and functions (methods). The instructions in a given loop are constantly repeated even though the processed data is different each time.

- There are data structures that have repeated access to their elements which leads to a repeated process.

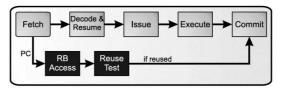

The instruction reuse procedure in a typical processor is demonstrated in Figure 2.2. The main principle behind instruction reuse [20] is that when an instruction with the same operands is repeated numerous times during program execution, the result of this instruction is fetched from a memory place instead of executing it via a function unit. As demonstrated in Figure 2.2, the first time an instruction runs, its result is cached in the Reuse Buffer (RB). The entries in the RB are indexed by Program Counter (PC). The next time the identical PC value is detected, the result is fetched from the RB. This procedure is done prior to fetching the actual instructions from memory. Before the commit phase, there is a reuse test to check if reuse is valid.

Figure 2.2: Instruction reuse in a typical processor (taken from [20])

The advantage [20] of instruction reuse is obvious. Instruction results cached in the RB, which could incur large delays, can be executed quickly, for instance multiplication and division. The reused instructions actually employ two pipelines as their path

instead of one pipeline on the processor, as illustrated in Figure 2.2. Due to instruction reuse, there are fewer accesses to the registers and memory. These effects potentially increase the number of instructions that can be executed concurrently, which leads to a reduction in execution time for a program.

Reuse also can be applied to more-than-one instructions at a time, as described below.

#### **Basic Block Reuse**

A *traditional basic block* is composed of a sequence of instructions with a single entry and single exit [20]. An entry point is a any instruction after a branch, subroutine call or return target. The exit point is a branch instruction or a return. Basic block reuse is similar to instruction reuse. The boundaries of the basic blocks are identified on the fly during the program execution. The information of basic blocks is cached in the Block History Buffer (BHB). Each basic block occupies one entry of the BHB. Every entry incorporates the information of register references, input and output context, PC, a bit indicating whether it is reused or not and the address of the following basic block.

#### **Trace Reuse**

A trace in this section is a traditional concept of trace. Different from the trace described in Section 2.2, a *traditional trace* is a larger sequence of instructions than that of a basic block. A reused trace is determined dynamically during program execution. Each time the first instruction of a reused trace is executed, the context of the trace is fetched from a special buffer and reconstructed. This procedure can avoid the execution of the trace on the processor. The *context* [15] here refers to information of integer registers, flag registers, instruction pointers and the program stacks.

### 2.6 Static Optimizers

#### 2.6.1 Introduction

A traditional compiler, for languages such as C, C++, even VHDL or Verilog, compiles programs once, producing a binary program that produces correct results under all inputs. Code optimization in such a compiler depends on the static analysis carried out at compile-time, often at an optimization level selected by the user. Static compilers employ some very sophisticated analyses [3] but are unable to optimize around variables whose values may change during program execution. Static optimization is performed ahead of execution, making runtime profile information unavailable.

However, static optimization shows a significant advantage over dynamic optimization. It is not concerned about the overhead caused by optimization operations. All the optimization operations are carried out before program execution, and the optimization overhead will not have negative effect on the code execution speed. For applications with little amount of code reuse or short execution, static optimization works well.

In the following three sections, three important static optimizers, MAO, Superoptimizer and peephole optimizer are reviewed. Introduction to some background technologies and techniques for static optimizers helps to understand the underlying working mechanism differences between static and dynamic optimizers. However, dynamic optimizers may also utilise the same techniques or algorithms that are employed in static optimizers. Chapter 3 utilises some techniques from MAO. Some background on MAO is important for better understanding the dynamic optimization algorithms used in Chapter 3. Since static optimization is not the main concern of this thesis, only three static optimizers are reviewed here.

### 2.6.2 MAO

MAO [25] is an extensible micro-architecture optimizer, seeking to address the problem of undocumented and puzzling performance cliffs of the X86/84 processors. MAO is a thin wrapper around an assembler infrastructure, GNU assembler (gas). The assembler accepts an input assembly file and converts it into an intermediate representation (IR). The optimization is performed on the IR and the results are output as IR into another assembly file. Code optimization in MAO is fully static.

MAO cooperates with the GNU assembler (gas); the input is parsed with gas's table driven encoder which encodes each input instruction into a single C *struct* type. Such encoded instruction sequences become a part of MAO's IR. Although MAO only performs static optimization, it can be integrated into a dynamic code generator easily because all the intermediate instructions are represented by a single C structure. MAO provides several types of optimization for IR, such as alignment optimization, experimental optimization and scheduling optimization [25].

In [25], the authors use a novel method of simply inserting or removing *nop* instructions, which makes the program gain performance improvement in some cases. The paper states the rationales behind how performance is improved. These are described as follows:

- The Intel platform comprises a Loop Stream Detector (LSD), which can bypass instruction fetching and decoding under certain circumstances. The loop must execute at least 64 iterations, cannot span more than four 16-byte decoding line and may not incorporate certain branches (more details are in the Intel manual [2]). The requirements may vary for different CPU vendors. When a loop meets the requirements to invoke LSD by inserting a certain number of *nops*, LSD can boost the program performance.

- The branch predictor in some Intel platforms is indexed by 5 PC steps which are instruction fetching, decoding, execution, memory access and writeback. Two short backward branches whose target addresses are close to each other may share the same branch predictor information (the same entry in a branch prediction table). Inserting *nops* may potentially make the PC value reach 5 so that the two backward branches may hit separate branch predictor spots. By appropriately padding *nops*, the correct branch prediction rate increases leading to saving of CPU cycles.

- Moreover, it is helpful to insert a random number of *nops* in a program. The idea behind this is that codes get shifted around to expose micro-architectural cliffs via inserting instructions. For example, this may result from removing unknown alias constraints in the branch predictor.

This is another interesting approach to program optimization which is further investigated in Section 3.6.

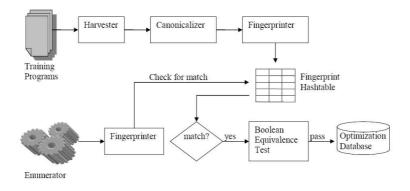

### 2.6.3 Superoptimizer

Superoptimizer [32] is a static code optimization system. It takes a program written in machine language as the input source and detects the shortest program which computes the same function as the source program through exhaustive search over all possible programs. In the first step, the op-codes of instruction sequences are stored in a table, the superoptimizer searches the table and generates all the possible combinations of the op-codes. The superoptimizer needs to determine whether the generated instructions perform the same function as the source program. This is achieved by *equivalence tests*. Two algorithms, referred to as *Boolean Test* and *Probabilistic Test*, are utilised to fulfil the equivalence test. In Boolean Test, the input arguments are changed to be the boolean-logic arguments at the beginning of a Boolean test. Two instructions are considered to be equivalent when their minterms of the Boolean arguments match. A minterm here is a special product of literals, in which each input variable appears exactly once. Boolean Test is a time-consuming procedure, so Henry Massalin [32] introduces a second method, Probabilistic Test, to achieve the same goal but execute faster. The basic idea is that of running the selected programs (the ones obtained from the first step) and testing their outputs to see if the results match the original program. The theory of Boolean Test and Probabilistic Test is out of the range of this thesis, more details can be found in Section 2.6.3. Massalin claims that only a few programs can pass such a test, and these successful programs will be inspected by a subsequent Boolean test again to compare their equivalence. Probabilistic Test largely reduces the memory requirements, as only a few boolean operations are left after the Probabilistic Test. To further decrease the search time, the superoptimizer filters the instruction sets that are not optimal by either Boolean Test or setting the rules manually. For example, by spotting the equivalent instruction sets and adding the new rule manually, so that the superoptimizer can replace the equivalent counterparts with a single instruction.