# Control of a Super-capacitor Based Energy Storage System

A thesis submitted to the University of Manchester for the degree of

Doctor of Philosophy

in the Faculty of Engineering and Physical Sciences

2013

by

Ding Wu

School of Electrical and Electronic Engineering

## List of contents

| LIST OF CON  | TENTSI                                                     |

|--------------|------------------------------------------------------------|

| LIST OF TABL | ES IV                                                      |

| LIST OF FIGU | RES V                                                      |

| LIST OF ABBI | REVIATIONSIX                                               |

| LIST OF SYM  | BOLSX                                                      |

| ABSTRACT     | XIV                                                        |

| DECLARATIO   | N XV                                                       |

| COPYRIGHT    | STATEMENT XVI                                              |

| DEDICATION   | XVII                                                       |

| ACKNOWLED    | DGEMENTS XVIII                                             |

| ABOUT THE    | AUTHORXIX                                                  |

| CHAPTER 1    | INTRODUCTION AND LITERATURE REVIEW1                        |

| 1.1 INTR     | ODUCTION1                                                  |

| 1.1.1        | More-electric Aircraft                                     |

| 1.1.2        | Energy storage system (ESS)                                |

| 1.1.3        | IEPNEF                                                     |

| 1.1.4        | Objectives4                                                |

| 1.2 LITER    | RATURE REVIEW                                              |

| 1.2.1        | Energy storage categories5                                 |

| 1.2.2        | Energy management strategies for the energy storage system |

| 1.2.3        | DC-DC converters for energy storage systems19              |

| 1.2.4        | Simulation methods                                         |

| 1.3 Sum      | MARY OF LITERATURE REVIEW                                  |

| 1.4 Scor     | PE OF THIS THESIS                                          |

| CHAPTER 2    | DUAL-INTERLEAVED CONVERTER WITH INTERPHASE-TRANSFORMER     |

| 2.1 INTR     | ODUCTION                                                   |

| 2.2 Boo      | ST MODE OPERATION                                          |

| 2.2.1        | Continuous conduction mode (CCM)                           |

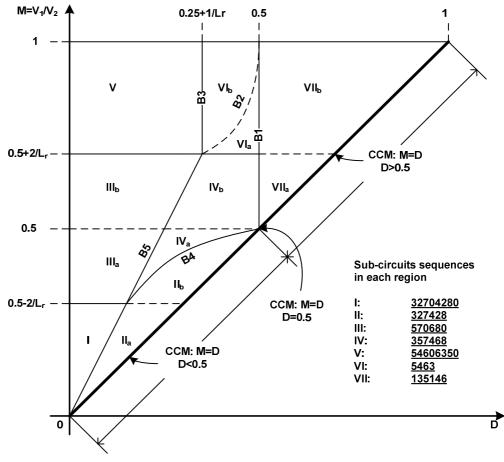

| 2.2.2        | Discontinuous conduction mode (DCM)                        |

| 2.2.3        | Saber simulation validation42                              |

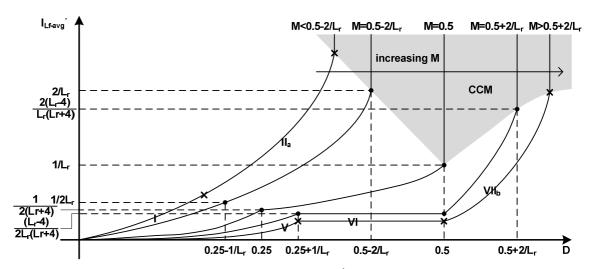

| 2.2.4        | Peak phase current and average inductor current45          |

| 2.3 Buci     | K MODE OPERATION                                           |

| 2.3.1        | Simplified analysis using symmetry characteristics         |

| 2.3.2        | Analysis of Buck mode CCM and DCM operation53              |

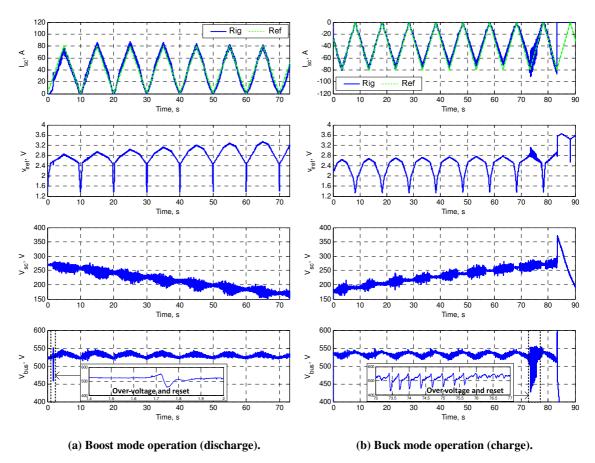

|              | RIMENTAL VALIDATION                                        |

| 2.4.1        | Boost DCM operation                                        |

| 2.4.2        | Buck DCM operation                                         |

|              |                                                            |

| 2.5 CON   | ICLUSION                                            | 66  |

|-----------|-----------------------------------------------------|-----|

| CHAPTER 3 | CONTROL OF EMULATED ENERGY STORAGE SYSTEM           | 67  |

| 3.1 INTR  | RODUCTION                                           | 67  |

| 3.2 ESS   | SYSTEM DESCRIPTION                                  | 67  |

| 3.2.1     | ESS system modelling                                |     |

| 3.2.2     | ESS system controller                               |     |

| 3.3 ESS   | SIMULATION IN DC ELECTRICAL SYSTEM                  | 77  |

| 3.3.1     | Simulation configuration                            | 77  |

| 3.3.2     | Simulation results                                  | 79  |

| 3.4 ESS   | EMULATION IN THE IEPNEF DC ELECTRICAL SYSTEM        | 85  |

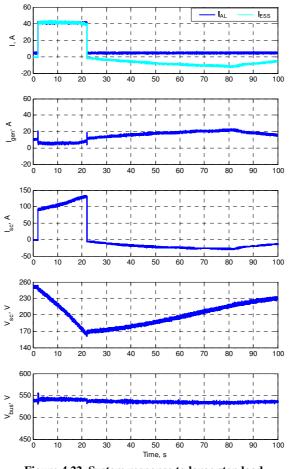

| 3.4.1     | Experiment configuration                            | 85  |

| 3.4.2     | Experimental validation                             | 87  |

| 3.5 CON   | ICLUSION                                            | 92  |

| CHAPTER 4 | ADVANCED CONTROL FOR AN ENERGY STORAGE SYSTEM       | 93  |

| 4.1 INTR  | RODUCTION                                           | 93  |

| 4.2 GEN   | ieral analysis of an ESS                            |     |

| 4.2.1     | Steady-state analysis                               |     |

| 4.2.2     | Dynamic response analysis                           |     |

| 4.3 Pro   | POSED CONTROL METHOD                                |     |

| 4.3.1     | Proposed steady-state SoC control                   |     |

| 4.3.2     | Proposed dynamic response control                   |     |

| 4.4 GEN   | ERIC ESS SIMULATION                                 |     |

| 4.4.1     | Simulation model                                    |     |

| 4.4.2     | Control design                                      |     |

| 4.4.3     | Simulation results                                  |     |

| 4.5 SUP   | ER-CAPACITOR BASED ESS SIMULATION                   |     |

| 4.5.1     | Simulation model                                    |     |

| 4.5.2     | Control design                                      |     |

| 4.5.3     | Simulation results                                  |     |

| 4.6 Pra   | CTICAL IMPLEMENTATION AND EXPERIMENTAL TEST RESULTS |     |

| 4.6.1     | Experimental test system                            |     |

| 4.6.2     | Energy storage system design and control            |     |

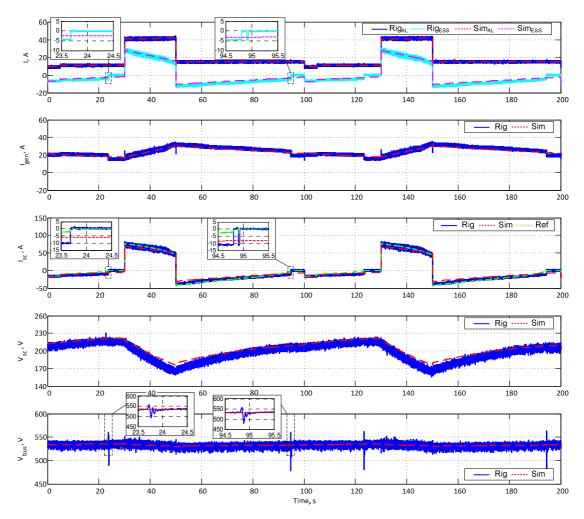

| 4.6.3     | Experimental Validation                             |     |

| 4.7 Con   | ICLUSIONS                                           | 136 |

| CHAPTER 5 | CONCLUSIONS AND FURTHER WORK                        |     |

|           | ODUCTION                                            |     |

|           | IMARY OF THE THESIS                                 |     |

| 5.2.1     | DCM converter analysis                              |     |

| 5.2.2     | ESS simulation and emulation                        |     |

| 5.2.3     | Advanced ESS control                                |     |

|           | ITRIBUTIONS OF THIS RESEARCH                        |     |

| 5.3.1     | DCM converter analysis                              |     |

|      | 5.3.2                                           | ESS simulation and emulation                                   | 142 |

|------|-------------------------------------------------|----------------------------------------------------------------|-----|

|      | 5.3.3                                           | Advanced ESS control                                           |     |

| 5.   | 4 Sugg                                          | ESTIONS FOR FUTURE WORK                                        | 143 |

|      | 5.4.1                                           | More advanced converter control                                |     |

|      | 5.4.2                                           | DC-DC converter for ESS                                        |     |

|      | 5.4.3                                           | More advanced energy management strategies                     |     |

|      | 5.4.4                                           | Fault ride through capability of the ESS                       | 144 |

| 5.   | 5 Cond                                          | CLUSIONS                                                       | 144 |

| REFE | RENCES.                                         |                                                                | 146 |

| APPE | NDICES.                                         |                                                                | 157 |

| А    | Dual-inte                                       | RLEAVED CONVERTER WITH IPT                                     | 157 |

|      | A.1 Transform of coupled inductors into an IPT1 |                                                                | 157 |

|      | A.2 Calc                                        | ulation of terminal voltage for the IPT                        | 158 |

|      | A.3 di <sub>L1/</sub>                           | /dt and di <sub>L2</sub> /dt calculation                       | 160 |

|      | A.4 Bou                                         | ndary conditions of the DCM modes                              | 163 |

|      | A.5 Sab                                         | er circuit diagram of the dual-interleaved converter           | 166 |

|      | A.6 Pea                                         | k current and average current equations                        | 167 |

| В    | ENERGY ST                                       | ORAGE SYSTEM                                                   | 171 |

|      | B.1 Ave                                         | raged DC-DC converter model for the ESS                        |     |

|      | B.2 Sim                                         | ulink model of the energy storage system                       |     |

|      | B.3 Dyn                                         | amic load emulation using the active load                      |     |

|      | B.4 Gra                                         | phical user interface for the active load                      |     |

|      | B.5 Deri                                        | ivation of E versus $P_s$ trajectory for a load step           |     |

|      | B.6 Imp                                         | lementation of control reference v <sub>iref</sub> calculation |     |

Final word count: 49300

## List of tables

| TABLE 1.1 BATTERY TECHNOLOGIES SUMMARY [50]                                              | 9   |

|------------------------------------------------------------------------------------------|-----|

| TABLE 2.1. TERMINAL VOLTAGES $V_{\tau 1}$ and $V_{\tau 2}$ in different DCM sub-circuits | 39  |

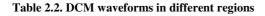

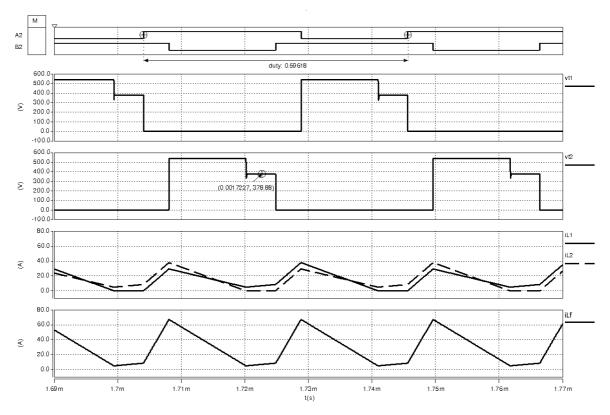

| TABLE 2.2. DCM WAVEFORMS IN DIFFERENT REGIONS                                            | 41  |

| TABLE 2.3. SUMMARY OF DCM BOUNDARY DUTY RATIOS IN BOOST MODE                             | 42  |

| TABLE 2.4. SUMMARY OF DCM BOUNDARY DUTY RATIOS IN BUCK MODE                              | 54  |

| TABLE 2.5. CONVERTER DETAILS IN EXPERIMENTS                                              | 57  |

| TABLE 3.1. SIMULATION PARAMETERS                                                         | 77  |

| TABLE 3.2. PARAMETERS OF THE LOAD PROFILES                                               | 87  |

| TABLE 4.1. PARAMETERS OF PEAK CURRENT CONTROLLER                                         | 121 |

| TABLE A.1. TRANSFORM OF COUPLED INDUCTORS                                                     | 157 |

|-----------------------------------------------------------------------------------------------|-----|

| TABLE A.2 VOLTAGES AND DI/DT OF CIRCUIT ELEMENTS IN BOOST MODE                                | 161 |

| TABLE A.3. VOLTAGES AND DI/DT OF CIRCUIT ELEMENTS IN BUCK MODE                                | 162 |

| TABLE A.4. PHASE CURRENT WAVEFORMS AT BOUNDARY                                                | 163 |

| TABLE A.5. SUMMARY OF AVERAGE INDUCTOR CURRENT AND PEAK CURRENT FOR DCM REGIONS IN BOOST MODE | 169 |

| TABLE A.6. SUMMARY OF AVERAGE INDUCTOR CURRENT AND PEAK CURRENT FOR DCM REGIONS IN BUCK MODE  | 170 |

## List of figures

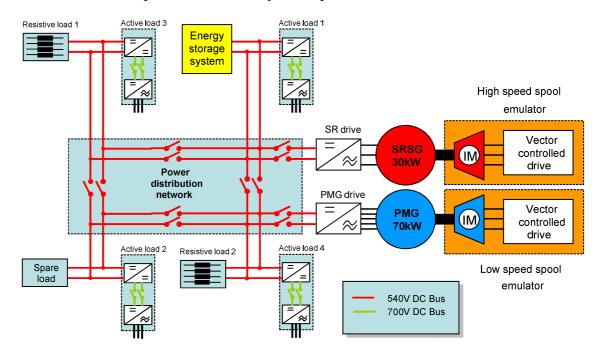

| FIGURE 1.1. IEPNEF SYSTEM DIAGRAM                                                                                            | 3 |

|------------------------------------------------------------------------------------------------------------------------------|---|

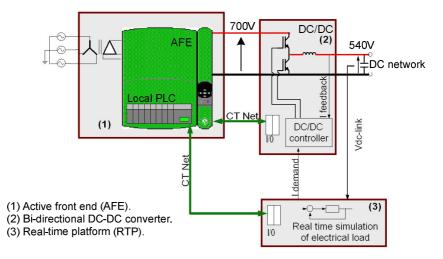

| FIGURE 1.2. DIAGRAM OF ACTIVE LOAD SYSTEM [8]                                                                                | 4 |

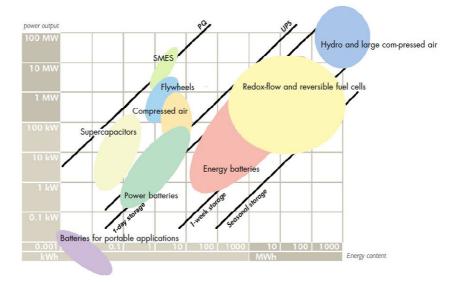

| FIGURE 1.3. POWER AGAINST ENERGY PLOT FOR VARIOUS ENERGY STORAGE TECHNOLOGIES [32]11                                         | 1 |

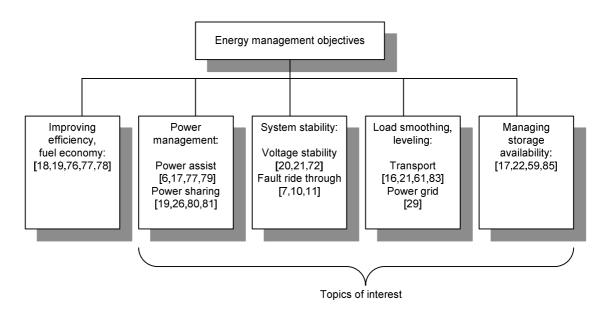

| FIGURE 1.4. ENERGY MANAGEMENT OBJECTIVES                                                                                     | 2 |

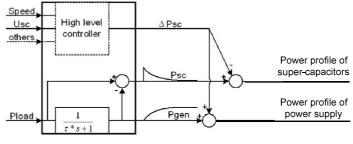

| FIGURE 1.5. CONTROL STRATEGIES OF USING LPF IN [83]                                                                          | 5 |

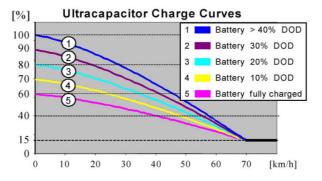

| FIGURE 1.6. STATE-OF-CHARGE OF SUPER-CAPACITOR AGAINST VEHICLE SPEED AND BATTERY DOD [59]                                    | 7 |

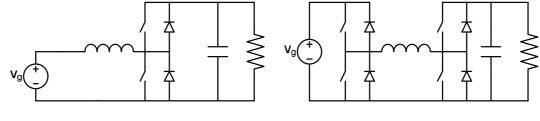

| FIGURE 1.7. BASIC NON-ISOLATED DC-DC CONVERTER TOPOLOGIES                                                                    | C |

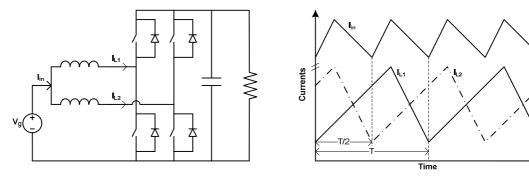

| FIGURE 1.8. INTERLEAVED BI-DIRECTIONAL HALF-BRIDGE CONVERTER AND ITS OPERATING WAVEFORMS                                     | 1 |

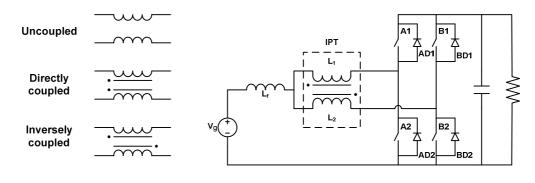

| FIGURE 1.9. INDUCTOR COUPLING ARRANGEMENTS AND THE DUAL INTERLEAVED CONVERTER WITH IPT                                       | 1 |

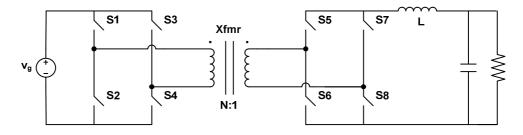

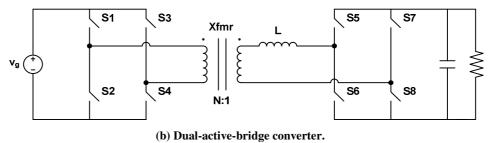

| FIGURE 1.10. TOPOLOGIES OF BI-DIRECTIONAL DC-DC CONVERTERS [111]                                                             | 3 |

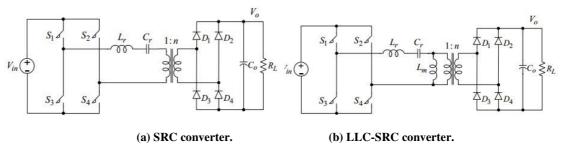

| FIGURE 1.11. TWO ISOLATED CONVERTER CIRCUIT DIAGRAMS                                                                         | 4 |

| FIGURE 1.12. SRC AND LLC-SRC CONVERTERS [136]25                                                                              | 5 |

| FIGURE 1.13. PEAK CURRENT CONTROL                                                                                            | 5 |

| FIGURE 1.14. COMPARISON OF SI, SIC AND GAN SEMICONDUCTOR DEVICES [145]                                                       | 7 |

| FIGURE 2.1. CIRCUIT DIAGRAM OF THE CONVERTER                                                                                 | 2 |

| FIGURE 2.2. SUB-CIRCUITS IN CCM BOOST MODE                                                                                   | 4 |

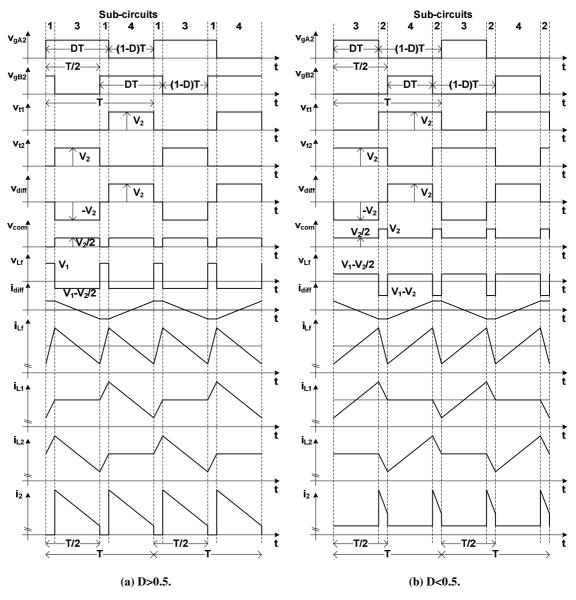

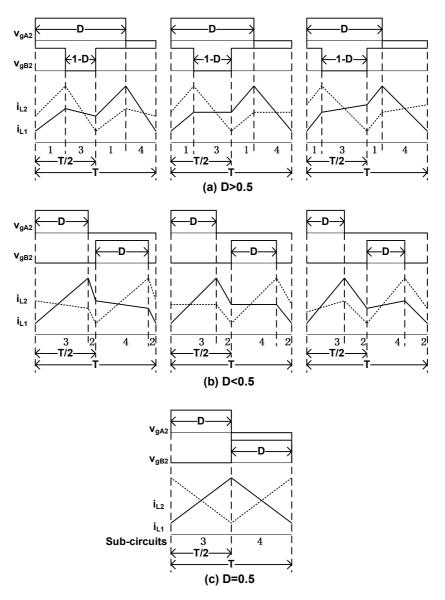

| FIGURE 2.3. OPERATING WAVEFORMS IN CCM BOOST MODE                                                                            | 5 |

| FIGURE 2.4. PHASE CURRENTS WAVEFORMS IN CCM BOOST MODE                                                                       | 5 |

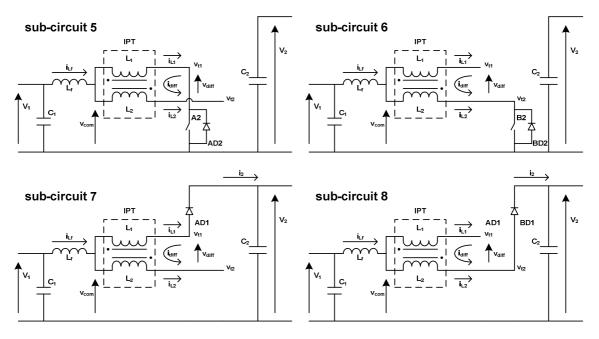

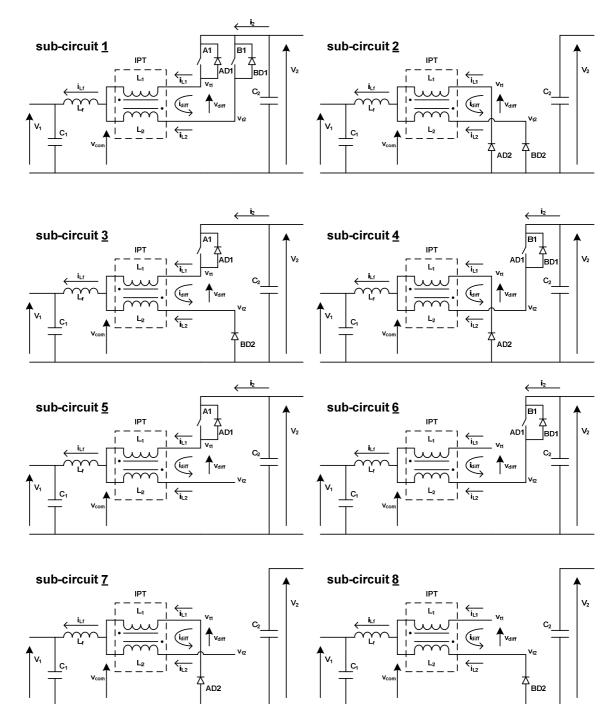

| FIGURE 2.5. ADDITIONAL FOUR SUB-CIRCUITS APPEARING IN DCM OPERATION, BOOST MODE                                              | 3 |

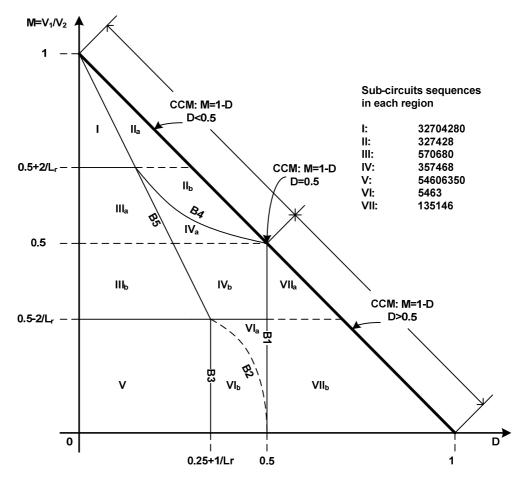

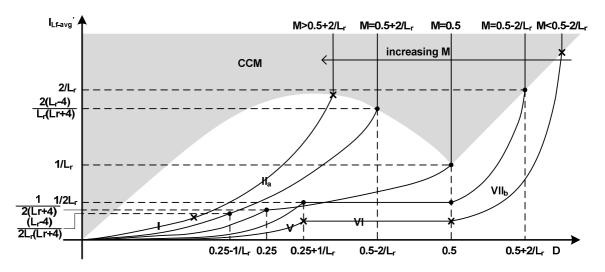

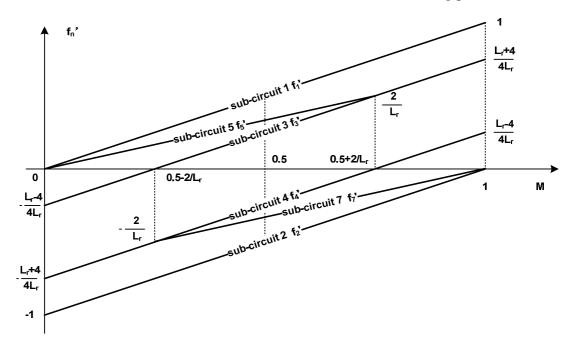

| FIGURE 2.6. DCM OPERATING REGIONS IN BOOST MODE                                                                              | ) |

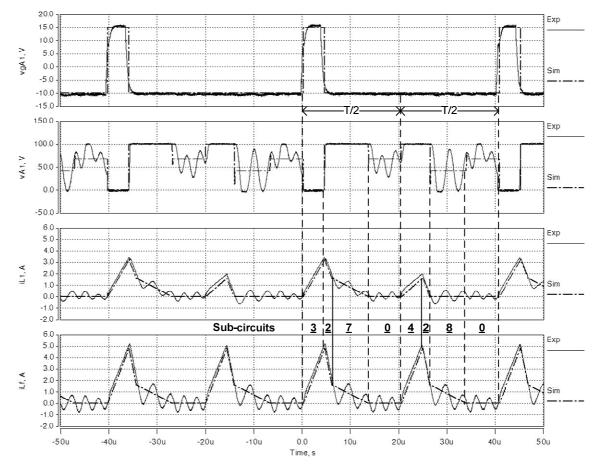

| Figure 2.7. Saber simulation waveforms in boost mode, $V_1$ =200V, $V_2$ =540V, M=0.37, D=0.6, f=24kHz L <sub>r</sub> =71.7, |   |

| L <sub>F</sub> =13.60H, REGION VII <sub>B</sub> 43                                                                           | 3 |

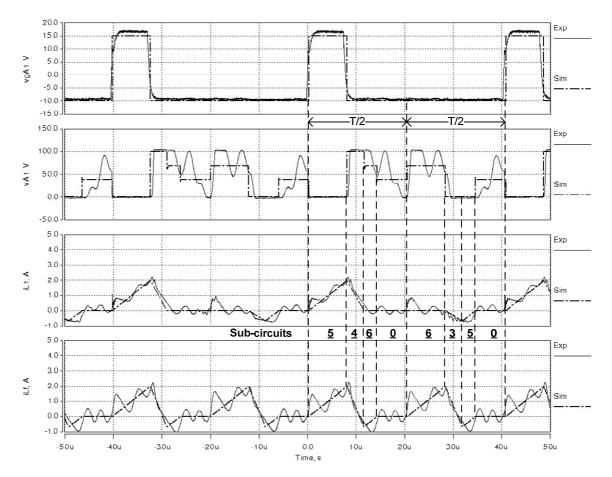

| Figure 2.8. Saber simulation waveforms in boost mode, $V_1$ =275V, $V_2$ =540V, M=0.509, D=0.3, F=24KHz, $L_R$ =71.7,        |   |

| L <sub>F</sub> =13.60H, REGION IV <sub>A</sub> 44                                                                            | 4 |

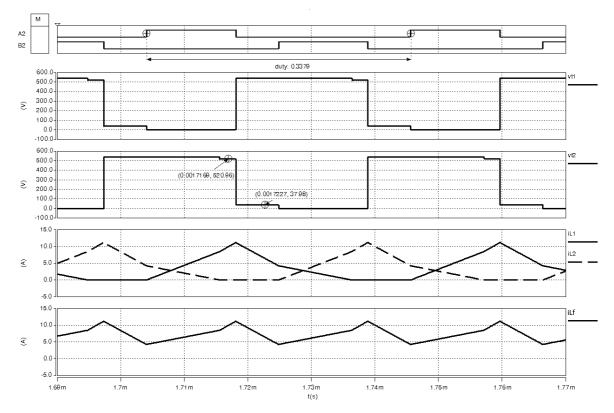

| Figure 2.9. Illustration of defined variables, $I_{L1[K]}$ , $\Delta T_{[K]}$ 45                                             | 5 |

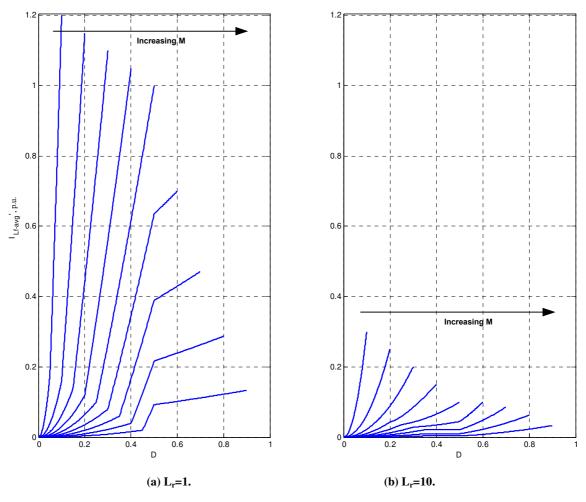

| Figure 2.10. Characteristics of normalized average inductor current $I_{LF-AVG}$ against D for different M, $L_R>4$ ,        |   |

| BOOST MODE                                                                                                                   | 7 |

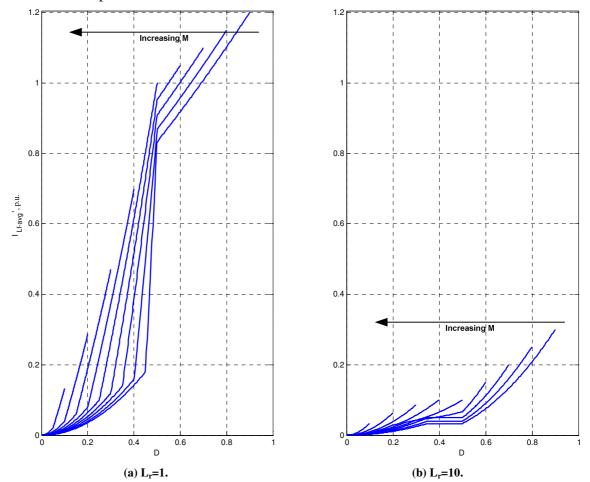

| Figure 2.11. Characteristics of normalized average inductor current $I_{LF-AVG}$ against duty ratio D, boost mode, M                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INCREASING FROM 0.1 TO 0.9 IN STEPS OF 0.1                                                                                                                      |

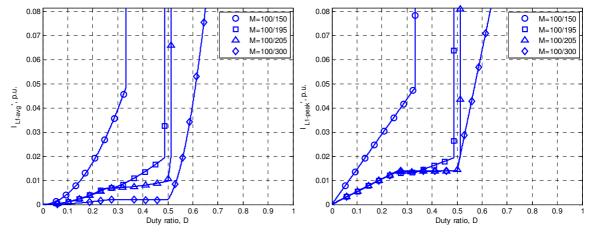

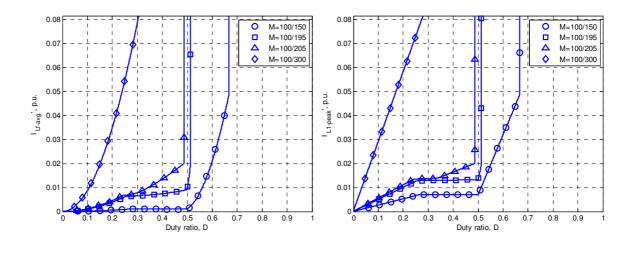

| FIGURE 2.12. COMPARISON OF AVERAGE INDUCTOR CURRENT BETWEEN THE CALCULATED VALUES (SOLID LINES) AND SABER                                                       |

| SIMULATION RESULTS (MARKERS), $V_1$ =100V, $L_F$ =13.60H, $L_R$ =71.7, boost mode, rated current $I_{BASE}$ =4.27A49                                            |

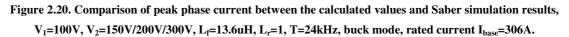

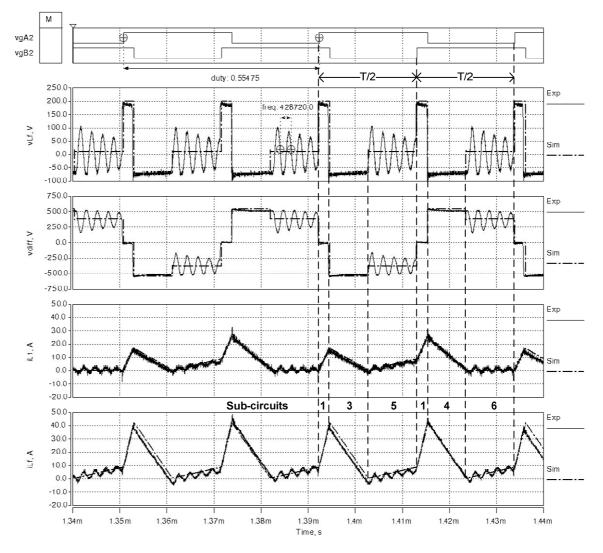

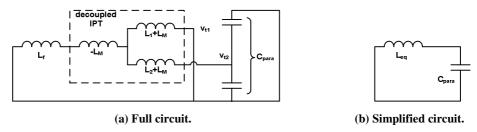

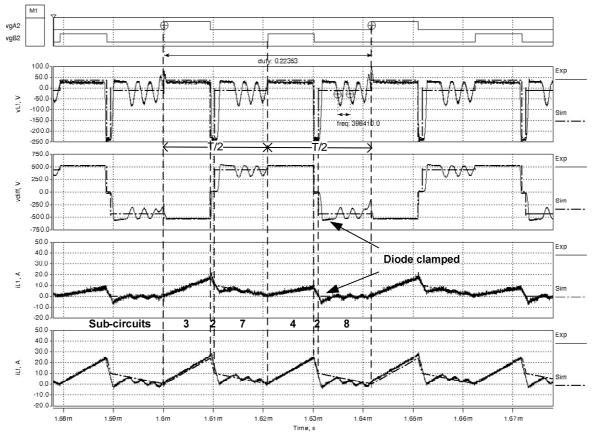

| FIGURE 2.13. COMPARISON OF PEAK PHASE CURRENT BETWEEN THE CALCULATED VALUES (SOLID LINES) AND SABER SIMULATION                                                  |

| results (markers), $V_1$ =100V, $L_F$ =13.60H, $L_R$ =1, boost mode, rated current $I_{BASE}$ =306A50                                                           |

| FIGURE 2.14. SUMMARY OF SUB-CIRCUITS IN BUCK MODE                                                                                                               |

| FIGURE 2.15. NORMALIZED RATE OF RISE IN PHASE CURRENT DIL1/DT AGAINST VOLTAGE RATIO M FOR BOOST MODE                                                            |

| FIGURE 2.16. DCM OPERATING REGIONS IN BUCK MODE                                                                                                                 |

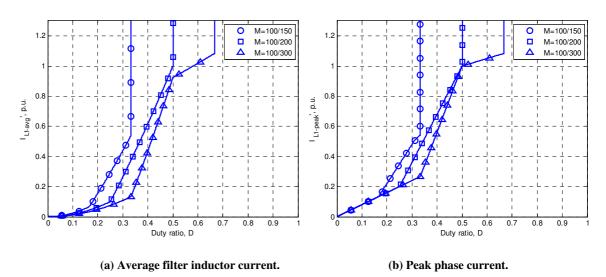

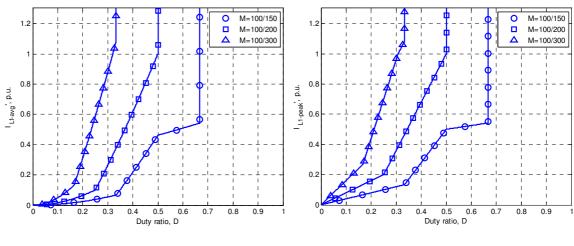

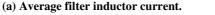

| FIGURE 2.17. CHARACTERISTICS OF AVERAGE INDUCTOR CURRENT ILF-AVG AGAINST D FOR DIFFERENT M, L <sub>R</sub> >4, BUCK MODE55                                      |

| FIGURE 2.18. CHARACTERISTICS OF NORMALIZED AVERAGE INDUCTOR CURRENT ILF-AVG' AGAINST D, BUCK MODE, M INCREASING                                                 |

| FROM 0.1 TO 0.9 IN STEPS OF 0.1                                                                                                                                 |

| FIGURE 2.19. COMPARISON OF AVERAGE INDUCTOR CURRENT BETWEEN THE CALCULATED VALUES AND SABER SIMULATION                                                          |

| results, $V_1$ =100V, $L_F$ =13.60H, $L_R$ =71.7, buck mode, rated current $I_{BASE}$ =4.27A56                                                                  |

| FIGURE 2.20. COMPARISON OF PEAK PHASE CURRENT BETWEEN THE CALCULATED VALUES AND SABER SIMULATION RESULTS,                                                       |

| V <sub>1</sub> =100V, L <sub>F</sub> =13.60H, L <sub>R</sub> =1, BUCK MODE, RATED CURRENT I <sub>BASE</sub> =306A57                                             |

| FIGURE 2.21. BOOST MODE, REGION VII <sub>B</sub> , CONVERTER A, D=55.4%, V <sub>1</sub> =200V, V <sub>2</sub> =530V, I <sub>LF-AVG</sub> =13.6A, 13.4A, 12.5A   |

| (from theoretical, simulation and measurement respectively) , R=120 $\Omega$                                                                                    |

| FIGURE 2.22. EQUIVALENT CIRCUIT FOR THE PARASITIC RINGING ANALYSIS                                                                                              |

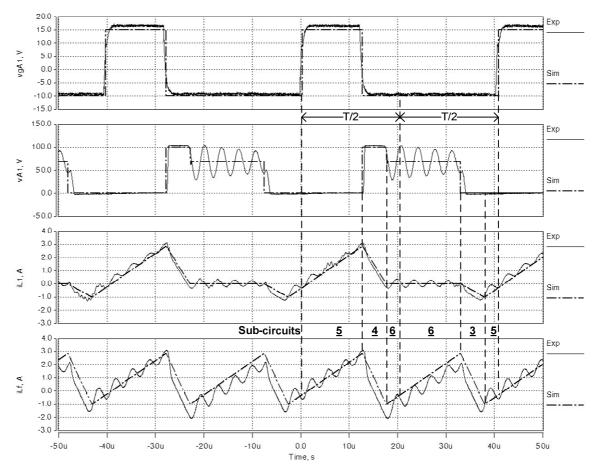

| Figure 2.23. Boost mode, region II <sub>a</sub> , converter A, D=22.3%, V <sub>1</sub> =300V, V <sub>2</sub> =530V, I <sub>LF-AVG</sub> =8.7A, 8.7A, 8.2A (from |

| Theoretical, simulation and measurement respectively), R=120 $\Omega$ 61                                                                                        |

| FIGURE 2.24. BUCK MODE, CONVERTER B, D=10.8%, V <sub>1</sub> =32.9V, V <sub>2</sub> =100V, I <sub>LF-AVG</sub> =1.06A, 1.07A, 1.09A (FROM                       |

| Theoretical, simulation and measurement respectively), R=30 $\Omega$ , region I62                                                                               |

| FIGURE 2.25. BUCK MODE, CONVERTER B, D=19.3%, V <sub>1</sub> =62V,V <sub>2</sub> =100V, I <sub>LF-AVG</sub> =0.44A, 0.44A, 0.52A (FROM THEORETICAL,             |

| simulation and measurement respectively), R=120 $\Omega$ , region V63                                                                                           |

| Figure 2.26. Buck mode, converter B, D=31%, $V_1$ =62V, $V_2$ =100V, $I_{LF-AVG}$ =0.91, 0.90, 0.52A (from theoretical,                                         |

| simulation and measurement respectively), R=120 $\Omega$ , region VI64                                                                                          |

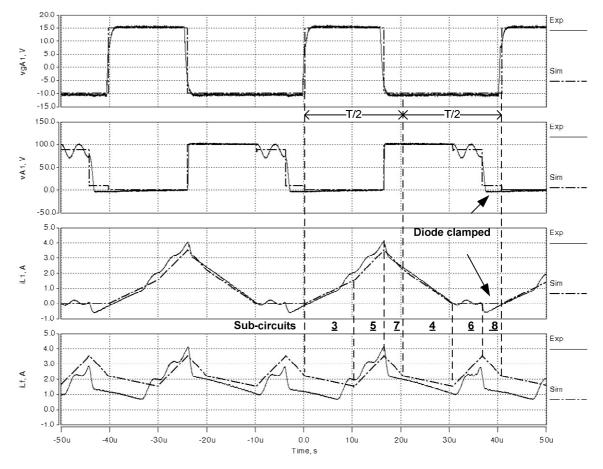

| Figure 2.27. Buck mode, converter B, D=40.1%, $V_1$ =51V, $V_2$ =100V, $I_{LF-AVG}$ =2.28A, 2.28A, 1.7A (from theoretical,                                      |

| simulation and measurement respectively), R=30 $\Omega$ , region IV $_{\scriptscriptstyle B}$ 65                                                                |

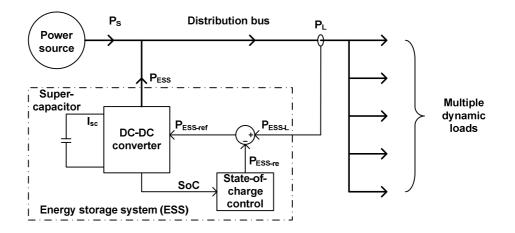

| FIGURE 3.1. SYSTEM DIAGRAM OF THE ESS AND THE DC DISTRIBUTION NETWORK                                                                                           |

| VI                                                                                                                                                              |

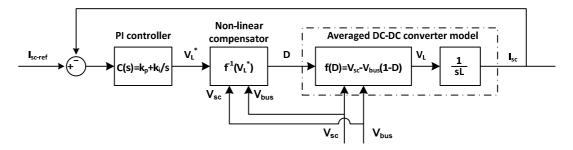

| FIGURE 3.2. POWER FLOW CHARACTERISTICS.                                                                                                                          | 68          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

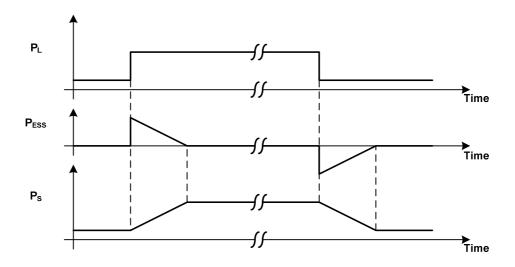

| FIGURE 3.3. MODEL OF THE ENERGY STORAGE SYSTEM IN THE DC DISTRIBUTION NETWORK                                                                                    | 69          |

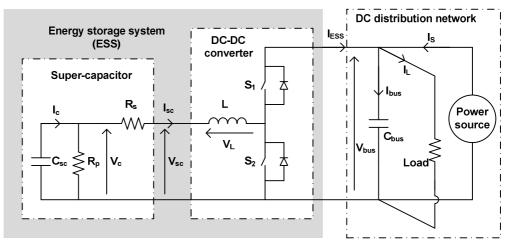

| FIGURE 3.4. SUPER-CAPACITOR CURRENT CONTROLLER USING THE NON-LINEAR COMPENSATOR.                                                                                 | 71          |

| FIGURE 3.5. TWO COMPONENTS OF THE SUPER-CAPACITOR CURRENT REFERENCE                                                                                              | 73          |

| FIGURE 3.6. CHARACTERISTIC OF P <sub>SC-RE</sub> AGAINST V <sub>SC</sub> , EQUATION (3.18).                                                                      | 76          |

| Figure 3.7. Simulation results of full power step load, $\kappa_1$ =0.64, $\kappa_2$ =1.5.                                                                       | 80          |

| FIGURE 3.8. CHARACTERISTICS OF $P_{sc-re}$ against $V_{sc}$ with different $\kappa_1$ and $\kappa_2$ parameters.                                                 | 81          |

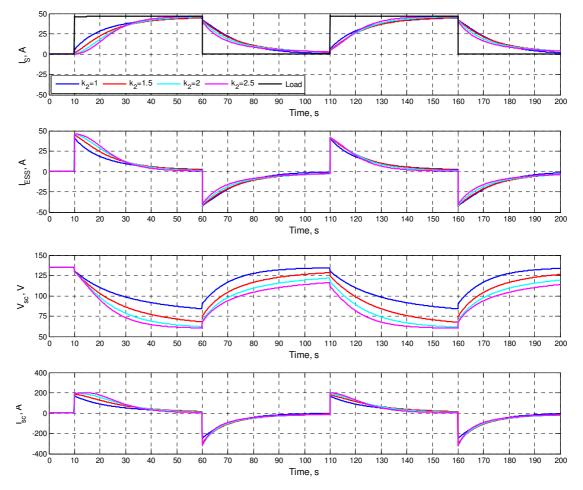

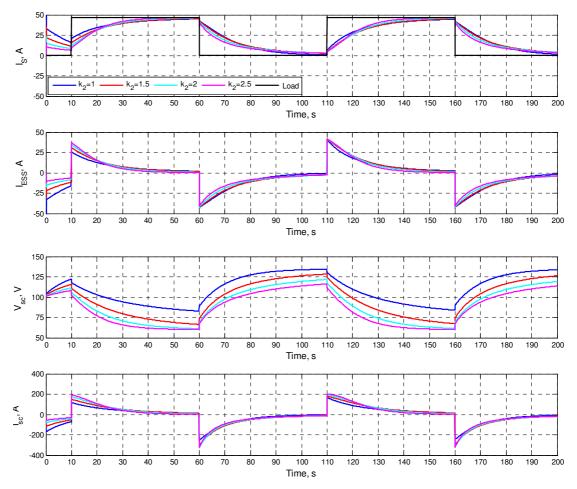

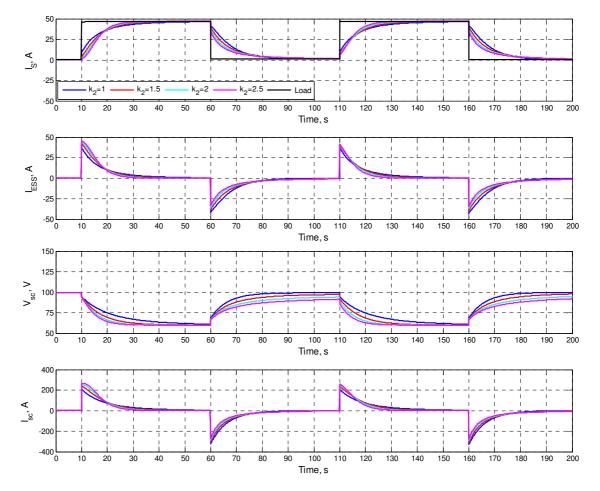

| FIGURE 3.9. SIMULATION RESULTS FOR FULL POWER STEP LOAD WITH DIFFERENT $K_1 K_2$ , INITIAL $V_{sc} = 135V$ , $V_{sc-max} = 135V$                                 | 82          |

| FIGURE 3.10. SIMULATION RESULTS FOR FULL POWER STEP LOAD WITH DIFFERENT K <sub>1</sub> K <sub>2</sub> , INITIAL V <sub>SC</sub> =100V, V <sub>SC-MAX</sub> =135V | 83          |

| Figure 3.11. Simulation results for full power step load with different $K_1 K_2$ , initial $V_{sc}$ =100V, $V_{sc-max}$ =100V                                   | 84          |

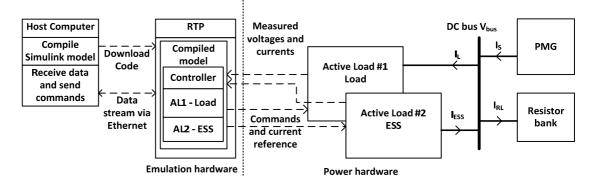

| FIGURE 3.12. STRUCTURE OF ADI RTP AND THE IEPNEF DC NETWORK.                                                                                                     | 85          |

| FIGURE 3.13. PROGRAMMABLE LOAD PROFILES.                                                                                                                         | 86          |

| FIGURE 3.14. EXPERIMENTAL RESULTS WITH ESS INACTIVE.                                                                                                             | 88          |

| FIGURE 3.15. EXPERIMENTAL RESULTS WITH ESS ACTIVE FOR RADAR LOAD.                                                                                                | 90          |

| FIGURE 3.16. EXPERIMENTAL RESULTS WITH ESS ACTIVE FOR HIGH FREQUENCY LOAD.                                                                                       | 91          |

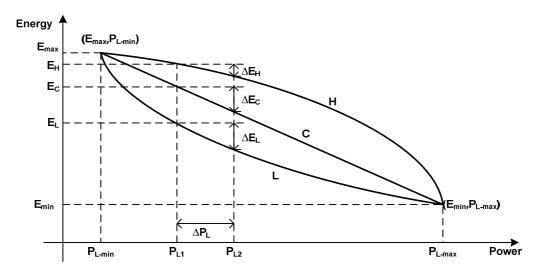

| FIGURE 4.1. SAMPLE STORED ENERGY AGAINST LOAD POWER PROFILES.                                                                                                    | 94          |

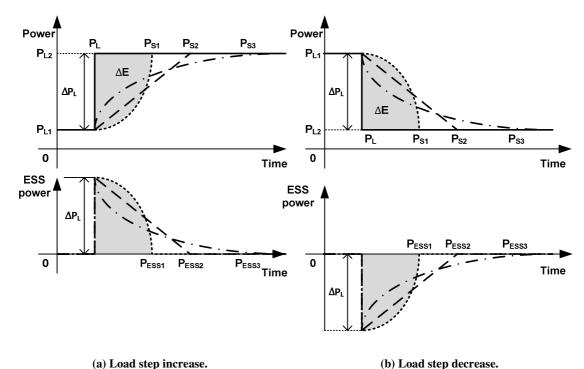

| FIGURE 4.2. THREE DIFFERENT POWER SOURCE RESPONSE PROFILES.                                                                                                      | 96          |

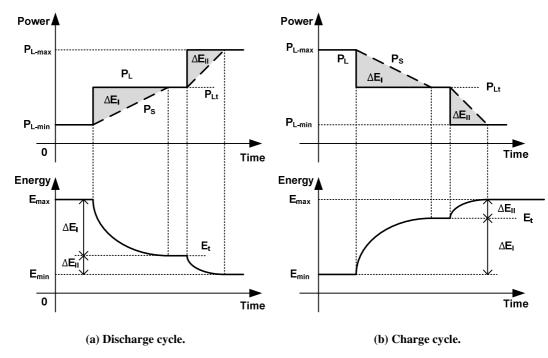

| FIGURE 4.3. FULL DISCHARGE AND CHARGE CYCLE OF THE ESS.                                                                                                          | 99          |

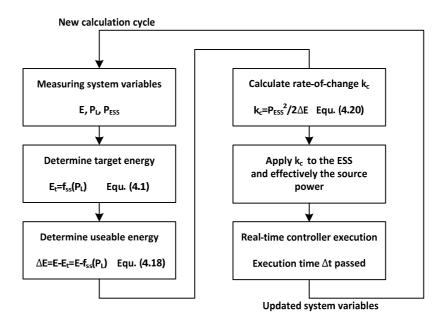

| FIGURE 4.4. FLOW CHART OF THE K <sub>c</sub> CALCULATION.                                                                                                        | .102        |

| FIGURE 4.5. P <sub>ESS-RE</sub> CONTROL USING RATE LIMITER                                                                                                       | .103        |

| FIGURE 4.6. THREE CONTROL PROFILES USED IN SIMULATION, L, C AND H                                                                                                | .104        |

| Figure 4.7. $\kappa_c$ values calculated for transition from $P_{L1}$ to $P_{L2}$                                                                                | .105        |

| FIGURE 4.8. SMALL LOAD STEPS RESPONSES.                                                                                                                          | .106        |

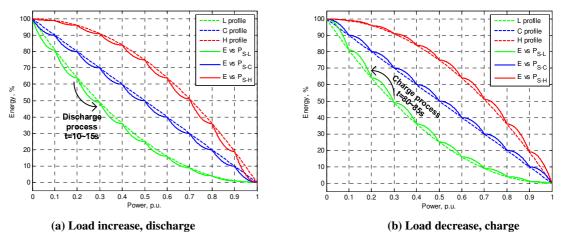

| FIGURE 4.9. ENERGY E AGAINST POWER SOURCE OUTPUT P <sub>S</sub> TRAJECTORIES                                                                                     | .107        |

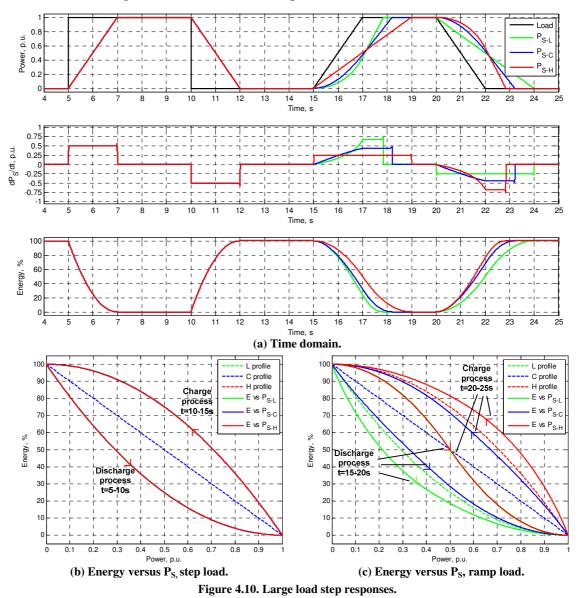

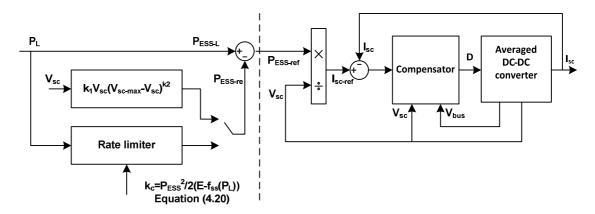

| FIGURE 4.10. LARGE LOAD STEP RESPONSES                                                                                                                           | .108        |

| FIGURE 4.11. SIMULATION MODEL OVERVIEW OF THE ESS WITH THE ADVANCED ENERGY MANAGEMENT CONTROLLER                                                                 | .110        |

| FIGURE 4.12. COMPARISON OF CONTROLLER PROFILES FOR THE SUPER-CAPACITOR BASED ESS.                                                                                | .112        |

| FIGURE 4.13. LOAD STEPS SIMULATION RESULTS.                                                                                                                      | .114        |

| FIGURE 4.14. RADAR LOAD SIMULATION RESULTS.                                                                                                                      | .116        |

| FIGURE 4.15. PULSED LOAD SIMULATION RESULTS                                                                                                                      |             |

|                                                                                                                                                                  | <b>X7TT</b> |

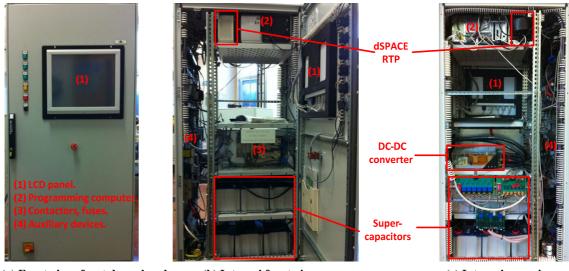

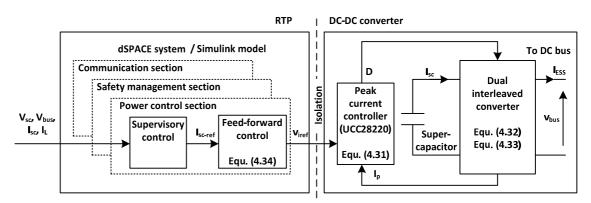

| FIGURE 4.16. ESS SYSTEM DIAGRAM FOR THE TEST.                                                                     | 118 |

|-------------------------------------------------------------------------------------------------------------------|-----|

| FIGURE 4.17. ENERGY STORAGE SYSTEM CABINET.                                                                       | 119 |

| FIGURE 4.18. ESS DSPACE RTP AND ITS CONNECTION TO THE POWER HARDWARE.                                             | 119 |

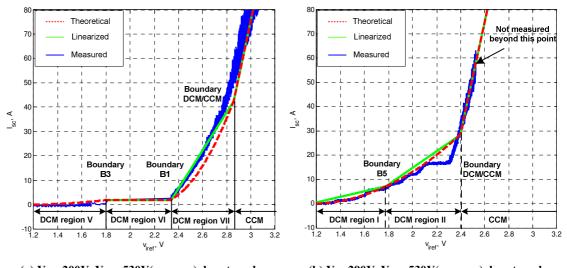

| Figure 4.19. Comparison between theoretical, linearized and measured characteristic of $I_{sc}$ versus $v_{iref}$ | 122 |

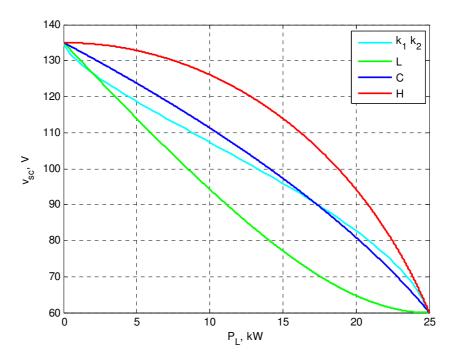

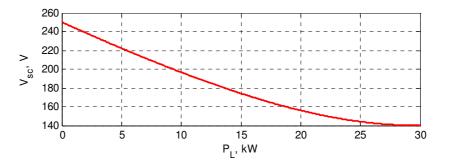

| FIGURE 4.20. STEADY-STATE SUPER-CAPACITOR VOLTAGE AGAINST LOAD POWER PL                                           | 125 |

| FIGURE 4.21. DETAILED ESS RESPONSE FOR TRIANGULAR I <sub>SC-REF</sub>                                             | 127 |

| FIGURE 4.22. SYSTEM RESPONSE TO LARGE STEP LOAD.                                                                  | 128 |

| FIGURE 4.23. OVERALL SYSTEM RESPONSE DUE TO HYPOTHETICAL RADAR LOAD.                                              | 130 |

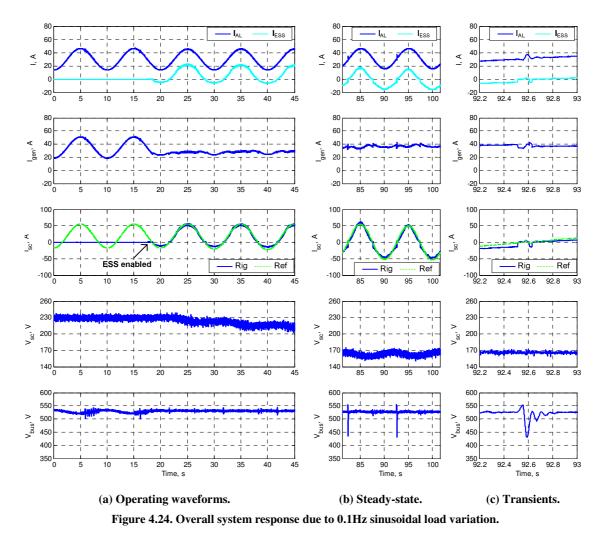

| FIGURE 4.24. OVERALL SYSTEM RESPONSE DUE TO 0.1HZ SINUSOIDAL LOAD VARIATION                                       | 132 |

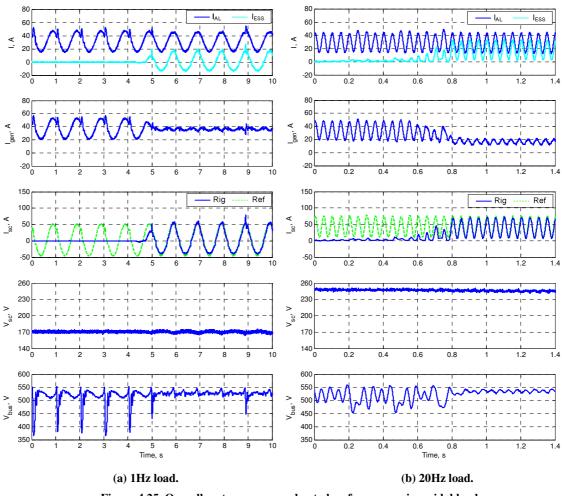

| FIGURE 4.25. OVERALL SYSTEM RESPONSE DUE TO LOW FREQUENCY SINUSOIDAL LOADS                                        | 133 |

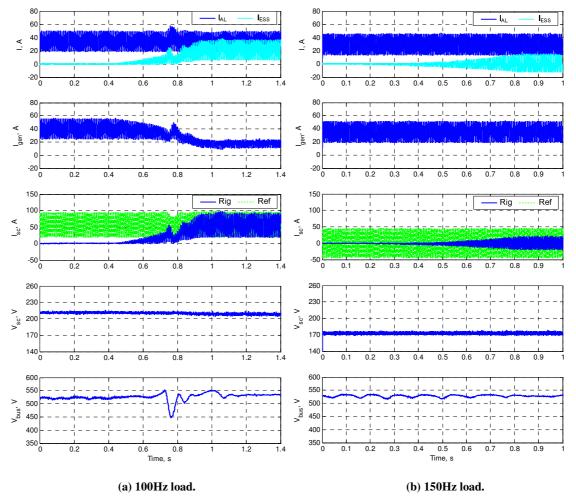

| FIGURE 4.26. OVERALL SYSTEM RESPONSE DUE TO HIGH FREQUENCY SINUSOIDAL LOADS.                                      | 134 |

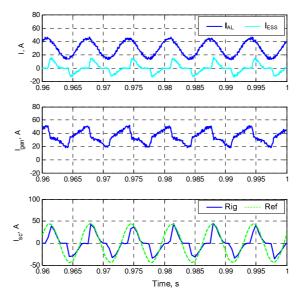

| FIGURE 4.27. MAGNIFIED VIEW OF FIGURE 4.25D FROM 0.9S TO 1S.                                                      | 135 |

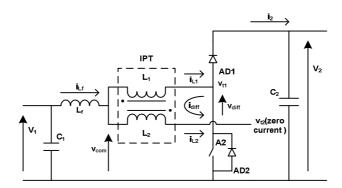

| Figure A.1. Circuit diagram when $V_{T2}$ is floating                             | .158 |

|-----------------------------------------------------------------------------------|------|

| FIGURE A.2. DC-DC CONVERTER CIRCUIT DIAGRAM WITH PEAK CURRENT CONTROLLER IN SABER | .166 |

| FIGURE A.3. DUAL-INTERLEAVED CONVERTER WITH A PEAK CURRENT CONTROLLER.            | .166 |

| FIGURE B.1. DC-DC CONVERTER EQUIVALENT CIRCUITS.                                  | 171 |

|-----------------------------------------------------------------------------------|-----|

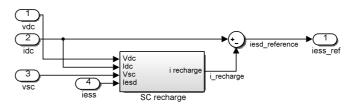

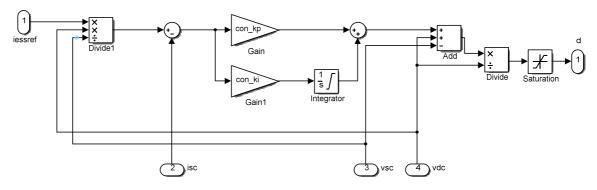

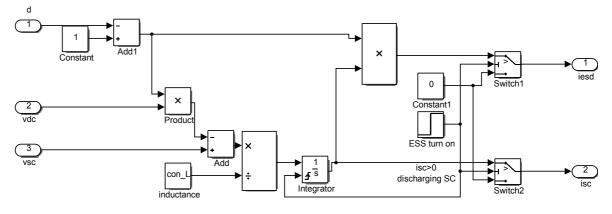

| FIGURE B.2. TOP LEVEL ESS SIMULINK MODEL DIAGRAM.                                 | 172 |

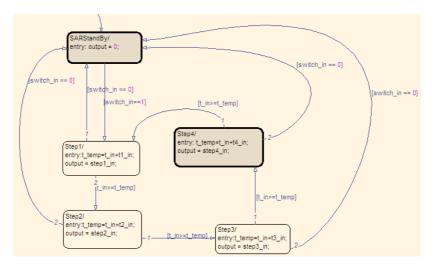

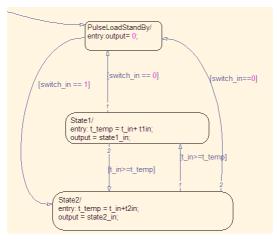

| FIGURE B.3. STATEFLOW DIAGRAM FOR DYNAMIC LOAD PROFILES.                          | 173 |

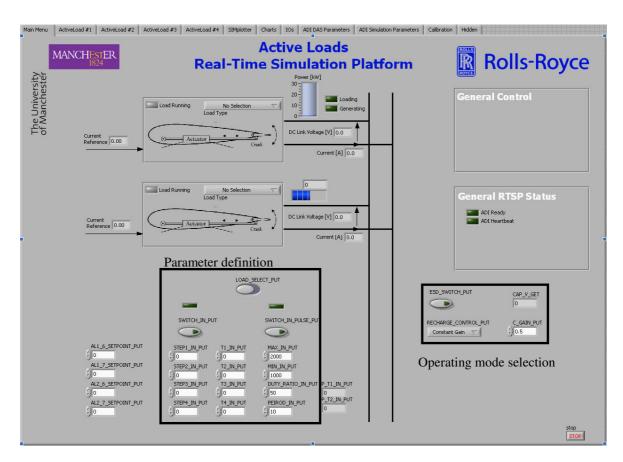

| FIGURE B.4. GUI FOR SETTING LOAD AND ESS CONTROL MODES                            | 174 |

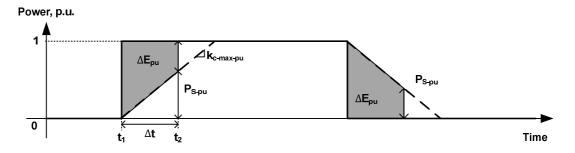

| FIGURE B.5. ESS RESPONSE TO A LOAD STEP STEP FROM ZERO TO 1P.U.                   | 175 |

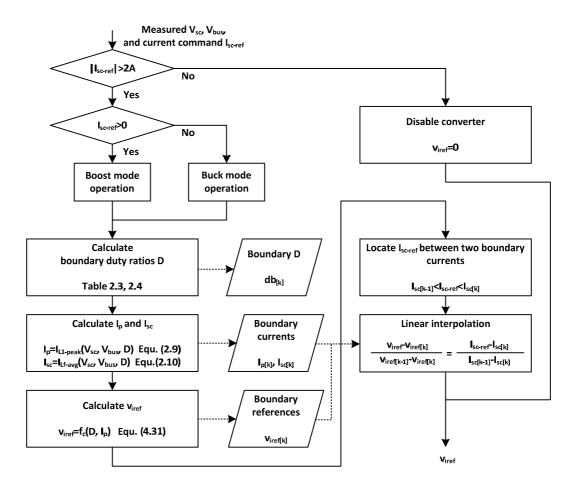

| FIGURE B.6. FLOW CHART OF THE OF CONTROL REFERENCE V <sub>IREF</sub> CALCULATION. | 176 |

## List of abbreviations

| ADI    | Applied Dynamics International                           |

|--------|----------------------------------------------------------|

| AFE    | Active front end                                         |

| AL     | Active load                                              |

| APEC   | Applied Power Electronics Conference and Exposition      |

| CCM    | Continuous conduction mode                               |

| CRM    | Critical conduction mode                                 |

| DC     | Direct current                                           |

| DCM    | Discontinuous conduction mode                            |

| DIC    | Dual-interleaved converter                               |

| DoD    | Depth-of-discharge                                       |

| ESS    | Energy storage system                                    |

| HESS   | Hybrid energy storage system                             |

| HEV    | Hybrid electric vehicle                                  |

| HIL    | Hardware-in-the-loop                                     |

| HMI    | Human machine interface                                  |

| ICE    | Internal combustion engine                               |

| IEPNEF | Intelligent Electrical Power Network Evaluation Facility |

| IGBT   | Insulated-gate bipolar transistor                        |

| IPT    | Interphase transformer                                   |

| IM     | Induction motor                                          |

| MEA    | More-electric aircraft                                   |

| ODE    | Ordinary differential equation                           |

| PI     | Proportional integral (controller)                       |

| PMG    | Permanent magnet generator                               |

| PWM    | Pulse width modulation                                   |

| RTP    | Real-time platform                                       |

| SMES   | Super-conducting magnetic energy storage                 |

| SoC    | State-of-charge                                          |

| SRSG   | Switched-reluctance starter/generator                    |

| TESS   | Thermal energy storage system                            |

| UPS    | Uninterruptible power supply                             |

| UTC    | University technology centre                             |

| ZCS    | Zero current switching                                   |

| ZVS    | Zero voltage swtiching                                   |

|        |                                                          |

## List of symbols

| Ax                  | Switches in the dual interleaved converter (x can be 1 or 2)                   |

|---------------------|--------------------------------------------------------------------------------|

| ADx                 | Anti-parallel diodes in the dual-interleaved converter (x can be 1 or 2)       |

| Bx                  | Switches in the dual interleaved converter (x can be 1 or 2)                   |

| BDx                 | Anti-parallel diodes in the dual-interleaved converter (x can be 1 or 2)       |

| $C_1$               | Low voltage side filter capacitor                                              |

| $C_2$               | High voltage side filter capacitor                                             |

| C <sub>bus</sub>    | Bus filter capacitor                                                           |

| C <sub>para</sub>   | Parasitic capacitance                                                          |

| C <sub>sc</sub>     | Super-capacitor capacitance                                                    |

| D                   | Duty ratio                                                                     |

| E                   | ESS energy                                                                     |

| E <sub>base</sub>   | Energy base                                                                    |

| $E_x$               | ESS energy using control profiles L, C and H (x can be L, C or H)              |

| E <sub>max</sub>    | Maximum energy operating range                                                 |

| $E_{min}$           | Minimum energy operating range                                                 |

| E <sub>sc</sub>     | Energy stored in super-capacitor                                               |

| Et                  | Target energy                                                                  |

| E <sub>t</sub> '    | Normalized target energy, using a base of $E_{max}$ - $E_{min}$                |

| $I_1$               | Low voltage side current of the DIC converter                                  |

| $I_2$               | High voltage side current of the DIC converter                                 |

| $I_{AL}$            | Active load current                                                            |

| I <sub>base</sub>   | Base current                                                                   |

| I <sub>bus</sub>    | Bus current flowing into the bus filter capacitor $C_{\mbox{\scriptsize bus}}$ |

| Ic                  | Internal super-capacitor current                                               |

| I <sub>ESS</sub>    | Energy storage system current                                                  |

| Igen                | Generator current                                                              |

| $I_{L}$             | Load current                                                                   |

| $I_{Lf-avg}$        | Average filter inductor current                                                |

| Ip                  | Peak current seen by the peak current controller                               |

| $I_{PMG}$           | Permanent magnetic generator current                                           |

| I <sub>RL</sub>     | Resistive load current                                                         |

| Is                  | Power source current                                                           |

| $I_{sc}$            | Super-capacitor current                                                        |

| I <sub>sc-L</sub>   | Load current reference component                                               |

| I <sub>sc-re</sub>  | Recharge power current reference component                                     |

| I <sub>sc-ref</sub> | Super-capacitor current reference                                              |

|                     |                                                                                |

| I <sub>L1-peak</sub>       | Peak of phase current i <sub>L1</sub>                                           |

|----------------------------|---------------------------------------------------------------------------------|

| L                          | Inductance of the single leg DC-DC converter                                    |

| L <sub>x</sub>             | Self-inductance of the IPT windings ( x can be 1 or 2)                          |

| $L_{\text{diff}}$          | Differential inductance                                                         |

| L <sub>eq</sub>            | Equivalent inductance in parasitic ringing analysis                             |

| $L_{\rm f}$                | Filter inductor                                                                 |

| L <sub>M</sub>             | Mutual inductance                                                               |

| L <sub>r</sub>             | Inductance ratio of $L_{diff}/L_{f}$                                            |

| Μ                          | Voltage ratio of $V_1/V_2$                                                      |

| $M_{c}$                    | Slope compensation rate in the peak current controller                          |

| N <sub>s</sub>             | Number of super-capacitor modules                                               |

| P <sub>ESS</sub>           | Output power of the ESS                                                         |

| $\mathbf{P_{ESS}}^{*}$     | Power reference of the ESS                                                      |

| $P_{ESS-L}$                | Load component of the energy storage system power reference                     |

| P <sub>ESS-re</sub>        | Recharge component of the energy storage system power reference                 |

| $P_{\text{ESS-ref}}$       | Energy storage system power reference                                           |

| P <sub>gen</sub>           | Generator output power                                                          |

| $P_L$                      | Load power                                                                      |

| $P_{Lx}$                   | Load powers (x can be 1 or 2)                                                   |

| $P_{L-base}$               | Load base                                                                       |

| P <sub>L-max</sub>         | Maximum load power                                                              |

| $P_{L-pu}$                 | Load power in per unit                                                          |

| $\mathbf{P}_{\mathrm{Lt}}$ | Intermediate load power level                                                   |

| $\mathbf{P}_{\mathrm{m}}$  | Phase margin                                                                    |

| Ps                         | Power source output power                                                       |

| P <sub>Sx</sub>            | Power source step response profiles (x can be 1, 2 or 3)                        |

| P <sub>sc-L</sub>          | Load component of the super-capacitor power reference                           |

| P <sub>sc-re</sub>         | Recharge component of the super-capacitor power reference                       |

| P <sub>sc-ref</sub>        | Super-capacitor power reference                                                 |

| P <sub>S-x</sub>           | Power source output power using control profile L, C and H (x can be L, C or H) |

| R                          | Resistive load                                                                  |

| R <sub>cs</sub>            | Current conversion ratio of the current sensor                                  |

| R <sub>p</sub>             | Leakage resistance of the super-capacitor                                       |

| R <sub>s</sub>             | Series resistance of the super-capacitor                                        |

| $S_1$                      | Upper switch in a half-bridge circuit                                           |

| $S_2$                      | Bottom switch in a half-bridge circuit                                          |

| Т                          | Switching period                                                                |

| T <sub>base</sub>          | Time base                                                                       |

| $\mathbf{V}_1$              | Low voltage side voltage of the DIC converter; input voltage in boost mode,      |  |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------|--|--|--|--|

|                             | output voltage in buck mode                                                      |  |  |  |  |

| $V_2$                       | High voltage side voltage of the DIC converter; output voltage in boost mode,    |  |  |  |  |

|                             | input voltage in buck mode                                                       |  |  |  |  |

| $\mathbf{V}_{\mathrm{bus}}$ | DC bus voltage                                                                   |  |  |  |  |

| V <sub>c</sub>              | Voltage on the super-capacitor                                                   |  |  |  |  |

| $V_L$                       | Averaged inductor voltage                                                        |  |  |  |  |

| $V_L^*$                     | Reference signal from the PI controller                                          |  |  |  |  |

| V <sub>sc</sub>             | Super-capacitor terminal voltage                                                 |  |  |  |  |

| V <sub>sc-max</sub>         | Maximum operating voltage of super-capacitor                                     |  |  |  |  |

| V <sub>sc-min</sub>         | Minimum operating voltage of super-capacitor                                     |  |  |  |  |

| V <sub>sc-t</sub>           | Target super-capacitor voltage                                                   |  |  |  |  |

| a                           | Coefficient of a polynomial of degree 2                                          |  |  |  |  |

| b                           | Coefficient of a polynomial of degree 2                                          |  |  |  |  |

| с                           | Coefficient of a polynomial of degree 2                                          |  |  |  |  |

| db <sub>1</sub>             | Boundary duty ratios                                                             |  |  |  |  |

| $f_c()$                     | Peak current controller characteristic function                                  |  |  |  |  |

| $\mathbf{f}_{osc}$          | Oscillation frequency of the parasitic elements in the converter                 |  |  |  |  |

| f <sub>p</sub> ()           | DIC converter characteristic function                                            |  |  |  |  |

| f <sub>ref</sub> ()         | The characteristic function of the DIC converter with a peak current controller  |  |  |  |  |

| f <sub>sc</sub> ()          | DIC converter characteristic function                                            |  |  |  |  |

| f <sub>ss</sub> ()          | Steady-state function of target energy $E_t$ versus load power $P_L$             |  |  |  |  |

| $\mathbf{i}_2$              | High voltage side current                                                        |  |  |  |  |

| i <sub>diff</sub>           | Differential current                                                             |  |  |  |  |

| i <sub>L1</sub>             | Phase current in L <sub>1</sub> winding                                          |  |  |  |  |

| $\mathbf{i}_{L1[k]}$        | Phase current $i_{L1}$ at the $k_{th}$ sub-circuit appeared in a switching cycle |  |  |  |  |

| i <sub>L2</sub>             | Phase current in L <sub>2</sub> winding                                          |  |  |  |  |

| $i_{Lf}$                    | Filter inductor current                                                          |  |  |  |  |

| $\mathbf{k}_1$              | Parameter which define the recharge component equation                           |  |  |  |  |

| $\mathbf{k}_2$              | Parameter which define the recharge component equation                           |  |  |  |  |

| k <sub>c</sub>              | Rate-of-change in source power                                                   |  |  |  |  |

| k <sub>c-base</sub>         | Base value of k <sub>c</sub>                                                     |  |  |  |  |

| k <sub>c-max</sub>          | Maximum rate-of-change in source power                                           |  |  |  |  |

| k <sub>c-max-pu</sub>       | k <sub>c-max</sub> in per unit                                                   |  |  |  |  |

| k <sub>c-pu</sub>           | k <sub>c</sub> in per unit                                                       |  |  |  |  |

| $\mathbf{k}_{i}$            | Integral term of the PI controller                                               |  |  |  |  |

| k <sub>p</sub>              | Proportional term of the PI controller                                           |  |  |  |  |

| $\mathbf{k}_{\mathrm{pwm}}$ | Gain of the peak current controller current reference                            |  |  |  |  |

| р                 | The sub-circuit number when peak current appears          |

|-------------------|-----------------------------------------------------------|

| S                 | Laplace operator                                          |

| $v_{Lf}$          | Filter inductor voltage of the DIC converter              |

| $v_{t1}$          | IPT terminal voltage; transistor A2 voltage               |

| v <sub>t2</sub>   | IPT terminal voltage; transistor B2 voltage               |

| V <sub>A1</sub>   | Upper switch A1 voltage                                   |

| V <sub>bias</sub> | Internal bias of the peak current controller              |

| V <sub>com</sub>  | Central tap voltage of the IPT                            |

| V <sub>diff</sub> | Differential voltage on the IPT                           |

| V <sub>gAx</sub>  | Gate drive voltage of switch Ax                           |

| V <sub>gBx</sub>  | Gate drive voltage of switch Bx                           |

| V <sub>iref</sub> | Current reference of the peak current controller          |

| x <sub>1</sub>    | DCM operating region number                               |

| $\Delta t_{[k]}$  | Duration of the $k_{th}$ sub-circuit in a switching cycle |

| ζ                 | Damping ratio of the closed loop transfer function        |

| ω <sub>c</sub>    | Unity gain cross-over frequency                           |

| ω <sub>n</sub>    | Natural frequency of the closed loop transfer function    |

|                   |                                                           |

### Abstract

The increasing use of electrical technologies within on-board (aircraft, road vehicle, train and ship) power systems is resulting in complex and highly dynamic networks in which energy storage devices have an important role to play, for example to resolve the instantaneous mismatch between load demand and power availability or to provide the flexibility to optimise overall performance. In this thesis, a multi-level controller for a super-capacitor based energy storage system (ESS) is designed, simulated, emulated and validated experimentally to show its effectiveness in smoothing load and managing stateof-charge of the energy storage system.

This thesis first investigates the low level control of the dual-interleaved converter, particularly at light load where seven discontinuous conduction modes (DCMs) appear. A thorough analysis of these operating modes is given and validated by simulations and experiments. Based on the analysis, an inverse-model-based feed-forward current controller is implemented, offering a low level converter control interface which serves the high level supervisory controller within the energy storage system.

Two supervisory control methods have been proposed in this thesis, both producing a super-capacitor current reference for the low level controller. The first supervisory control not only manages the energy within the ESS but also shields the primary power source from rapid load transients, which has been examined through an emulated ESS in the Intelligent Electrical Power Network Evaluation Facility (IEPNEF). A more advanced supervisory controller is then proposed which in addition to the benefits of the first control, regulates the rate-of-change in power that is drawn from the primary power source in the system. The proposed second control method is implemented within a real super-capacitor energy storage system in IEPNEF, with both simulation and experimental results successfully demonstrating and validating its operation.

## Declaration

No portion of the work referred to in the thesis has been submitted in support of an application for another degree or qualification of this or any other university of other institute of learning.

Copyright statement

## **Copyright statement**

The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the 'Copyright') and he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made only in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the 'Intellectual Property') and any reproductions of copyright works in the thesis, for example graphs and tables ('Reproductions'), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx?DocID=487), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on Presentation of Theses.

## Dedication

To my wife Linyu Zhou, and my dear parents Mr Minfu Wu and Mrs Mingfang Yu.

## Acknowledgements

I would like to express my gratitude to my supervisor, Professor Andrew J. Forsyth, and my co-supervisor, Dr Rebecca Todd, for their guidance and support during my PhD career, and proof reading the thesis. Thanks to my advisor, Dr Judith Apsley, for her advice and guidance in research.

I acknowledge the sponsorship of the Dorothy Hodgkin Postgraduate Award from Rolls-Royce plc and EPSRC for the financial funding.

I would like to thank Dr Gerardo Calderon-Lopez for his help, experience and discussions in research. Thanks to Dr Frank Bryan and Dr Tom Feehally for their help in the experimental work in this thesis.

To my parents, for their love and support in finance, thanks for bringing me up and offering me the opportunity to study in UK. To my wife, Linyu Zhou, for her company with great moments that I will always treasure.

I would like to thank my friends, Dr Chunjiang Jia, Nan Xiong, Shicong Zhang, Chengwei Gan, Ding Wang, Wenyuan Wang, Shirley and Vincent, for their support and help.

## About the author

In 2005, the author took a joint program operated by the University of Manchester and the North China Electric Power University, where he obtained two bachelor degrees, both in Electrical and Electronic Engineering. After graduation in 2009, he started his PhD in the Power Conversion Group, University of Manchester. He has researched a wide area of power-electronics-related topics, including control of energy storage systems, design and control of isolated and non-isolated DC-DC converters for energy storage systems, and he contributed to the design and development of a microcontroller-based communication system for a cryogenic converter, which forms part of a patent application.

The following papers have been published:

- R. Todd, D. Wu, J. A. dos Santos Girio, M. Poucand, and A. J. Forsyth, "Supercapacitor-based energy management for future aircraft systems," Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), 2010, pp. 1306-1312.

- C. Jia, D. Wu, I. Hawkins, and A. J. Forsyth, "One-wire communication system for cryogenic converter control," Power Electronics, Machines and Drives (PEMD 2012), 6th IET International Conference on, 2012, pp. 1-5.

- A. J. Forsyth, C. Jia, D. Wu, C. H. Tan, S. Dimler, Y. Yang, et al., "Cryogenic converter for superconducting coil control," IET Power Electronics, vol. 5, pp. 739-746, 2012.

The work in Chapter 4 has been submitted to the PEMD conference (2014) and is under consideration by Rolls-Royce for a patent application.

## Chapter 1 Introduction and literature review

### 1.1 Introduction

As part of its strategy to meet the G8 objective of reducing global  $CO_2$  emissions in 2050 by 50% compared with 2008 levels [1], the government has set targets to limit the  $CO_2$ emissions of the aviation industry to the 2005 level (37.5 million tonnes) by 2050 [2]. However, the recent rapid rise in air travel of 130% in the last 20 years is predicted to increase by a further 60% by 2050. To meet this challenge the aviation industry is pursuing a wide range of new engine, airplane and systems technologies, one of them being the more-electric aircraft (MEA) concept.

### 1.1.1 More-electric Aircraft

In the more-electric aircraft, traditional mechanical, hydraulic and pneumatic systems which tend to be heavy, bulky and inefficient are replaced by electric motor drives and power electronic converters, which are expected to be lighter, smaller and more efficient [3]. Furthermore, replacing multiple types of power distribution systems with a single electrical system is likely to bring further reductions in weight and complexity. The perceived merits of the MEA are summarised in [3], including improvements in aircraft-empty weight, fuel consumption, installation and maintenance costs, turn-around times and system reliability.

However, the introduction of many electrical drives and converters (for example those for fuel pumps, environmental control compressors, actuators and avionic systems) not only increases the required capacity of the electrical system, but also creates challenges of managing the energy flows, power quality and network stability. This is due to the high peak powers that may be drawn by some loads, the rapid load transients that may occur, and the fact that many motor drives and power electronic converters have constant power characteristics due to their internal control functions, which result in a negative incremental input impedance characteristic [4, 5]. In such conditions, exisiting power distribution networks especially those with weak power sources may encounter sub-optimal operation or even malfunction, demonstrating an inability to acceptably deal with voltage transients and faults. One approach to help solving the afore-mentioned problems

of energy management, power quality and stability is the use of energy storage systems (ESSs) which are under active consideration and development.

### 1.1.2 Energy storage system (ESS)

By absorbing and releasing electrical energy at different times with little energy loss, energy storage systems provide a mechanism to reconcile the instantaneous mismatch between load demands and source capacity/availability. This can enable reductions in the peak power rating of sources, leading to potential weight and cost savings, and the capture of energy that would otherwise be lost, for example in regenerative braking systems, often leading to overall energy savings. Metro vehicles in [6] using energy storage systems achieved a 30% saving in energy and a 50% reduction in peak power demand. Furthermore, the possibility of continued operation through a power supply interruption was also mentioned. In grid applications [7], an energy storage system may be used to improve the fault ride through capability of wind generators.

Research in the area of energy storage systems includes improving the characteristics of storage devices (efficiency, lifetime, power density and energy density), improved methods of control to optimise the utilisation of storage devices, optimum combinations of devices to meet application requirements (power density and energy density), and new applications.

As this project concerns an energy storage system that is going to be installed in the Intelligent Electrical Power Network Evaluation Facility (IEPNEF), at the University of Manchester. An overview of the facility is provided in the following section.

#### **1.1.3 IEPNEF**

The Intelligent Electrical Power Network Evaluation Facility (IEPNEF) located in the Rolls-Royce University Technology Centre (UTC) at Manchester is a 100kW state-of-art facility that emulates the electrical system of a more-electric aircraft. The facility has been established for devising and developing more electric technologies as part of a national project for future aircraft and land-based vehicles [8-12].

As shown in Figure 1.1, the two variable speed induction motor (IM) drives emulate the high speed spool and low speed spool of a gas engine, working as the major power source

of the electrical system. The high speed and low speed spools are connected through two shafts to a 30kW, switched reluctance, starter/generator (SRSG) and a 70kW, five phase, permanent magnet generator (PMG) respectively. Taking electrical power from both engine shafts is an area of active investigation as part of the more-electric aircraft concept due to the increased operational flexibility that it provides [13].

Figure 1.1. IEPNEF system diagram.

The electrical power produced by the two generators is distributed through a high-voltage 540V DC bus structure (power distribution network) to a number of electric loads, which include four bi-directional active loads and two resistive load banks. The whole distribution network is in a ring topology with contactors for fault management and network re-configuration.

The bi-directional active loads on the bus are power electronic based load emulators which replicate the behaviour of real aircraft loads such as actuators, fuel pumps, avionics and environmental control systems. Each active load consists of a 700V DC output active front end (AFE) and a DC-DC converter, Figure 1.2. The active front end (AFE) enables bidirectional power flow, having the ability to transfer power back to the grid. The 700V then feeds a 30kW bi-directional DC-DC converter which converts the voltage to 540V and connects to the power distribution network. The control of both the AFE and DC-DC converter is managed by programmable logic controllers (PLC) though communication using Control Techniques' CTNet [14]. Overall control is provided by a real-time platform (RTP), manufactured by Applied Dynamics International [15].

A piece of pre-downloaded program is executed within the real-time platform to control the active loads, for example, to emulate an electric actuator. The real-time platform communicates repeatedly with its host computer (not drawn) located in the control room via Ethernet, allowing remote control and monitoring of the active loads. The programming of the real-time simulation platform is undertaken in Simulink.

Figure 1.2. Diagram of active load system [8].

Two resistive load banks are available as general background loads, Figure 1.1, each contains four individual resistors of  $120\Omega$ ,  $60\Omega$ ,  $30\Omega$  and  $30\Omega$ . The combination of different resistors can provide load steps of approximately 2.5kW, reaching a maximum of 26.7kW with a 540V bus voltage.

A super-capacitor based energy storage system was added to IEPNEF during the course of this PhD project, and the research described in this thesis has supported that development. However, initially, one of the active load systems was used to emulate the operation of the energy storage system. By doing this, the control algorithm and the benefits of the energy storage system were examined.

### 1.1.4 Objectives

The overall objectives of this PhD project were to investigate the converter interfacing, operation and control of a super-capacitor based energy storage system for use within an on-board DC electrical system such as the IEPNEF lab. The dynamic electrical loads and

the varying voltages on the storage devices require the ESS converter to operate correctly across the various operating conditions. Therefore, the fundamental behaviour of the converter needs to be fully understood as it is essential to successfully implement current or voltage controllers. The supervisory level energy management strategies are also an important part of the ESS control, to improve system level performance including energy management, system stability, power capability and load smoothing. In this thesis, the target has been set to operate the converter over a wide operating range while maximally utilising the limited ESS energy, and achieving the conflicting requirement of reducing the impact of load changes on the power sources.

#### **1.2** Literature review

A wide range of papers has been published on energy storage systems, the most common application being for hybrid electric vehicles (HEV) [16-21] where the efficiency, output power or the lifetime of the on-board electrical devices (such as batteries) are of most concern. Applications for trains, trams [6, 22-25] and the MEA [26] can also be found. Other papers describe using an ESS as an auxiliary device to improve the stability and power quality of a power grid or micro grid [7, 21, 27-29], and even an application has been reported using a super-capacitor based ESS for elevators [30].

In the following sections, the main components of an ESS are reviewed first, including: the available energy storage sources, energy management strategies, and DC-DC converters and their control. Secondly, a review of simulation methods including hardware-in-the-loop (HIL) simulation is presented.

#### **1.2.1 Energy storage categories**

Through history, much effort has been spent on finding new energy sources. From using firewood for keeping warm in ancient times to using nuclear reactions for power generation today, a large variety of energy sources is available for use. However, not all are regenerative or suitable for storage. For example, oil is not regenerative, whilst some other sources like solar power or wind are regenerative but not suitable for direct storage. The power from the sun or kinetic power from the wind has to be converted into other forms for easier storage. The range of energy storage forms can be categorized into five

types: mechanical, thermal, electrical, magnetic and chemical energy (in electro-chemical and thermal-chemical forms) [31], which will be described in this section.

### 1.2.1.1 Mechanical energy

The kinetic energy of a moving or rotating mass is one form of stored mechanical energy, the flywheel being the most obvious example. The amount of stored energy in a flywheel is proportional to the square of the rotational speed, which is limited by the tensile strength of the material used and the bearing [32]. With the recent advances in super-strong and ultra-light composite materials, and frictionless, high-performance magnetic bearings [31], the flywheel has now become a strong candidate for energy storage systems, featuring high efficiency, high power density, no emissions and a virtually infinite number of charge and discharge cycles [33, 34]. In addition, it is relative easy to monitor the state-of-charge of a flywheel simply by measuring its speed. In [34], a 10MJ flywheel energy storage system is designed with a peak power of 10kW to improve grid power quality; and the work in [35] addresses voltage sag problems in a grid using flywheel energy storage system.

Another form of stored mechanical energy is potential energy. Pumped hydro and compressed air are typical examples of potential energy, which are usually used for grid applications due to their high energy capacity and high output power [36, 37]. These types of storage are important for the economical operation of the grid, for example, to release energy stored during the low demand period at times of peak demand, i.e., load levelling. However pumped hydro power plants consume 1.3kWh to 1.4kWh in pumping for every kWh generated from storage [37] due to the losses associated with evaporation and friction.

### 1.2.1.2 Thermal energy

Thermal energy can be stored as 'sensible heat', 'latent heat' or as the heat of a chemical reaction (thermo-chemical) [31]. Sensible heat involves storing energy in the high heat capacity of a storage medium, water, or molten salt, by raising its temperature; whereas latent heat involves using the energy required to make a phase change from solid to liquid and vapour as a storage mechanism; the third form is the heat in reversible chemical reactions, including decomposition of metal hydrides, oxides, etc. [31]. Thermal energy storage systems (TESS) are usually found in cooling or heating systems for buildings and

solar thermal power plants [38]. Due to the need for large storage tanks, thermal storage systems are generally not suitable for the transport industry.

### 1.2.1.3 Magnetic energy

Magnetic energy is stored in the magnetic field produced by a large current. The superconducting magnetic energy storage (SMES) system operates on this principle, utilizing a superconducting inductor to virtually eliminate conduction loss. The advantages of SMES systems are the high efficiency above 90% [39], the quick, high-power response [40], and applicability in cryogenic climates (-54°C) where other power sources like batteries cease to function [41]. The disadvantages of SMES systems are the high cost [42, 43], the additional cryogenic refrigeration system required to keep the coil in a superconductor. Due to its extremely high power rating [32], but large size and weight, SMES systems are usually found in power quality applications for the utility grid. For example SMES systems are being evaluated [44, 45] for smoothing output power from wind farms. In [41], the author proposes a small scale SMES for aircraft, however, it has a capacity of 5kWh and weighs 500kg.

### 1.2.1.4 Electrical energy (including electrochemical energy)

Hydrogen storage systems (fuel-cells), batteries and super-capacitors are widely used technologies for electrical energy storage. Quite a number of applications can be found especially in the transport sector utilizing individual units or the combination of different types of devices in order to combine their best features in cost, energy/power density, response time, and efficiency [32]. Fuel-cells and batteries utilise electrochemical conversions to store energy which tends to result in a device with a high energy density [33]. However, degradation occurs in batteries over a number of repetitive charge and discharge cycles, especially at extreme rates and with over-charging/discharging, which tends to reduce capacity and lifetime [46]. Super-capacitors, on the other hand, store energy by simple charge separation without chemical reaction and tend to have high peak power capability and a long lifetime but low energy density [33, 47].

#### Fuel-cell

The fuel-cell combines oxygen with a hydrogen fuel and converts them electrochemically into water, heat, and the production of electricity [48]. The absence of any greenhouse gas emissions makes fuel-cells an attractive energy source for many applications including road vehicles [49]. Regenerative fuel-cell are devices that combine the function of electricity production and hydrogen production for energy storage [33].

Some key features of fuel-cells include:

- a low and poorly regulated output voltage which requires series connections to increase the output voltage and/or power electronic control to stabilise the voltage [50];

- 2. clean operation with low emissions [42] and a high energy density (typically 200Wh/l 300Wh/l), which is much greater than that of batteries [50];

- 3. the temperature, gas flows, pressure, and humidity of the cell have a strong influence on the behaviour and performance [42, 51];

- 4. high efficiency is possible (40%-70%) [48], but is affected by the temperature and pressure conditions, and so it is important to control these conditions for maximum efficiency [52];

- 5. slow response due to limits of the mechanical devices required for maintaining the temperature, pressure and humidity. Therefore, during rapid electrical load transients, the fuel-cell may suffer partial over temperature or over-air pressure conditions which shorten the lifetime of the fuel-cell [53];

- 6. the main challenges for fuel-cell technology include the high price, the durability of the system and the fuel storage mechanism [54].

#### Batteries

Among the various kinds of rechargeable batteries, lead-acid batteries are still the most widely used, which first appeared in the mid 1800's [33]. Their advantages are the low price and high energy density [31]. Nickel cadmium (NiCd) batteries became widely used between 1970 and 1990, but have recently been replaced by lithium-ion and nickel metal hydride (NiMH) batteries which offer the advantages of longer life cycle, less pronounced 'memory effect' and higher energy density [33]. Some other types of rechargeable batteries are summarised in Table 1.1 together with the afore-mentioned batteries.

| Technology              | Capacity<br>(Ah) | Cycle life<br>(Cycles) | Energy density<br>(Wh/kg) | Power density<br>(W/kg) | Cell voltage<br>(V) |

|-------------------------|------------------|------------------------|---------------------------|-------------------------|---------------------|

| Nickel-Cadmium          | 100-180          | 2000                   | 50-60                     | 200                     | 1.35                |

| Iron-Air                | -                | 200                    | 80                        | 30-40                   | -                   |

| Iron-Nickel Oxide       | 200-600          | 920                    | 50-250                    | 100                     | -                   |

| Lead-Acid               | 100-1500         | 1000-1500              | 20-50                     | 80-300                  | 2.1                 |

| Nickel-Metal<br>Hydride | 100-250          | 1000                   | 50-60                     | 200-250                 | 1.25                |

| Lithium                 | 100              | 1200                   | 40-150                    | 100-400                 | 3.6                 |

| Sodium-Sulphur          | 230-300          | 600-800                | 80-120                    | 90-200                  | 2.08                |

| ZEBRA                   | -                | >1200                  | 80-100                    | 150-200                 | 2.58                |

| Zinc-air                | -                | -                      | 200                       | 100                     | -                   |

| Zinc-Bromine            | 120              | 350-500                | 70-90                     | 80-100                  | 1.79                |

| Zinc-Nickel oxide       | 300              | -                      | 70                        | 200                     | -                   |

The main application areas for battery storage reported in the literature include portable equipment, vehicles, industrial applications, uninterruptible power supplies (UPSs) and load levelling for grid systems [25, 29, 31, 33, 55]. Lithium-ion batteries and Ni-MH batteries tend to be preferred in portable applications [31]. Hybrid electric vehicles (HEVs), such as the Toyota Prius and the Honda Accord, use sealed Ni-MH batteries [56, 57]; some new battery technologies, like the ZEBRA battery, are also used for HEVs [58, 59]. For grid applications, large battery storage using lead-acid batteries existed early in the 1930s and had 186MWh capacity [32]. However more recently lithium-ion cells are being used, for example, by Siemens [60].

One of the problems of batteries is the aging process. The longevity of batteries is significantly affected by the depth-of-discharge (DoD) [61], extreme temperatures, over-charging or over-discharging, and the rate of charge or discharge [46, 62, 63]. Some of the other disadvantages of batteries include the toxic materials used in manufacturing [31] and the safety issues such as gas release during over-charging, and protection against thermal runaway [46, 64].

#### Super-capacitors

Super-capacitors, also known as ultra-capacitors or electric double-layer capacitors, store electrical energy in the electric field between two electrodes [32]. Compared to conventional capacitors with mF or  $\mu$ F capacitance, super-capacitors are designed to have a large electrode surface area and use high permittivity dielectric, therefore attaining very high capacitance ratings (up to kF).

The key features of super-capacitors are:

- low output voltage (2.7V per cell); therefore series connection of cells with balancing is necessary [32];

- 2. high power density (2kW/kg) [32, 48], but low energy density [54];

- 3. nearly unlimited charge/discharge cycles and a long life time of ten years [32, 43];

- 4. high in-out efficiency, above 95% [32, 48], but the self-discharge rate is also high (5% per day) compared with batteries [32];

- 5. state-of-charge (SoC) is simple to monitor by measuring the voltage [32];

- 6. easy installation, compact size [32] and adaptability in adverse environments (hot, cold, and moist) [43].

However, among the merits of the super-capacitors, the most dominant feature is their high power characteristic which has resulted in them finding applications in many fields. Iwanski [28] reports the use of super-capacitors for smoothing wind turbine output power in a micro-grid. The authors of [22, 24, 65] use super-capacitors for on-board and substation energy storage for metro trains. Curti [16] improves the dynamic performance of a battery bank using super-capacitors in an HEV. Zhang uses super-capacitors to improve the power quality of an aircraft electrical system in [66, 67].

A typical operating regime for a super-capacitor bank is to allow the voltage to vary over a 2:1 range, which enables 75% of the maximum stored energy to be used within a system application [48]. A greater depth-of-discharge is normally avoided since it results in very high capacitor currents for a given power level and places extreme demands on the interfacing DC-DC converter [52, 68].

#### Hybrid energy storage systems (HESS)

As a summary, the features of different energy storage technologies are compared in terms of their energy capacity and power capability as shown in Figure 1.3.

Figure 1.3. Power against energy plot for various energy storage technologies [32].

Due to their different characteristics, multiple energy sources are sometimes combined. These combinations come in many variations, but all share a common trend of combining fast, high power devices and slow, high energy devices [54]. For example, the slow responding fuel-cell is often equipped with auxiliary storage devices to improve its dynamic performance, lifetime and operational safety [21, 69]. Thounthong improved the dynamics of a fuel-cell first by utilizing a battery bank as a secondary source in [21], and later added a super-capacitor for further improvement [70]. Another widely used combination is of a battery and super-capacitor for an HEV, in which the super-capacitor is used for improving battery lifetime and fuel-economy [16-19, 27, 61, 71-73]. In addition, other hybrid energy storage systems are reported in the literature:

- 1. battery and super-conducting magnetic coil [74];

- 2. battery and flywheel [75];

- 3. fuel-cell, batteries and super-capacitor [20, 52, 70];

- 4. fuel-cell and super-conducting magnetic coil [45];

- 5. compressed air and super-capacitor [76].

For the energy storage system to be used on the target on-board electrical system in this thesis, super-capacitors are the ideal candidate because of their high power density and high peak power it can provide to improve the stability, power quality of the system.

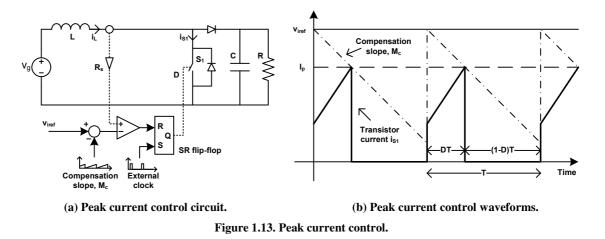

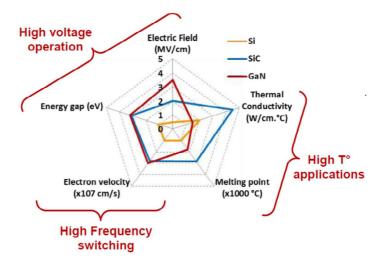

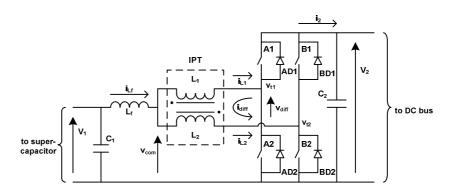

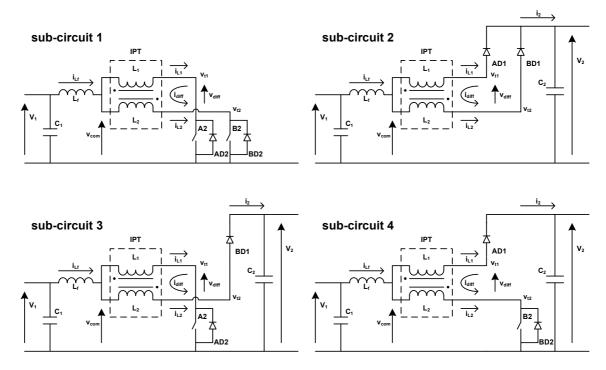

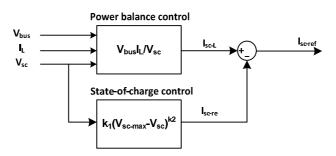

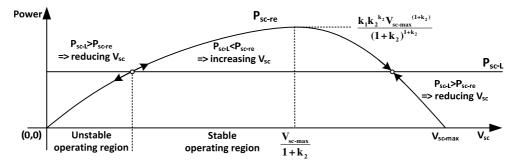

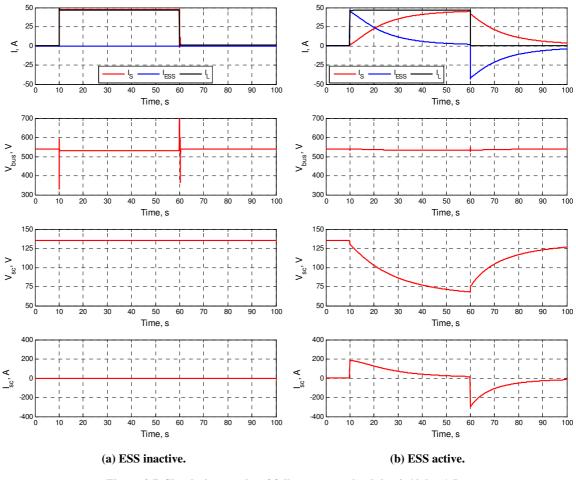

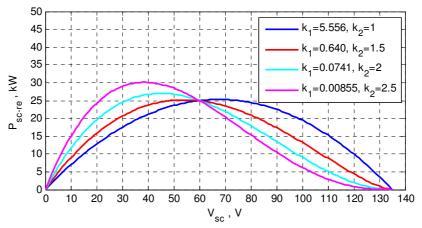

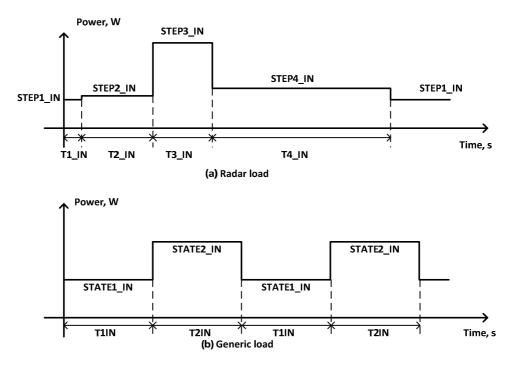

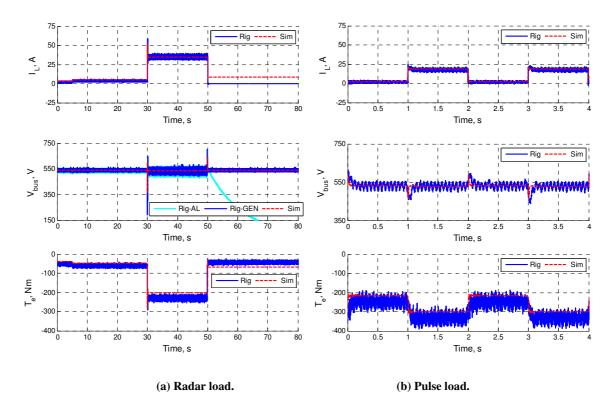

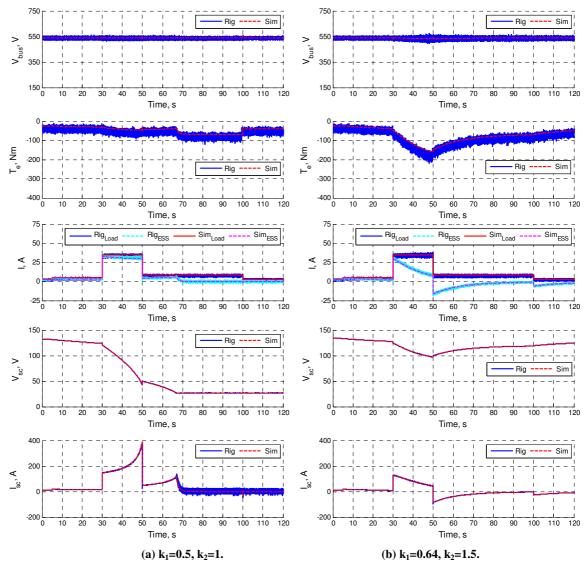

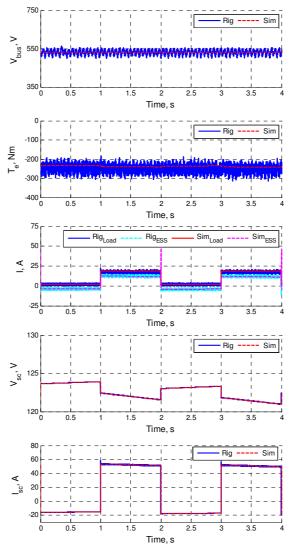

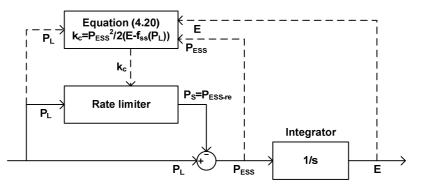

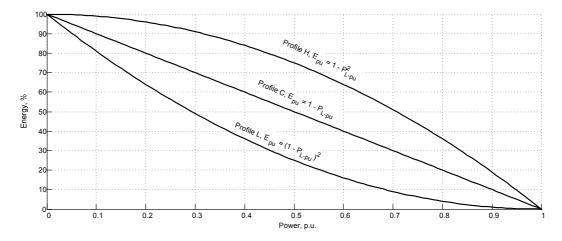

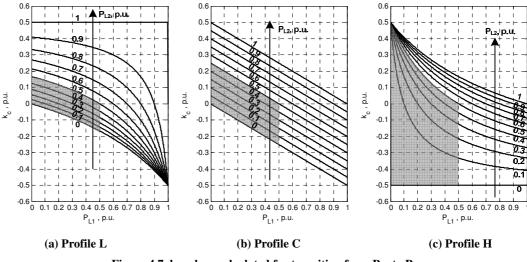

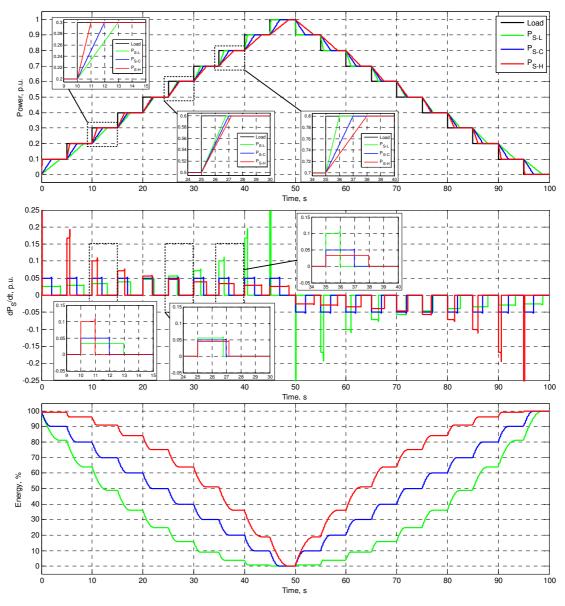

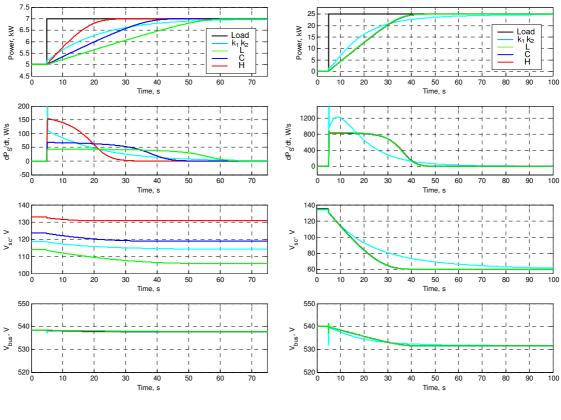

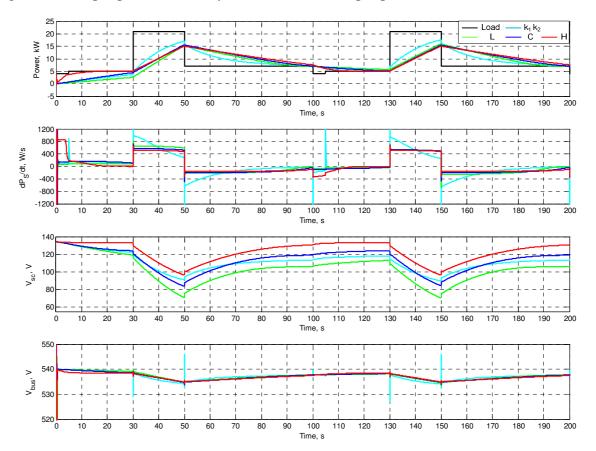

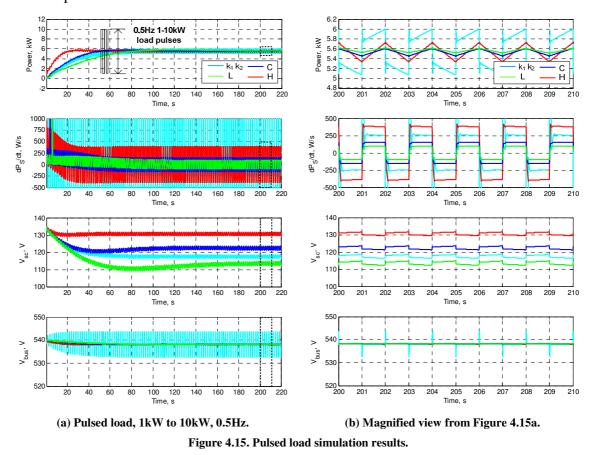

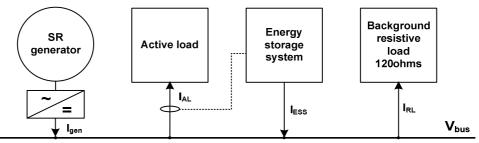

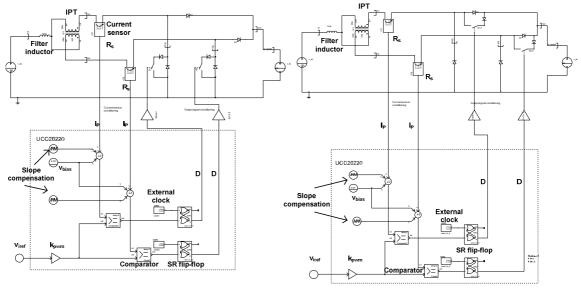

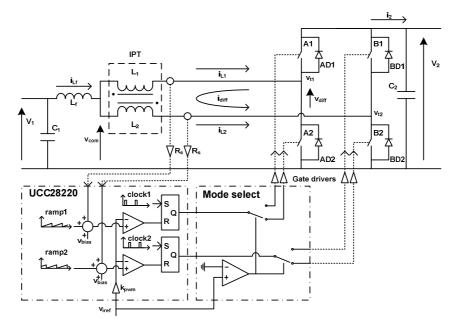

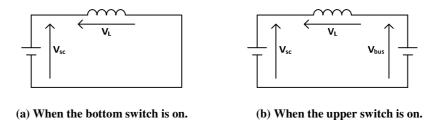

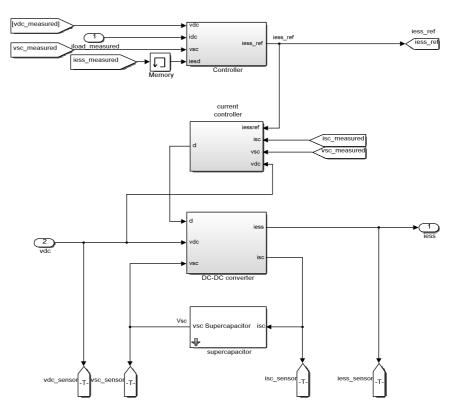

#### 1.2.2 Energy management strategies for the energy storage system