## **Organic Logic Circuits: Fabrication Process and Device Optimisation**

A thesis submitted to The University of Manchester for the degree of Doctor of Philosophy in the Faculty of Engineering and Physical Sciences.

2012

Ming Yu Shi

School of Electrical and Electronic Engineering

### **Table of Contents**

| List | t of F | Figures                                                        | 5   |

|------|--------|----------------------------------------------------------------|-----|

| List | t of T | ۲ables                                                         | 10  |

| Abł  | orevi  | ations and Symbols                                             | .11 |

| Abs  | stract | t                                                              | 15  |

| Dec  | larat  | tion                                                           | 16  |

| Cop  | oyrig  | ht Statement                                                   | 16  |

| Ack  | now    | ledgements                                                     | 17  |

| 1    | Int    | roduction                                                      | 18  |

|      |        | Background                                                     |     |

|      |        | 1.1.1 Organic Semiconductor Materials and Charge Transport     |     |

|      |        | 1.1.2 Organic Field Effect Transistors (OFETs)                 | 23  |

|      | 1.2    | Motivation and Research Aim                                    |     |

|      | 1.3    | Research Challenges                                            | 27  |

|      | 1.4    | Thesis Organisation                                            | 27  |

| 2    | Lite   | erature Review                                                 | 29  |

|      | 2.1    | Introduction                                                   | 29  |

|      | 2.2    | Progress in Organic Logic Circuits                             | 29  |

|      |        | 2.2.1 State of The Art Organic Devices                         | 30  |

|      | 2.3    | Fabrication Process                                            | .35 |

|      |        | 2.3.1 Laboratory Based Processing                              |     |

|      |        | 2.3.2 Printing Based Processing                                | 45  |

|      | 2.4    | Simulation Techniques                                          | 57  |

|      | 2.5    | Discussion and Summary                                         | 59  |

| 3    | De     | sign                                                           | 63  |

|      | 3.1    | Introduction                                                   | .63 |

|      |        | 3.1.1 Using Liquid Crystals to Measure Temperature             |     |

|      |        | 3.1.2 Silicon System Design                                    | 69  |

|      | 3.2    | Analysis of an Organic Sensor Circuit Equivalent               |     |

|      |        | 3.2.1 Revised Research Focus                                   |     |

|      | 3.3    | A Suitable Fabrication Process                                 |     |

|      |        | 3.3.1 Transistor Structure, Processing and Choice of Materials |     |

|      | 3.4    | Logic Circuit Configuration and Geometry                       |     |

|      |        | 3.4.1 Inverters                                                |     |

|      | 2 5    | 3.4.2 Comparator                                               |     |

|      | 3.5    | Photomask Design                                               |     |

|      | 21     | 3.5.1 Design Discussion                                        |     |

|      | 3.0    | Summary                                                        | 91  |

| 4 | Ме                                                                                                   | thodo                                                                                                                                                  | logy                                                                                                                                                                                                                                                                                                                                                                                                                     | 92                                                                                                                                |

|---|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|   | 4.1                                                                                                  | Substr                                                                                                                                                 | ate Preparation and Cleaning                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   |

|   |                                                                                                      |                                                                                                                                                        | Procedure                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   |

|   | 4.2                                                                                                  | Solver                                                                                                                                                 | t Preparation                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                   |

|   |                                                                                                      | 4.2.1                                                                                                                                                  | Procedure for PVP + PMF solution                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

|   |                                                                                                      | 4.2.2                                                                                                                                                  | Procedure for TIPS- pentacene solution:                                                                                                                                                                                                                                                                                                                                                                                  | 93                                                                                                                                |

|   | 4.3                                                                                                  | Single                                                                                                                                                 | Transistor Fabrication                                                                                                                                                                                                                                                                                                                                                                                                   | 94                                                                                                                                |

|   |                                                                                                      |                                                                                                                                                        | Procedure                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   |

|   | 4.4                                                                                                  | Capaci                                                                                                                                                 | itors                                                                                                                                                                                                                                                                                                                                                                                                                    | 95                                                                                                                                |

|   |                                                                                                      | -                                                                                                                                                      | Circuit fabrication                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|   |                                                                                                      | 4.5.1                                                                                                                                                  | Procedure I: Lift-Off Photolithography                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

|   |                                                                                                      | 4.5.2                                                                                                                                                  | Procedure II: Gate Layer Deposition                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|   |                                                                                                      | 4.5.3                                                                                                                                                  | Procedure III: Dielectric Layer Deposition and Patterning                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   |

|   |                                                                                                      | 4.5.4                                                                                                                                                  | Procedure IV: Source Drain Layer Deposition                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |

|   |                                                                                                      | 4.5.5                                                                                                                                                  | Procedure V: Semiconductor Deposition                                                                                                                                                                                                                                                                                                                                                                                    | 99                                                                                                                                |

|   | 4.6                                                                                                  | Device                                                                                                                                                 | e Simulation                                                                                                                                                                                                                                                                                                                                                                                                             | 101                                                                                                                               |

|   |                                                                                                      | 4.6.1                                                                                                                                                  | Parameter Extraction                                                                                                                                                                                                                                                                                                                                                                                                     | 101                                                                                                                               |

|   |                                                                                                      | 4.6.2                                                                                                                                                  | AIM-Spice Simulation                                                                                                                                                                                                                                                                                                                                                                                                     | 101                                                                                                                               |

|   | 4.7                                                                                                  | Device                                                                                                                                                 | e Characterisation and Measurements                                                                                                                                                                                                                                                                                                                                                                                      | 101                                                                                                                               |

|   |                                                                                                      | 4.7.1                                                                                                                                                  | Device Characterisation                                                                                                                                                                                                                                                                                                                                                                                                  | 101                                                                                                                               |

|   |                                                                                                      | 4.7.2                                                                                                                                                  | Surface Profiling                                                                                                                                                                                                                                                                                                                                                                                                        | 102                                                                                                                               |

|   |                                                                                                      | 4.7.3                                                                                                                                                  | Permittivity Measurement                                                                                                                                                                                                                                                                                                                                                                                                 | 103                                                                                                                               |

|   | 4.8                                                                                                  | Calcul                                                                                                                                                 | ation of Transistor Characteristics                                                                                                                                                                                                                                                                                                                                                                                      | 103                                                                                                                               |

|   |                                                                                                      |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                   |

| 5 | Fa                                                                                                   | bricati                                                                                                                                                | ion Results                                                                                                                                                                                                                                                                                                                                                                                                              | 105                                                                                                                               |

| 5 |                                                                                                      |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                   |

| 5 |                                                                                                      |                                                                                                                                                        | i <b>on Results</b><br>s a Polymer Dielectric for Organic Transistors<br>Film Thickness                                                                                                                                                                                                                                                                                                                                  | 105                                                                                                                               |

| 5 |                                                                                                      | PVP a                                                                                                                                                  | s a Polymer Dielectric for Organic Transistors                                                                                                                                                                                                                                                                                                                                                                           | 105<br>105                                                                                                                        |

| 5 |                                                                                                      | PVP a<br>5.1.1                                                                                                                                         | s a Polymer Dielectric for Organic Transistors<br>Film Thickness                                                                                                                                                                                                                                                                                                                                                         | 105<br>105<br>106                                                                                                                 |

| 5 |                                                                                                      | PVP at 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                                                                                                                | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching                                                                                                                                                                                                                                                                        | 105<br>105<br>106<br>107<br>107                                                                                                   |

| 5 |                                                                                                      | PVP at 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                                                                                                                | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant                                                                                                                                                                                                                                                                                                         | 105<br>105<br>106<br>107<br>107                                                                                                   |

| 5 | 5.1                                                                                                  | PVP at 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5                                                                                                       | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching                                                                                                                                                                                                                                                                        | 105<br>105<br>106<br>107<br>107<br>109                                                                                            |

| 5 | 5.1<br>5.2                                                                                           | PVP at<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single                                                                                          | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP                                                                                                                                                                                                                                     | 105<br>105<br>106<br>107<br>107<br>109<br>111                                                                                     |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                                                        | PVP at<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single<br>Simula                                                                                | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP<br>Transistor Results                                                                                                                                                                                                               | 105<br>105<br>106<br>107<br>107<br>109<br>111<br>116                                                                              |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                                                        | PVP at<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single<br>Simula                                                                                | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP<br>Transistor Results                                                                                                                                                                                                               | 105<br>106<br>106<br>107<br>107<br>107<br>109<br>111<br>116<br>122                                                                |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                                                        | PVP at<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single<br>Simula<br>Logic<br>5.4.1                                                              | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP<br>Transistor Results<br>Ation Results<br>Circuit Results                                                                                                                                                                           | 105<br>106<br>106<br>107<br>107<br>109<br>111<br>116<br>122<br>122                                                                |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                                             | PVP at<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single<br>Simula<br>Logic<br>5.4.1<br>5.4.2                                                     | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP<br>Transistor Results<br>Ation Results<br>Circuit Results<br>Inverter Circuit<br>Comparator Circuit                                                                                                                                 | 105<br>105<br>106<br>107<br>107<br>107<br>109<br>111<br>116<br>122<br>125                                                         |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                                             | PVP at<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single<br>Simula<br>Logic<br>5.4.1<br>5.4.2                                                     | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP<br>Transistor Results<br>ation Results<br>Circuit Results<br>Inverter Circuit                                                                                                                                                       | 105<br>106<br>106<br>107<br>107<br>109<br>111<br>116<br>122<br>125<br>127                                                         |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                                             | PVP at<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single<br>Simula<br>Logic<br>5.4.1<br>5.4.2<br>BGBC                                             | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP<br>Transistor Results<br>ation Results<br>Circuit Results<br>Inverter Circuit<br>Comparator Circuit<br>Logic Circuit Fabrication Process                                                                                            | 105<br>106<br>106<br>107<br>107<br>107<br>107<br>109<br>111<br>116<br>122<br>125<br>127                                           |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                                             | PVP at<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single<br>Simula<br>Logic<br>5.4.1<br>5.4.2<br>BGBC<br>5.5.1                                    | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP<br>Transistor Results<br>ation Results<br>Circuit Results<br>Inverter Circuit<br>Comparator Circuit<br>Gate Layer                                                                                                                   | 105<br>106<br>106<br>107<br>107<br>109<br>111<br>116<br>122<br>122<br>125<br>127<br>127<br>127                                    |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                                             | PVP at<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single<br>Simula<br>Logic<br>5.4.1<br>5.4.2<br>BGBC<br>5.5.1<br>5.5.2                           | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP<br>Transistor Results<br>Ation Results<br>Circuit Results<br>Inverter Circuit<br>Comparator Circuit Fabrication Process<br>Gate Layer<br>Dielectric layer                                                                           | 105<br>105<br>106<br>107<br>107<br>109<br>111<br>116<br>122<br>125<br>127<br>127<br>127<br>127<br>128                             |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li><li>5.5</li></ul>                                | PVP at<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single<br>Simula<br>Logic<br>5.4.1<br>5.4.2<br>BGBC<br>5.5.1<br>5.5.2<br>5.5.3<br>5.5.4         | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP<br>Transistor Results<br>ation Results<br>Circuit Results<br>Inverter Circuit<br>Comparator Circuit<br>Comparator Circuit Fabrication Process<br>Gate Layer<br>Dielectric layer<br>Source Drain Layer                               | 105<br>105<br>106<br>107<br>107<br>109<br>111<br>116<br>122<br>127<br>127<br>127<br>127<br>127<br>128<br>130                      |

| 5 | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> </ul>             | PVP at<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single<br>Simula<br>Logic<br>5.4.1<br>5.4.2<br>BGBC<br>5.5.1<br>5.5.2<br>5.5.3<br>5.5.4<br>Summ | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP<br>Transistor Results<br>Ation Results<br>Circuit Results<br>Inverter Circuit<br>Comparator Circuit<br>Comparator Circuit Fabrication Process<br>Gate Layer<br>Dielectric layer<br>Source Drain Layer<br>Semiconductor Layer        | 105<br>105<br>106<br>107<br>107<br>109<br>111<br>116<br>122<br>127<br>127<br>127<br>127<br>127<br>128<br>130<br>132               |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>De</li> </ul> | PVP a<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single<br>Simula<br>Logic<br>5.4.1<br>5.4.2<br>BGBC<br>5.5.1<br>5.5.2<br>5.5.3<br>5.5.4<br>Summ  | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP<br>Transistor Results<br>Ation Results<br>Circuit Results<br>Circuit Results<br>Inverter Circuit<br>Comparator Circuit<br>Comparator Circuit Fabrication Process<br>Gate Layer<br>Dielectric layer<br>Source Drain Layer<br>ary     | 105<br>105<br>106<br>107<br>107<br>109<br>111<br>116<br>122<br>125<br>127<br>127<br>127<br>128<br>130<br>132                      |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>De</li> </ul> | PVP a<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>Single<br>Simula<br>Logic<br>5.4.1<br>5.4.2<br>BGBC<br>5.5.1<br>5.5.2<br>5.5.3<br>5.5.4<br>Summ  | s a Polymer Dielectric for Organic Transistors<br>Film Thickness<br>Dielectric Properties<br>Dielectric Constant<br>Rate of Oxygen Plasma Etching<br>Photolithography Process on PVP<br>Transistor Results<br>ation Results<br>Circuit Results<br>Inverter Circuit<br>Comparator Circuit<br>Comparator Circuit Fabrication Process<br>Gate Layer<br>Dielectric layer<br>Source Drain Layer<br>Semiconductor Layer<br>ary | 105<br>106<br>106<br>107<br>107<br>109<br>111<br>116<br>122<br>125<br>127<br>127<br>127<br>127<br>128<br>130<br>134<br>134<br>134 |

|            |     | 6.1.3     | Characterisation of PVP-BST Thin Films                                                         | 144   |

|------------|-----|-----------|------------------------------------------------------------------------------------------------|-------|

|            |     | 6.1.4     | Single Transistor Results                                                                      |       |

|            |     | 6.1.5     | PVP-BST Nanocomposite for Logic Circuits                                                       | 154   |

|            |     | 6.1.6     | PVP-BST Dielectric Discussion                                                                  | 161   |

|            | 6.2 | Contac    | ct Layer Optimisation                                                                          | 165   |

|            |     | 6.2.1     | Introduction                                                                                   | 165   |

|            |     | 6.2.2     | Experimental                                                                                   |       |

|            |     | 6.2.3     | Results and Discussion                                                                         | 165   |

| 7          | Со  | nclusi    | ion                                                                                            | . 170 |

|            | 7.1 | Future    | Work                                                                                           | 172   |

|            |     | 7.1.1     | PVP-BST Nanocomposite Dielectric                                                               | 172   |

|            |     | 7.1.2     | Optimisation of the BGBC Logic Circuit Fabrication Process                                     | 173   |

|            |     | 7.1.3     | Printed OFETs                                                                                  | 174   |

| 8          | Re  | ferenc    | ces                                                                                            | . 175 |

| Apr        |     |           | Potential Capacitance Measurement Circuits for the Liquid Crysta                               |       |

| <b>F</b> F |     |           | ensor                                                                                          |       |

| App        | end | ix B : P  | Passive Liquid Crystal Temperature Sensor Array                                                | 188   |

| App        | end | ix C : P  | VP + PBTTT Transistor Performance                                                              | 190   |

| App        | end | ix D : P  | VP-BST Raw Material Calculation                                                                | 191   |

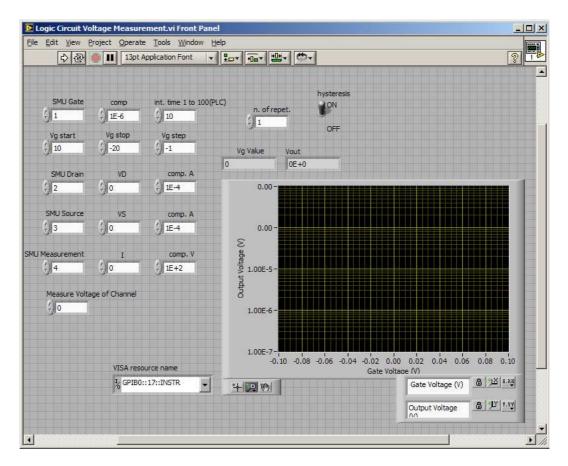

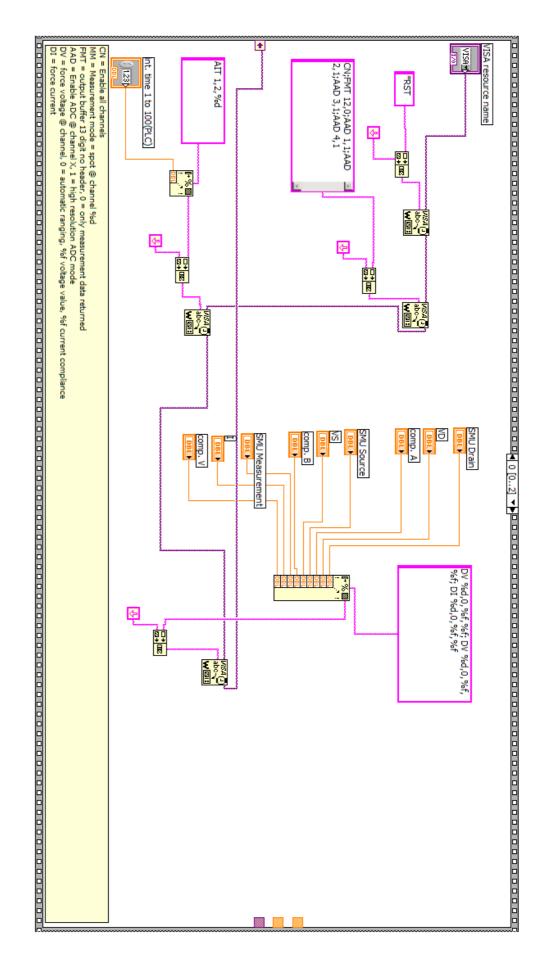

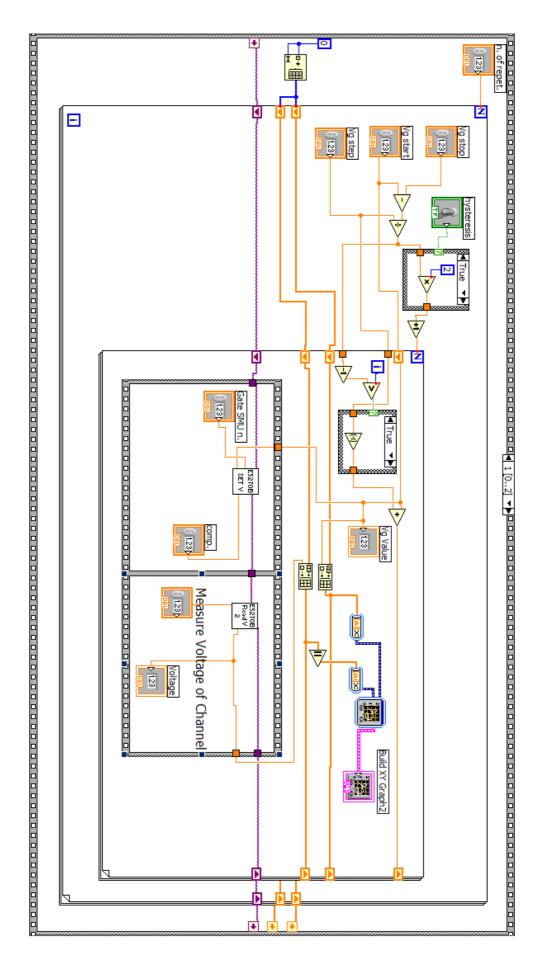

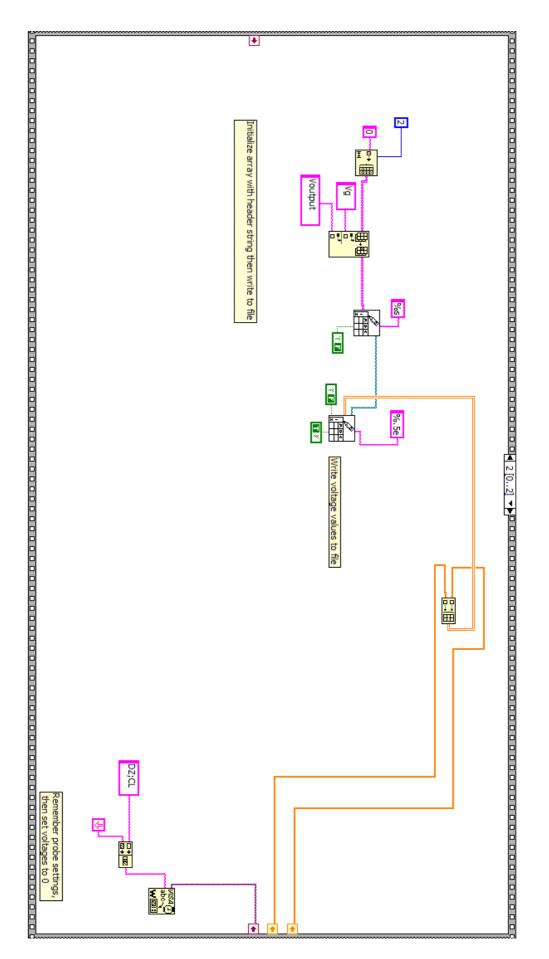

| App        | end | ix E : L  | abVIEW Program for Logic Circuit Characterisation                                              | 193   |

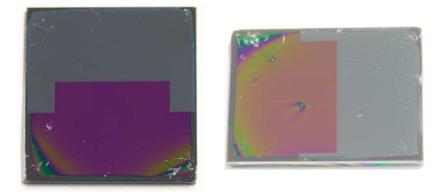

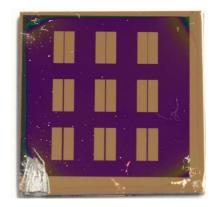

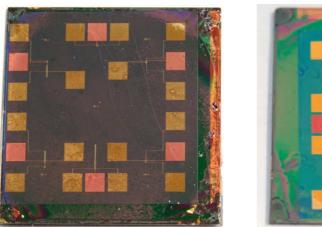

| App        | end | ix F : F  | abricated Devices                                                                              | 197   |

| App        | end | ix G : C  | Cross-linking PVP with HMBG                                                                    | 200   |

| App        | end | ix H : N  | Aaximum Theoretical Gain for The Diode-Load Inverter                                           | 203   |

| App        | end | ix I : Ci | rcuit Designs                                                                                  | 204   |

| App        | end | ix J : A  | IM-Spice Simulation                                                                            | 206   |

| App        | end |           | Calculation of Dielectric Constant Values Using Series, Parallel A ogarithmic Mixing Equations |       |

|            |     |           |                                                                                                |       |

Word count: 50717

#### List of Figures

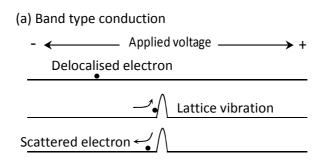

| Figure 1.1: Band transport (a) and hopping transport (b). This figure is adapted from [1] 21                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

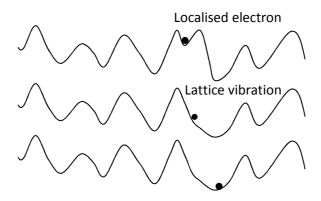

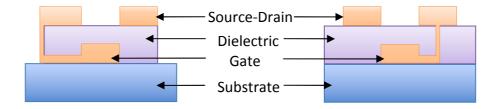

| Figure 1.2: OFET structures. Bottom gate bottom contact – BGBC (a). Bottom gate top<br>contact – BGTC (b). Top gate bottom contact – TGBC (c). Top gate top contact –<br>TGTC (d) |

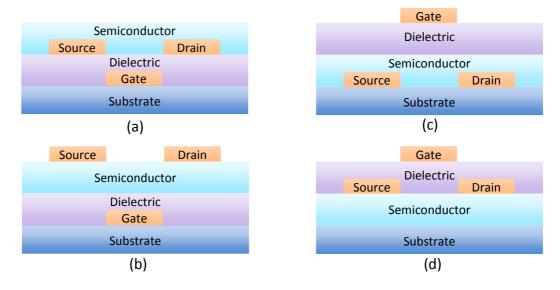

| Figure 1.3: Bottom gate bottom contact OFET with Si gate, SiO <sub>2</sub> dielectric and pentacene semiconductor                                                                 |

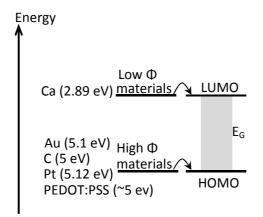

| Figure 1.4: Energy diagram illustrating the injection of charges from matching work function contact materials into HOMO or LUMO levels of an organic semiconductor25             |

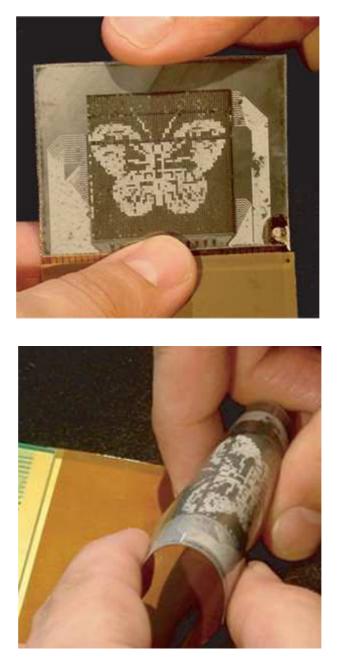

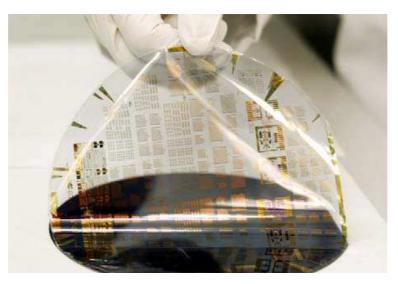

| Figure 2.1: Flexible display using organic transistors. Image by Philips [40]                                                                                                     |

| Figure 2.2: A 6" Readius display. Image by Polymer Vision [53]                                                                                                                    |

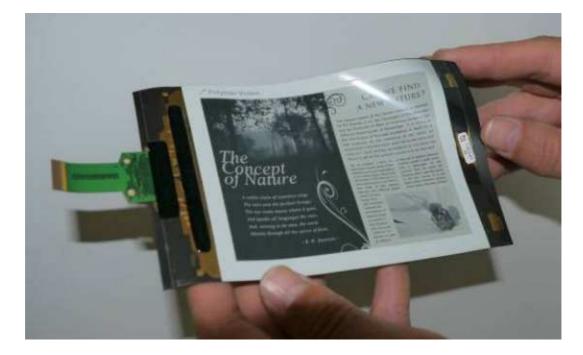

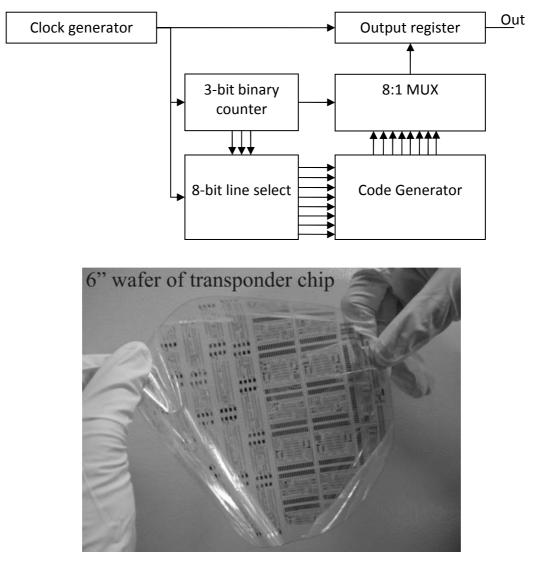

| Figure 2.3: Organic RFID chip fabricated on polyimide substrate. Image by Philips [41]33                                                                                          |

| Figure 2.4: The fastest RFID chip to date using Al <sub>2</sub> O <sub>3</sub> dielectric. Image by IMEC-TNO [59]34                                                               |

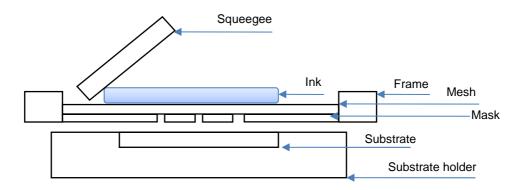

| Figure 2.5: Screen Printer Setup                                                                                                                                                  |

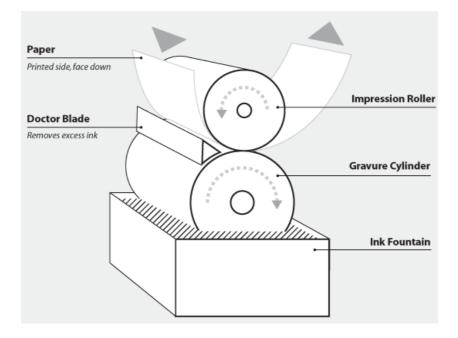

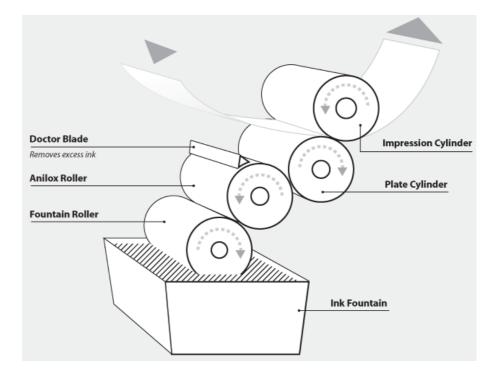

| Figure 2.6: Gravure printer setup. Image by Devon International [105].                                                                                                            |

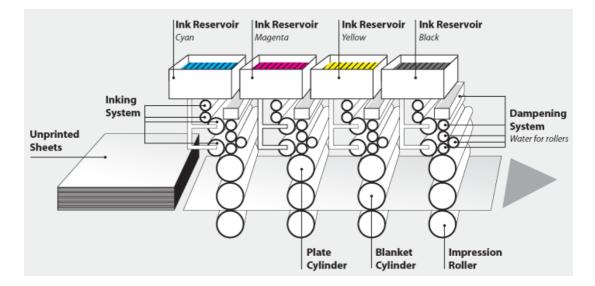

| Figure 2.7: Offset printer setup. Image by Devon International [105].                                                                                                             |

| Figure 2.8: Flexographic printer setup. Image by Devon International [105]                                                                                                        |

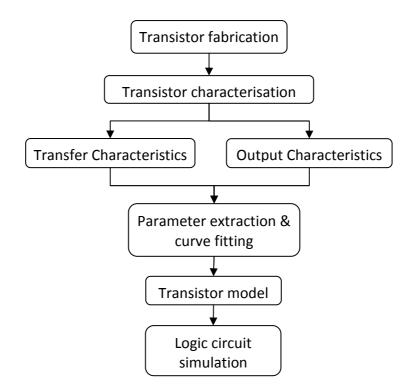

| Figure 2.9: Organic logic circuit design cycle                                                                                                                                    |

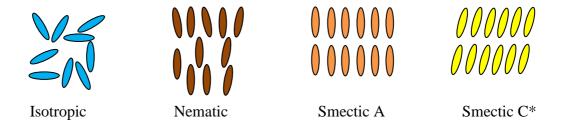

| Figure 3.1: Orientation of the liquid crystal molecules in various phases [129]63                                                                                                 |

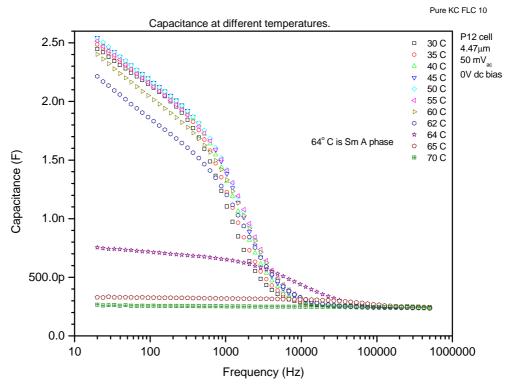

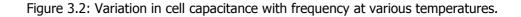

| Figure 3.2: Variation in cell capacitance with frequency at various temperatures                                                                                                  |

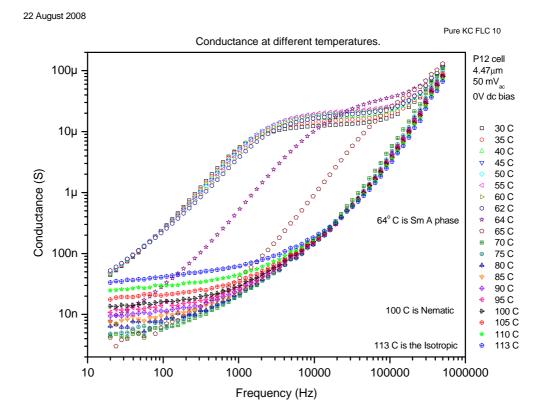

| Figure 3.3: Variation in cell conductance with frequency at various temperatures                                                                                                  |

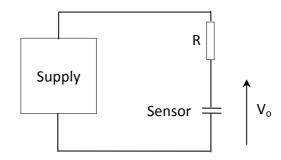

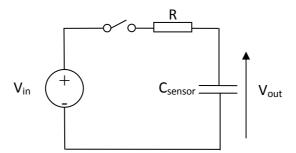

| Figure 3.4: RC time constant circuit setup for sensor characterisation                                                                                                            |

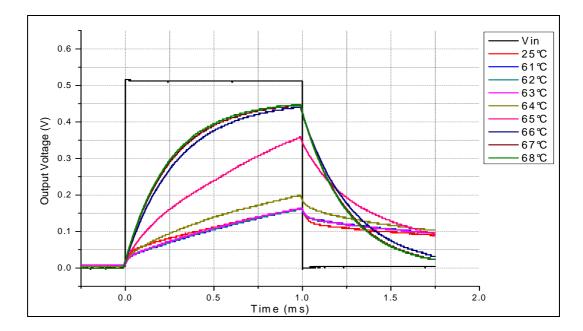

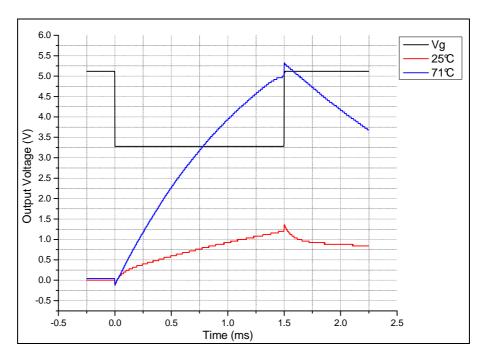

| Figure 3.5: Sensor response to a 0-500 mV, 1 ms pulse at different temperatures [128] 67                                                                                          |

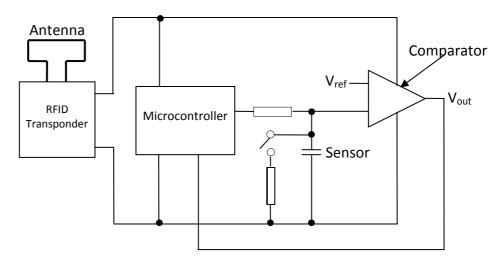

| Figure 3.6: Block diagram of the RFID Sensor tag. Figure adapted from [128]                                                                                                       |

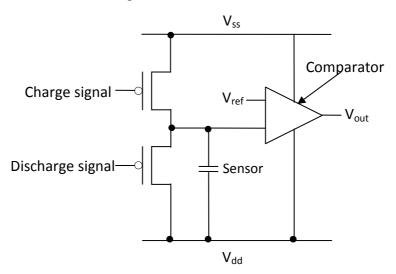

| Figure 3.7: Organic capacitance measurement circuit70                                                                                                                             |

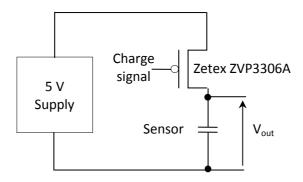

| Figure 3.8: Transistor based transient time circuit using Zetex P-type MOSFET71                                                                                                   |

| Figure 3.9: Voltage response of the sensor using the transient time circuit                                                                                                       |

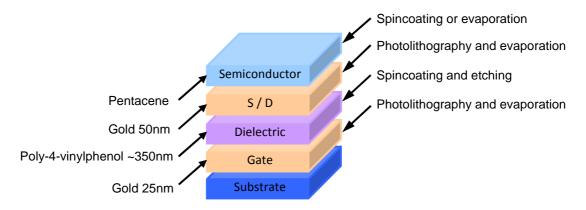

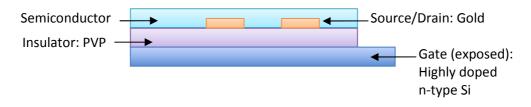

| Figure 3.10: Bottom gate bottom contact transistor structure for logic circuit fabrication 74                                                                                     |

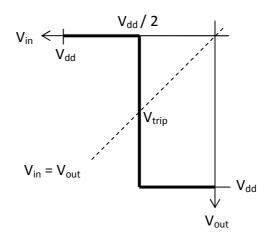

| Figure 3.11: Characteristics of an ideal inverter77                                                                                                                               |

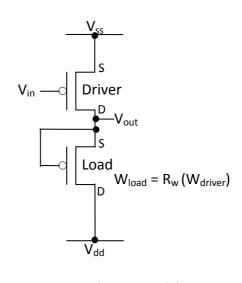

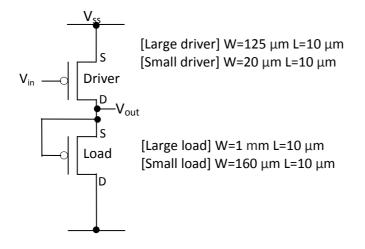

| Figure 3.12: Transistor configuration of the zero-V <sub>gs</sub> inverter [133]78                                                                                                |

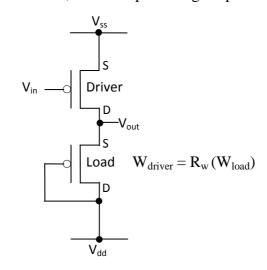

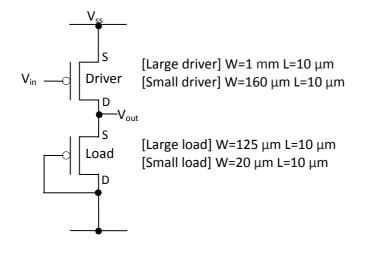

| Figure 3.13: Transistor configuration for the diode-load inverter [133].                                                                                                          |

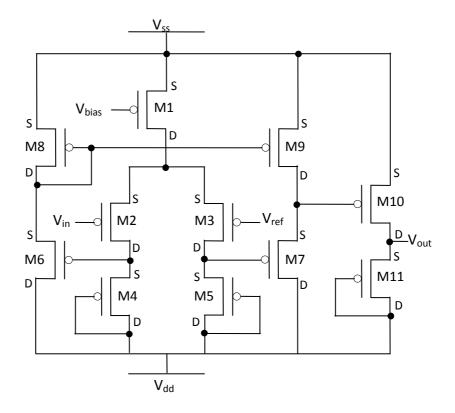

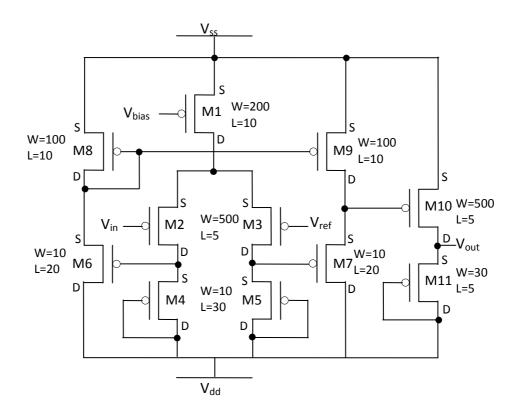

| Figure 3.14: P-channel organic comparator based on a single ended differential amplifier [73]81                                                                                   |

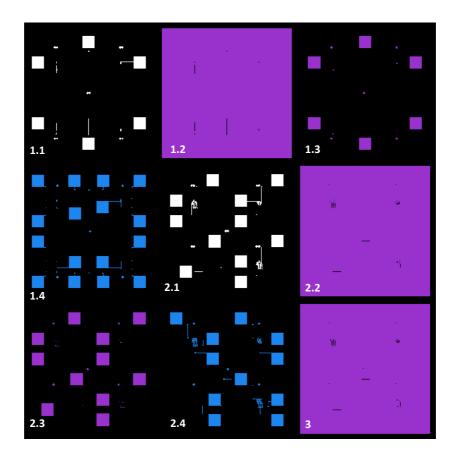

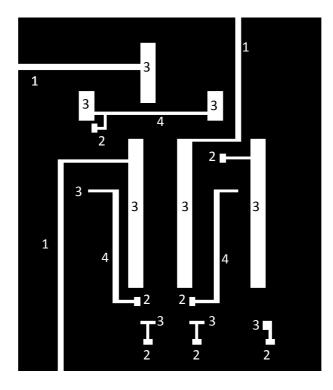

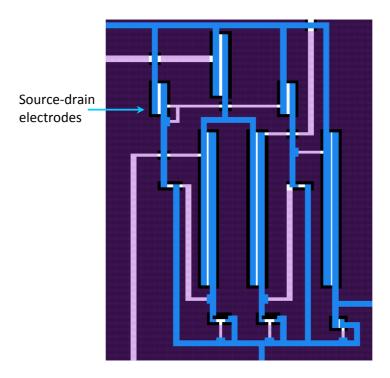

| Figure 3.15: Full photomask design consisting of the inverter and comparator patterns83                                                                                           |

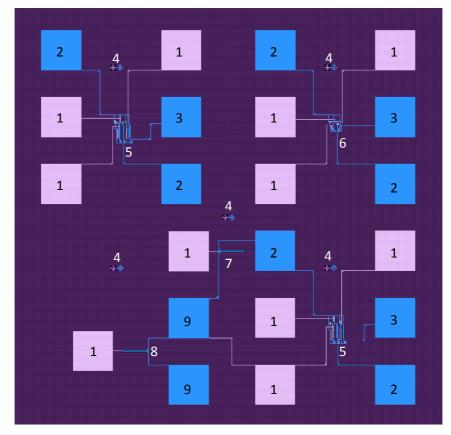

| Figure 3.16: Stacked layers of the inverter and single transistor mask                                                                                                            |

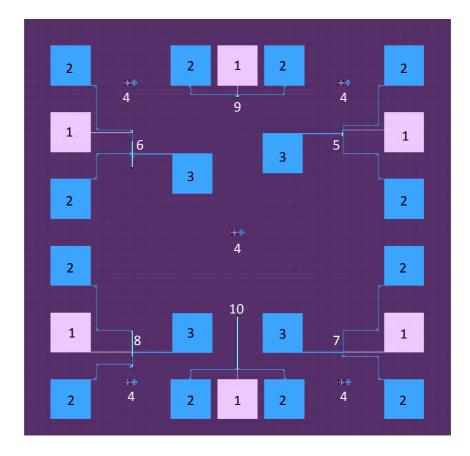

| Figure 3.17: Stacked layers of the comparator mask                                                                                                                                |

|                                                                                                                                                                                   |

| Figure 3.18:  | The actual photomask manufactured by Qudos.                                                                                                                                                                                     | 86  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.19:  | The gate layer patterns of the comparator circuit.                                                                                                                                                                              | 87  |

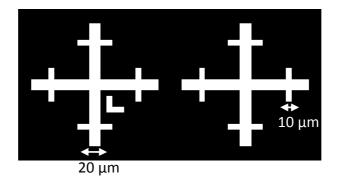

| Figure 3.20:  | Contact electrode overlap vias (left) and through hole vias (right)                                                                                                                                                             | 88  |

| -             | Alignment mark patterns for the gate layer. Mark for mesa layer (left) and ma for source/drain layer (right).                                                                                                                   |     |

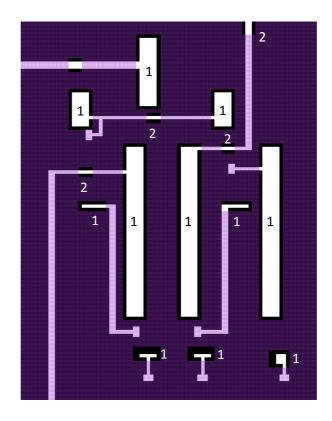

| Figure 3.22:  | Stacked gate and mesa patterns of the comparator circuit                                                                                                                                                                        | 89  |

| Figure 3.23:  | Stacked gate, mesa and source/drain patterns for the comparator circuit                                                                                                                                                         | 90  |

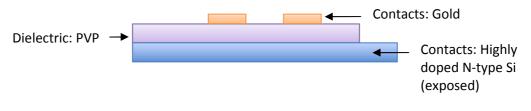

| Figure 4.1: S | Structure of the single transistor                                                                                                                                                                                              | 94  |

| Figure 4.2: S | Structure of the MIM capacitor.                                                                                                                                                                                                 | 95  |

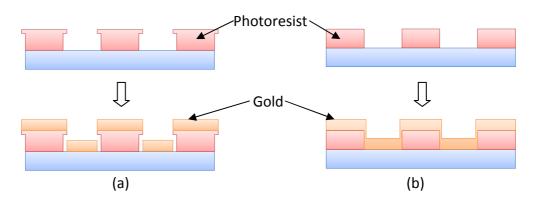

| -             | Resist and evaporated metal profile of developed films with chlorobenzene soa<br>(a) and without (b)                                                                                                                            |     |

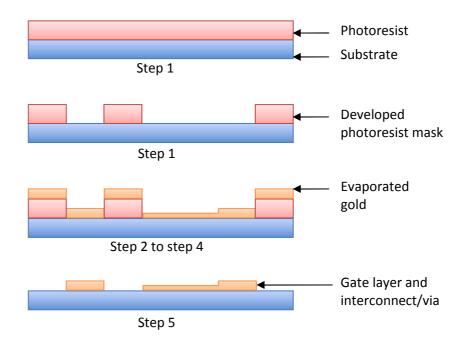

| Figure 4.4: P | Processing steps for gate layer deposition.                                                                                                                                                                                     | 97  |

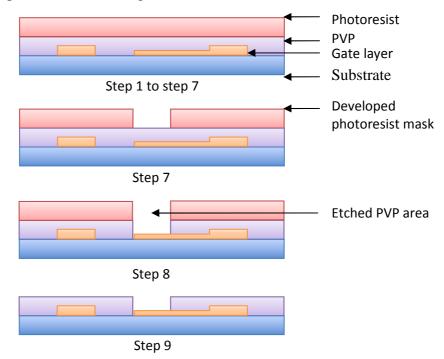

| Figure 4.5: P | Processing steps for dielectric layer deposition.                                                                                                                                                                               | 98  |

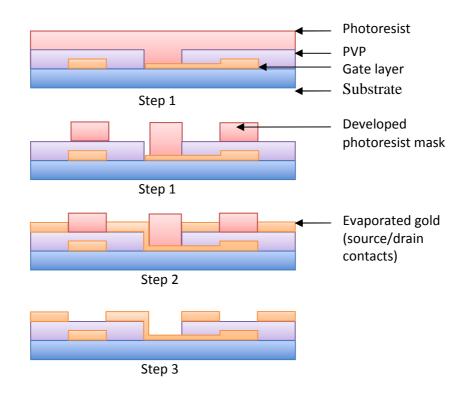

| Figure 4.6: P | Processing steps for source/drain layer deposition                                                                                                                                                                              | 99  |

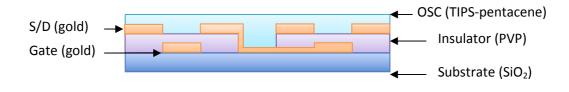

| Figure 4.7: S | Structure of a BGBC transistor1                                                                                                                                                                                                 | 100 |

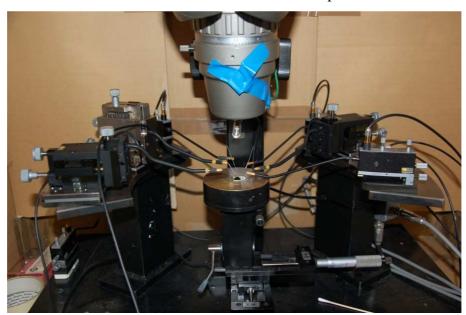

| Figure 4.8: P | Probe station with six micromanipulator probes1                                                                                                                                                                                 | 02  |

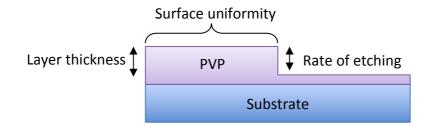

| Figure 5.1: I | nvestigated PVP characteristics1                                                                                                                                                                                                | L05 |

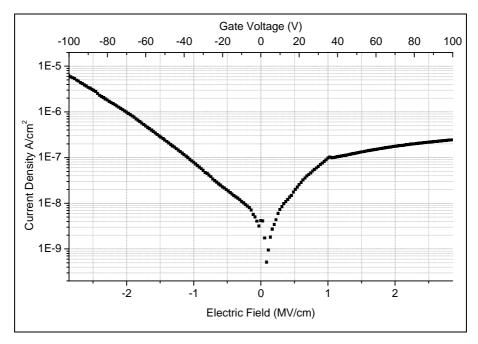

| Figure 5.2: L | eakage current through PVP dielectric layer1                                                                                                                                                                                    | 106 |

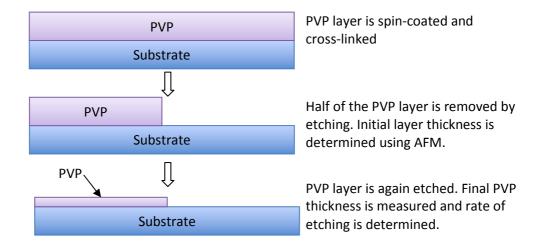

| Figure 5.3: F | abrication steps to determine the rate of oxygen plasma etching for PVP1                                                                                                                                                        | 108 |

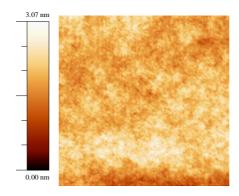

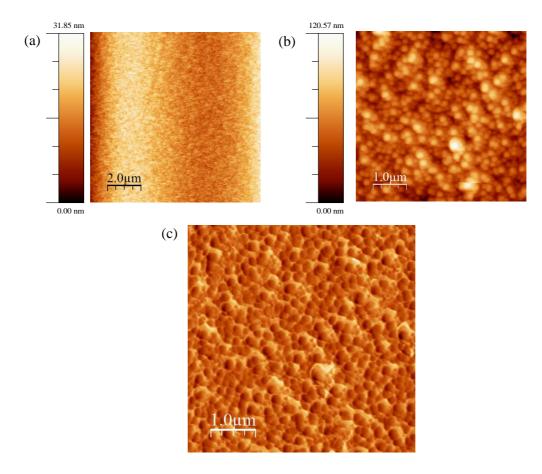

| Figure 5.4: A | AFM surface profile of unprocessed cross-linked PVP layer (5x5 $\mu$ m area) 1                                                                                                                                                  | 109 |

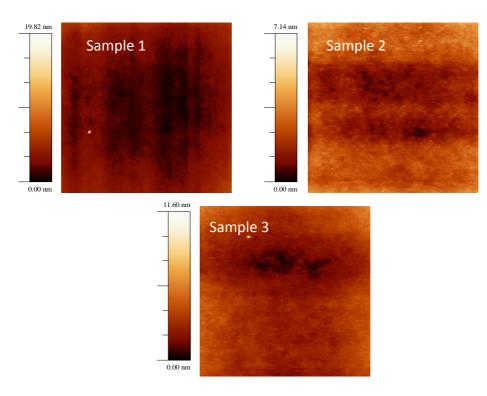

| -             | AFM surface profiles of three different cross-linked PVP samples after lift-off<br>photolithography processing (10x10 μm area)1                                                                                                 | 109 |

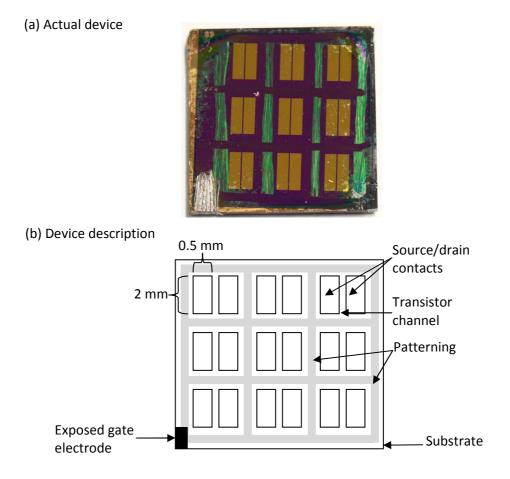

| Figure 5.6: P | VP + TIPS-pentacene single transistor sample1                                                                                                                                                                                   | 111 |

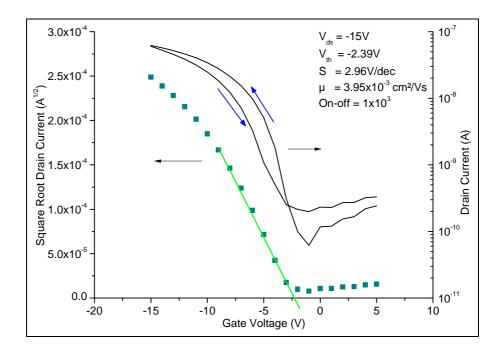

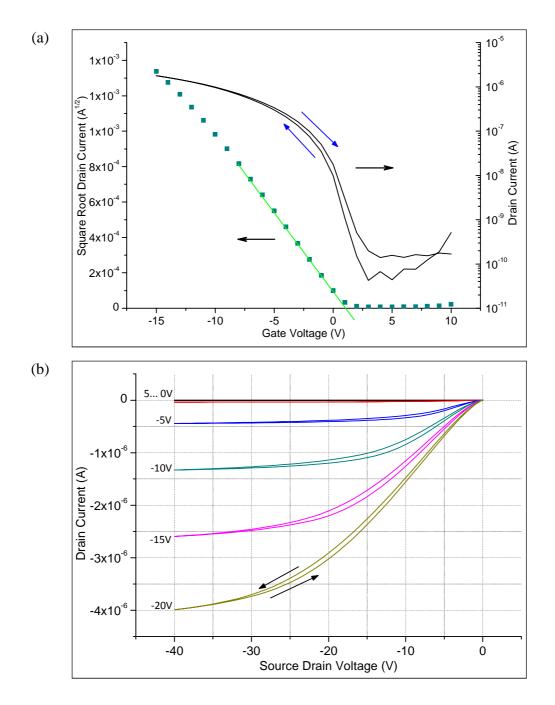

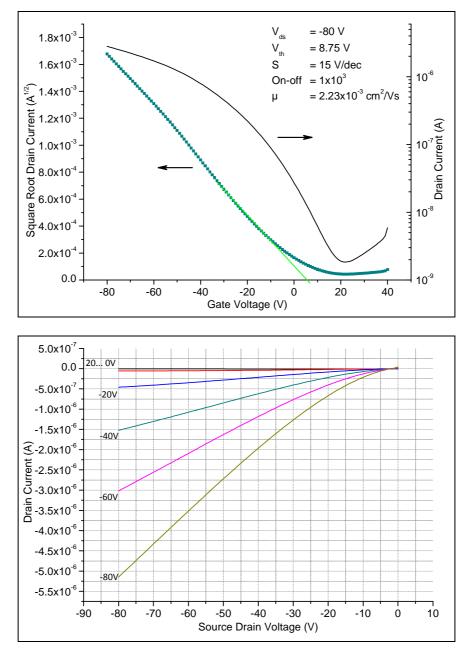

| p             | $_d$ -V <sub>g</sub> characteristics of a BGBC transistor with PVP dielectric and spin-coated TIF pentacene (1000 rpm). V <sub>ds</sub> =-15 V, W=2 mm and L=60 $\mu$ m. The square root curves from the forward voltage sweep1 | e   |

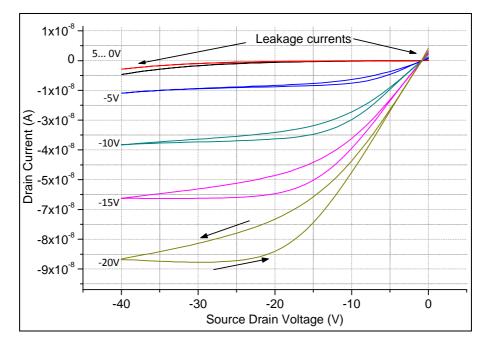

| -             | d-V <sub>ds</sub> characteristics of a BGBC transistor with PVP dielectric and spin-coated TIPS-pentacene (1000 rpm)                                                                                                            | 112 |

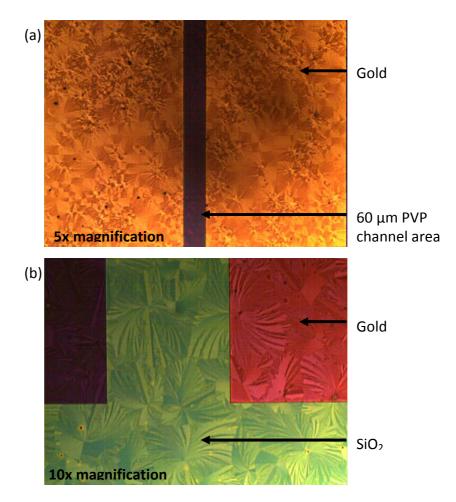

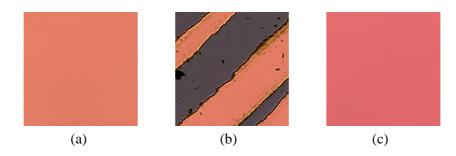

| -             | Grain growth of spin-coated TIPS-pentacene on (a) gold, PVP and (b) SiO $_2$ surface $1$                                                                                                                                        |     |

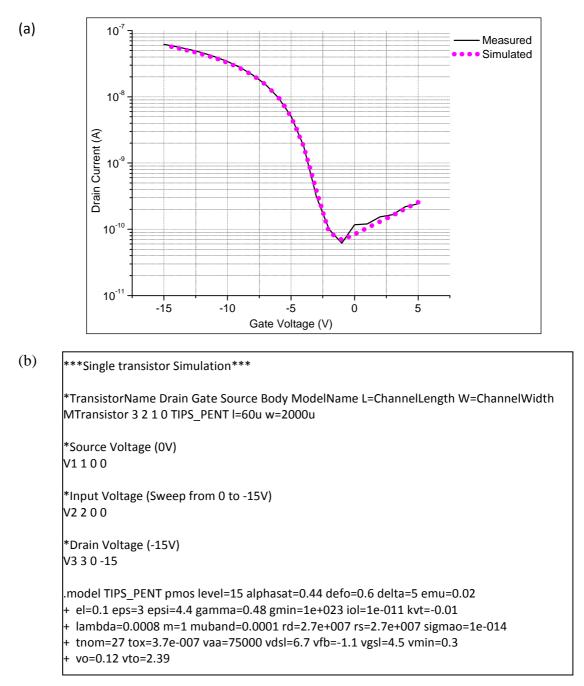

| -             | Simulated and measured $I_d$ - $V_g$ characteristics of the single transistor (a). The AIM-Spice code used for simulation (b)1                                                                                                  | 16  |

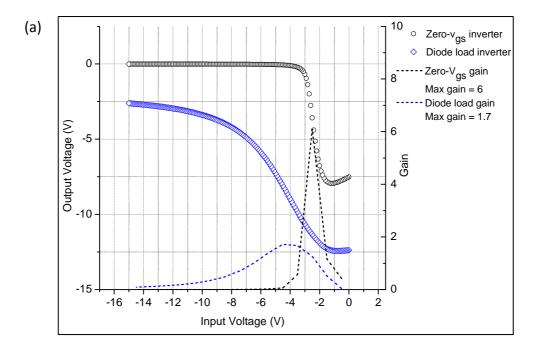

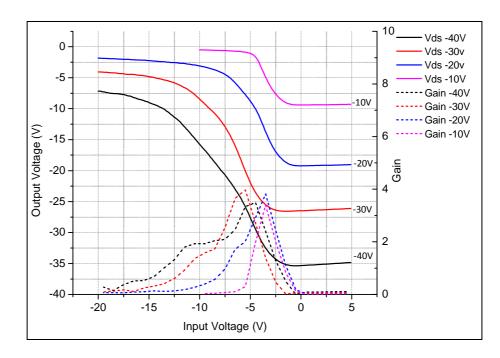

| -             | Simulated inverter characteristics for the zero- $V_{gs}$ and diode load configuratio (a). The AIM-Spice code used for the simulation of the zero- $V_{gs}$ (b) and diode load (c) inverters                                    |     |

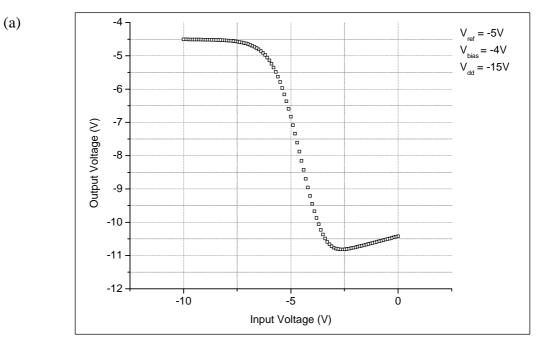

|               | Simulated comparator characteristics (a). The AIM-Spice code used for the simulation (b)                                                                                                                                        | 19  |

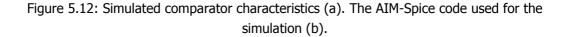

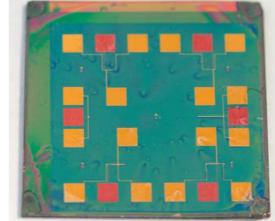

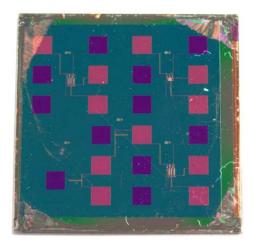

| Figure 5.13:  | Inverter circuit fabricated using the BGBC logic circuit process1                                                                                                                                                               | 122 |

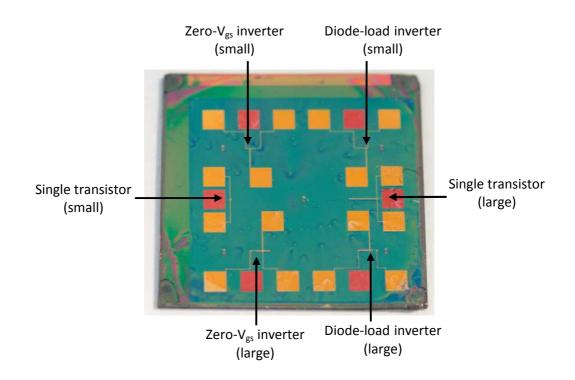

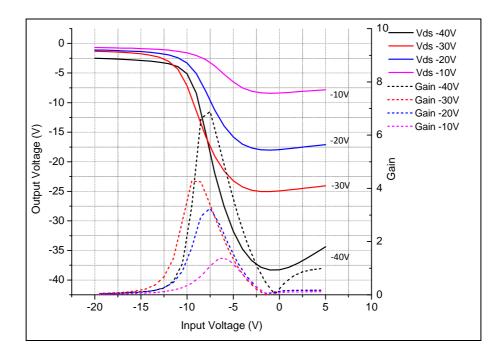

| Figure 5.14: $V_o$ - $V_{in}$ characteristics of two zero- $V_{gs}$ inverters. $V_{ds}$ = -40 V. Driver transistor,<br>W=125 $\mu$ m L=10 $\mu$ m. Load transistor, W =1 mm L=10 $\mu$ m                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

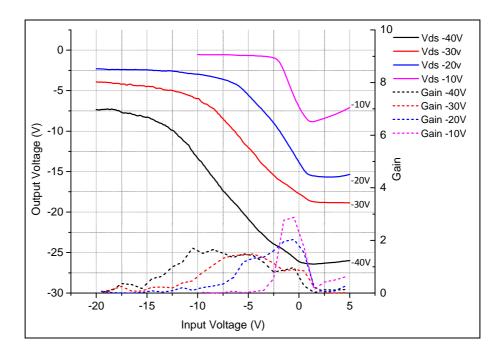

| Figure 5.15: V <sub>o</sub> -V <sub>in</sub> characteristics of the large diode-load inverter. Driver transistor, W=1 mm L=10 $\mu$ m. Load transistor, W=125 $\mu$ m L=10 $\mu$ m                                                  |

| Figure 5.16: V <sub>o</sub> -V <sub>in</sub> characteristics of the small diode-load inverter. Driver transistor, W=160 $\mu$ m L=10 $\mu$ m. Load transistor, W=20 $\mu$ m L=10 $\mu$ m                                            |

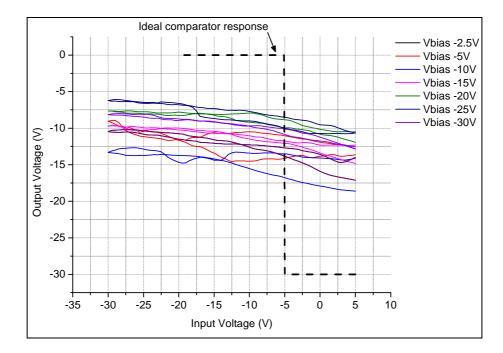

| Figure 5.17: An example voltage response of the comparator circuit                                                                                                                                                                  |

| Figure 5.18: Incomplete photoresist lift-off during the deposition of the source/drain contact electrodes                                                                                                                           |

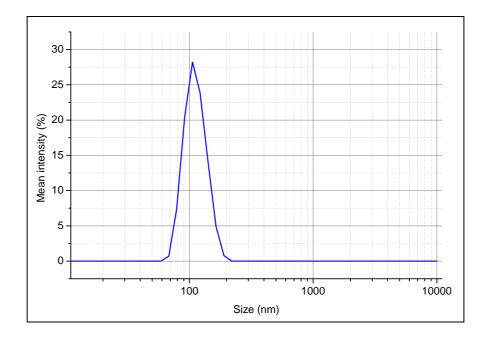

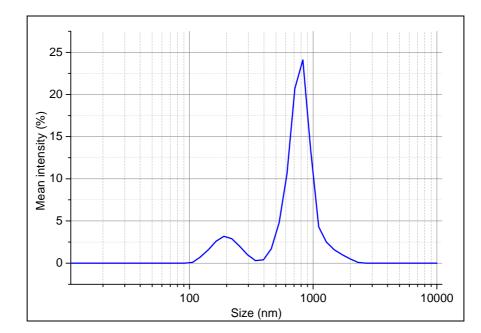

| Figure 6.1: Size distribution of the suspended BST nanoparticles after completing the synthesis reaction (step 11). Sample is taken from the top portion of the synthesis mixture directly from the autoclave vessel. Peak = 113 nm |

| Figure 6.2: Size distribution of the BST nanoparticles taken during the final cycle of the cleaning procedure. Peak 1 = 202 nm, Peak 2 = 824 nm                                                                                     |

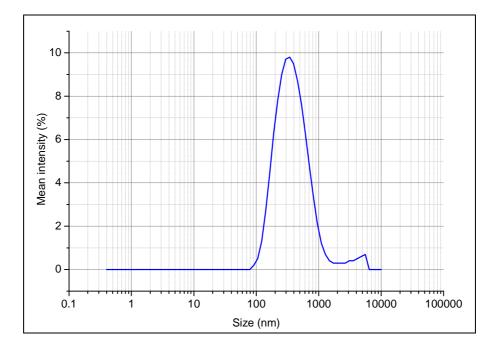

| Figure 6.3: Size distribution of BST nanoparticles obtained from Sigma-Aldrich. Peak = 334nm                                                                                                                                        |

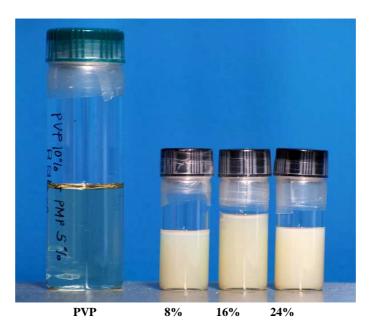

| Figure 6.4: PVP-BST nanocomposite solution with 8, 16 and 24 wt% nanoparticle loading. 142                                                                                                                                          |

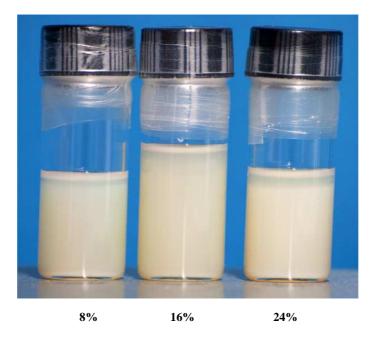

| Figure 6.5: PVP-BST nanocomposite solution with 8, 16 and 24 wt% nanoparticle loading that have been stored in upright position after two weeks                                                                                     |

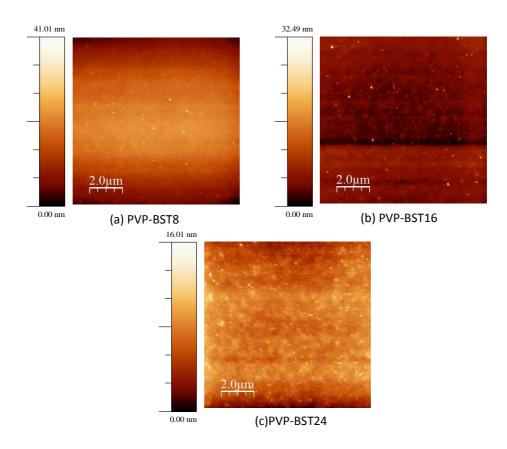

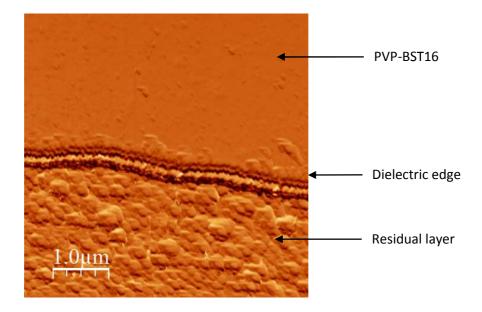

| Figure 6.6: AFM surface scan of PVP-BST films144                                                                                                                                                                                    |

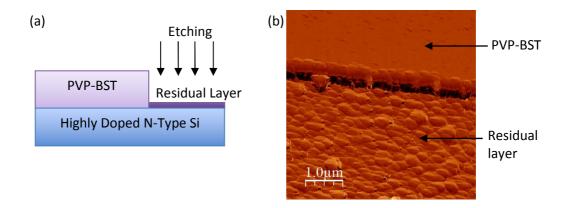

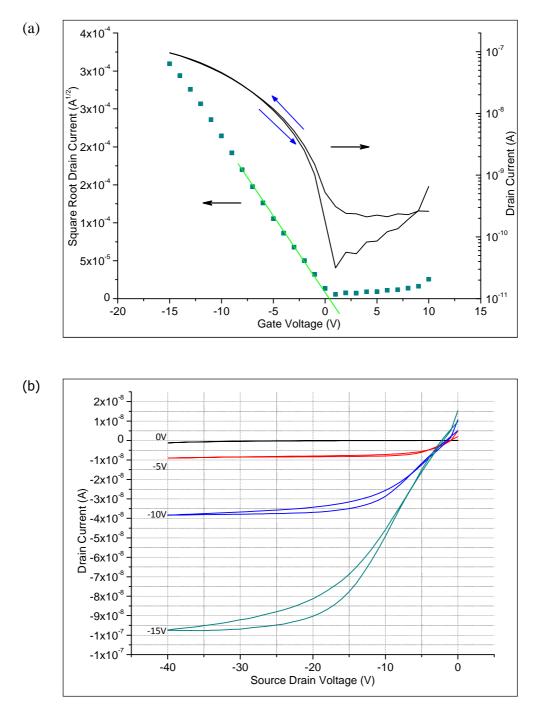

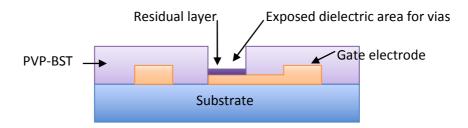

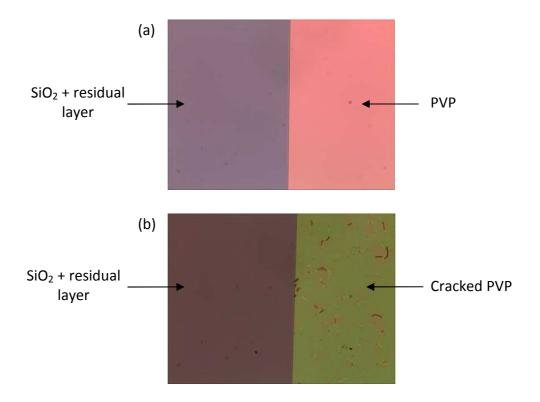

| Figure 6.7: Residual layer formed by the oxygen plasma etch of PVP-BST (a). Phase image of the residual layer on $SiO_2$ (b)146                                                                                                     |

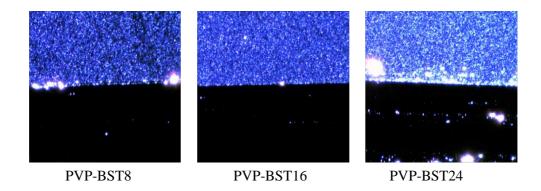

| Figure 6.8: Dark field illumination of the PVP-BST residual layer for 8-24 wt% nanoparticle loading                                                                                                                                 |

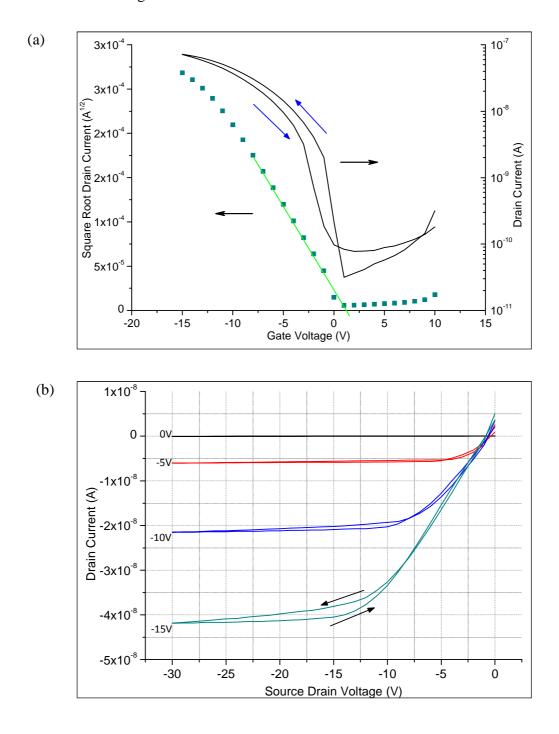

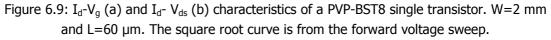

| Figure 6.9: $I_d$ - $V_g$ (a) and $I_d$ - $V_{ds}$ (b) characteristics of a PVP-BST8 single transistor. W=2 mm and L=60 $\mu$ m. The square root curve is from the forward voltage sweep150                                         |

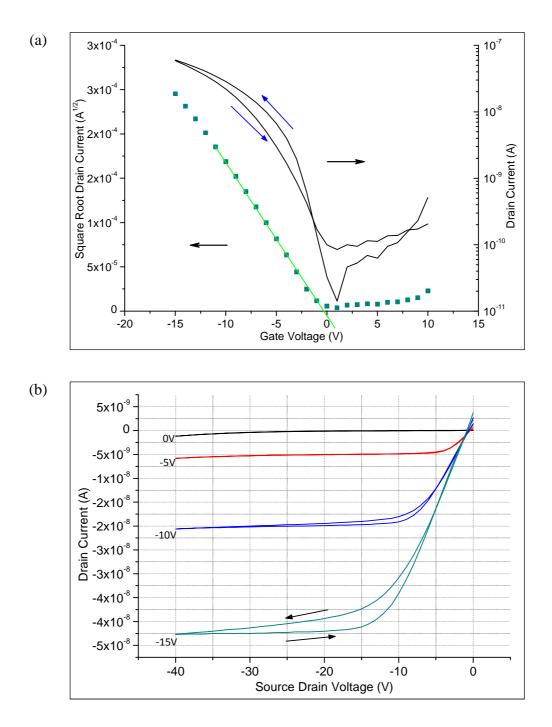

| Figure 6.10: $I_d$ - $V_g$ (a) and $I_d$ - $V_{ds}$ (b) characteristics of a PVP-BST16 single transistor. W=2 mm and L=60 $\mu$ m. The square root curve is from the forward voltage sweep151                                       |

| Figure 6.11: $I_d$ - $V_g$ (a) and $I_d$ - $V_{ds}$ (b) characteristics of a PVP-BST24 single transistor. W=2 mm and L=60 $\mu$ m. The square root curve is from the forward voltage sweep152                                       |

| Figure 6.12: Formation of the residual layer on the gate electrode interconnect area154                                                                                                                                             |

| Figure 6.13: AFM phase image of the etched PVP-BST area when using the sacrificial layer.                                                                                                                                           |

| Figure 6.14: Before (a) and after (b) images of a PVP sample rinsed in aqua regia for 2<br>minutes                                                                                                                                  |

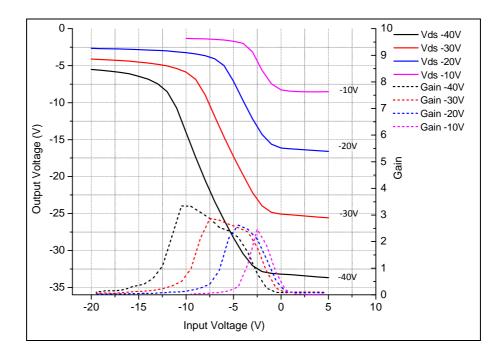

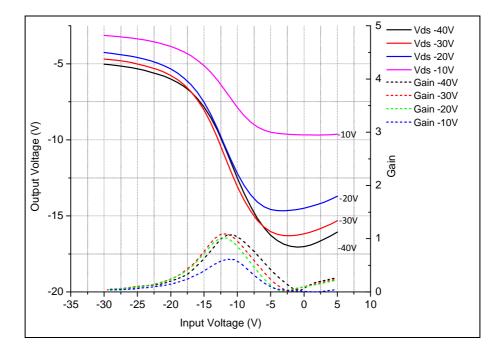

| Figure 6.15: $V_o$ - $V_{in}$ characteristics of a large zero- $V_{gs}$ inverter using PVP-BST16 dielectric for $V_{ds}$ -10 to -40 V. Driver transistor, W=125 $\mu$ m L=10 $\mu$ m. Load transistor, W=1 mm L=10 $\mu$ m          |

| Figure 6.16: $V_o$ - $V_{in}$ characteristics of a small zero- $V_{gs}$ inverter using PVP-BST16 dielectric for $V_{ds}$ -10 to -40 V. Driver transistor, W=20 $\mu$ m L=10 $\mu$ m. Load transistor, W=160 $\mu$ m L=10 $\mu$ m    |

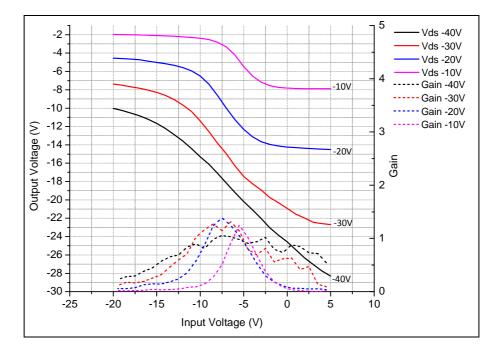

| for             | V <sub>in</sub> characteristics of a large diode-load inverter using PVP-BST16 dielectric<br>V <sub>ds</sub> -10 to -40 V. Driver transistor, W=1 mm L=10 μm. Load transistor, W=1<br>L=10 μm      |     |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| for             | V <sub>in</sub> characteristics of a small diode-load inverter using PVP-BST16 dielectric<br>V <sub>ds</sub> -10 to -40 V. Driver transistor, W=160 μm L=10 μm. Load transistor, W=<br>L=10 μm1    | 20  |

| -               | M image of the surface of gold (a) and etched PVP-BST (b) on gold. Phase<br>age of etched PVP-BST on gold (c)1                                                                                     | .60 |

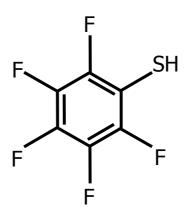

| Figure 6.20: Ch | emical structure of PFBT. Image adapted from Sigma-Aldrich [171]1                                                                                                                                  | 65  |

| -               | $\prime_{\rm g}$ (a) and $I_d\text{-}V_{ds}$ (b) characteristics of a transistor treated with PFBT. Channel gth 60 $\mu m$ , channel width 2 mm                                                    |     |

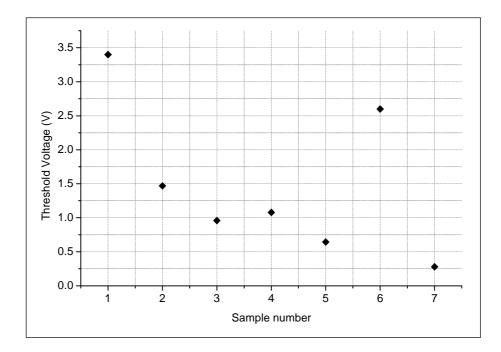

| Figure 6.22: Th | reshold voltage values for 7 transistors treated with PFBT1                                                                                                                                        | .68 |

|                 |                                                                                                                                                                                                    |     |

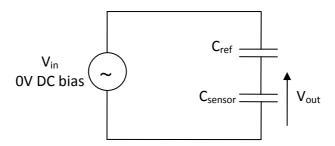

|                 | AC excitation of capacitive divider1                                                                                                                                                               |     |

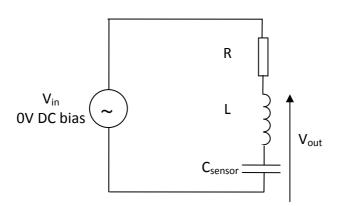

|                 | : Tuner circuit with capacitance and inductance in series1                                                                                                                                         |     |

|                 | RC circuit configuration1                                                                                                                                                                          |     |

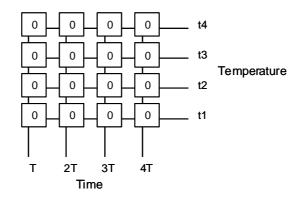

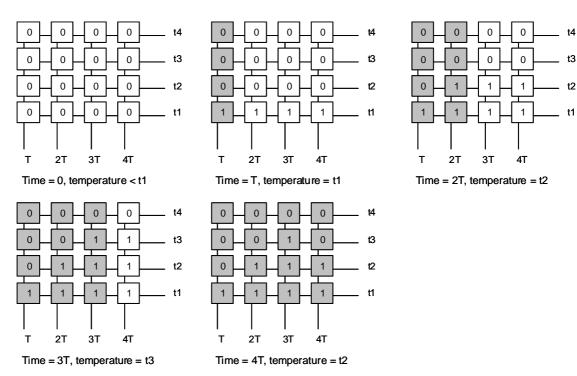

| Figure_Apx B.1  | Sensor array1                                                                                                                                                                                      | 89  |

| Figure_Apx B.2  | Gradual polymerisation of sensor array.                                                                                                                                                            | 89  |

| Figure_Apx C.1  | : Transfer and output characteristics of a transistor using PBTTT<br>semiconductor, highly doped n-type Si substrate and 650 nm of PVP<br>dielectric layer1                                        | .90 |

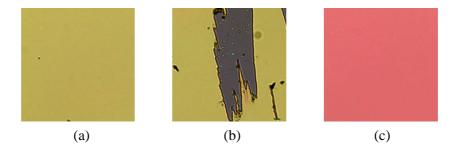

| Figure_Apx F.1: | Etched PVP samples using highly doped n-type Si substrates for dielectric thickness measurement                                                                                                    | .97 |

| Figure_Apx F.2: | MIM capacitor using gold contact electrodes for capacitance and gate leakage measurements                                                                                                          | .97 |

| Figure_Apx F.3: | Single transistors using PVP and spin-coated TIPS-pentacene on highly dop n-type Si substrates1                                                                                                    |     |

| Figure_Apx F.4: | Inverter circuit using PVP and spin-coated TIPS-pentacene on Si-SiO <sub>2</sub> substrates1                                                                                                       | .98 |

| Figure_Apx F.5: | Inverter circuit using PVP and drop casted TIPS-pentacene on Si-SiO <sub>2</sub> substrates1                                                                                                       | .98 |

| Figure_Apx F.6: | Comparator circuit using PVP and spin-coated TIPS-pentacene on Si-SiO <sub>2</sub> substrate1                                                                                                      | .98 |

| Figure_Apx F.7: | The first functional organic inverter in UoM EEE fabricated on $Si-SiO_2$ substrates. PTAA is used as the active layer and (conductive) epoxy bonded wires were employed for forming interconnects |     |

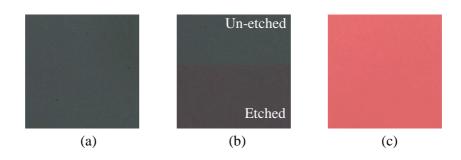

| Figure_Apx G.1  | : Microscope images of PVP film cross-linked with HMBG at 130°C for 3 hou<br>Sample after acetone rinse (a). Sample etched using oxygen plasma (b).<br>Reference sample (c)2                       |     |

| 0                 | Microscope images of PVP film crosslinked with HMBG at 150°C for 3 hou<br>Sample after acetone rinse (a). Sample scratched using cocktail stick (b). |      |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                   | Reference sample (c).                                                                                                                                | 201  |

|                   | Microscope images of PVP film crosslinked with HMBG at 150°C for 6 hou<br>Sample after acetone rinse (a). Sample scratched using cocktail stick (b). | ırs. |

|                   | Reference sample (c)                                                                                                                                 | 201  |

| Figure_Apx I.1: Z | ero-V <sub>gs</sub> inverter                                                                                                                         | 204  |

| Figure_Apx I.2: D | Diode-load inverter                                                                                                                                  | 204  |

| Figure_Apx I.3: C | Comparator circuit. Length unit is in micrometers                                                                                                    | 205  |

#### List of Tables

| Table 2.1: Laboratory based fabrication techniques reported from 2000 to 2003                                                    |

|----------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2: Laboratory based fabrication techniques reported from 2004 to 200737                                                  |

| Table 2.3: Laboratory based fabrication techniques reported from 2007 to 2008                                                    |

| Table 2.4: Laboratory based fabrication techniques reported from 2010 to 2011                                                    |

| Table 2.5: Printing based fabrication techniques reported from 1994 to 200447                                                    |

| Table 2.6: Printing based fabrication techniques reported from 1997 to 201048                                                    |

| Table 2.7: Characteristics of various printing technologies. Table adapted from [62]49                                           |

| Table 3.1: Description of the full photomask patterns.    83                                                                     |

| Table 3.2: Description of the inverter and single transistor photomask patterns.         84                                      |

| Table 3.3: Description of the comparator photomask patterns.         85                                                          |

| Table 3.4: Description of the gate layer patterns.    87                                                                         |

| Table 3.5: Description of the mesa layer photomask patterns. Marked areas are protected by<br>the photoresist during etching     |

| Table 5.1: Dielectric constant of cross-linked PVP107                                                                            |

| Table 5.2: Etching rate of cross-linked PVP.         108                                                                         |

| Table 5.3: Cross-linked PVP roughness data prior to and after lift-off photolithography         processing.         110          |

| Table 6.1: Comparison of the dielectric constant of PVP and PVP-BST dielectric                                                   |

| Table 6.2: Dielectric constant values calculated using series, parallel and logarithmic mixingequations.149                      |

| Table 6.3: Performance matrices of PVP-BST transistors for 8 to 24 wt% loading. Mean valuescalculated from four measured devices |

| Table 6.4: Gain of inverters fabricated using PVP-BST16.       157                                                               |

| Table 6.5: Performance metrics of the transistor treated with PFBT. Mean values are over 7         devices.         166          |

#### Abbreviations and Symbols

| μ                  | Mobility or micron                                         |

|--------------------|------------------------------------------------------------|

| Å                  | Angstrom $(1 \times 10^{-10} \text{ m})$                   |

| 0                  | Degrees                                                    |

| $\pi$ bond         | Pi bond                                                    |

| $\sigma$ bond      | Sigma bond                                                 |

| $\Phi_{\rm w}$     | Work function                                              |

| a:Si:H             | Hydrogenated amorphous silicon                             |

| ADS                | Agilent Technologies - Advanced Design System              |

| AFG                | Arbitrary Function Generator                               |

| AFM                | Atomic force microscopy                                    |

| Al                 | Aluminium                                                  |

| $Al_2O_3$          | Aluminium oxide                                            |

| ALD                | Atomic layer deposition                                    |

| Au                 | Aurum / Gold                                               |

| BaTiO <sub>3</sub> | Barium titanate, Barium titanium oxide                     |

| BC                 | Bottom contact                                             |

| BG                 | Bottom gate                                                |

| BGBC               | Bottom gate bottom contact                                 |

| BGTC               | Bottom gate top contact                                    |

| BST                | Barium strontium titanium oxide, barium strontium titanate |

| DCB                | Dichlorobenzene                                            |

| DLS                | Dynamic light scattering                                   |

| DPVAnt             | Di(phenylvinyl)anthracene                                  |

| EEE                | School of electrical and electronic engineering            |

| F8T2               | Poly(9,9-dioctylfluorene-co-bithiophene)                   |

| FLC                | Ferroelectric liquid crystal                               |

| GDSII              | Graphic Database Stream II                                 |

| HMBG        | Hydroxymethyl benzoguanamine                                                                                                                                          |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| НОМО        | Highest occupied molecular orbital                                                                                                                                    |

| Hz          | Hertz                                                                                                                                                                 |

| ICCAP       | Agilent Technologies - Integrated Circuit Characterization and Analysis Program                                                                                       |

| IDE         | Interdigitated electrodes                                                                                                                                             |

| IGZO        | Indium gallium zinc oxide                                                                                                                                             |

| LUMO        | Lowest unoccupied molecular orbital                                                                                                                                   |

| MIM         | Metal insulator metal                                                                                                                                                 |

| MOSFET      | Metal oxide semiconductor field effect transistor                                                                                                                     |

| nm          | Nanometers                                                                                                                                                            |

| ODT         | Octadecanethiol                                                                                                                                                       |

| OFET(s)     | Organic field effect transistor                                                                                                                                       |

| ОН          | Hydroxyl                                                                                                                                                              |

| OTS         | Octadecyltrichlorosilane                                                                                                                                              |

| PAG         | Photoacid generator                                                                                                                                                   |

| PANI        | Polyaniline                                                                                                                                                           |

| PBTTT       | Poly(2,5-bis(3-alkylthiophen-2-yl)thieno[3, 2-b]thiophene                                                                                                             |

| PDHTT       | Poly(3,3 -dihexyl-2,2:5 ,2-terthiophene)                                                                                                                              |

| PDRA        | Post doctoral research associate                                                                                                                                      |

| PEDOT:PSS   | Poly(3,4-ethylenedioxythiophene) poly(styrenesulfonate)                                                                                                               |

| PEN         | Polyethylene naphthalate                                                                                                                                              |